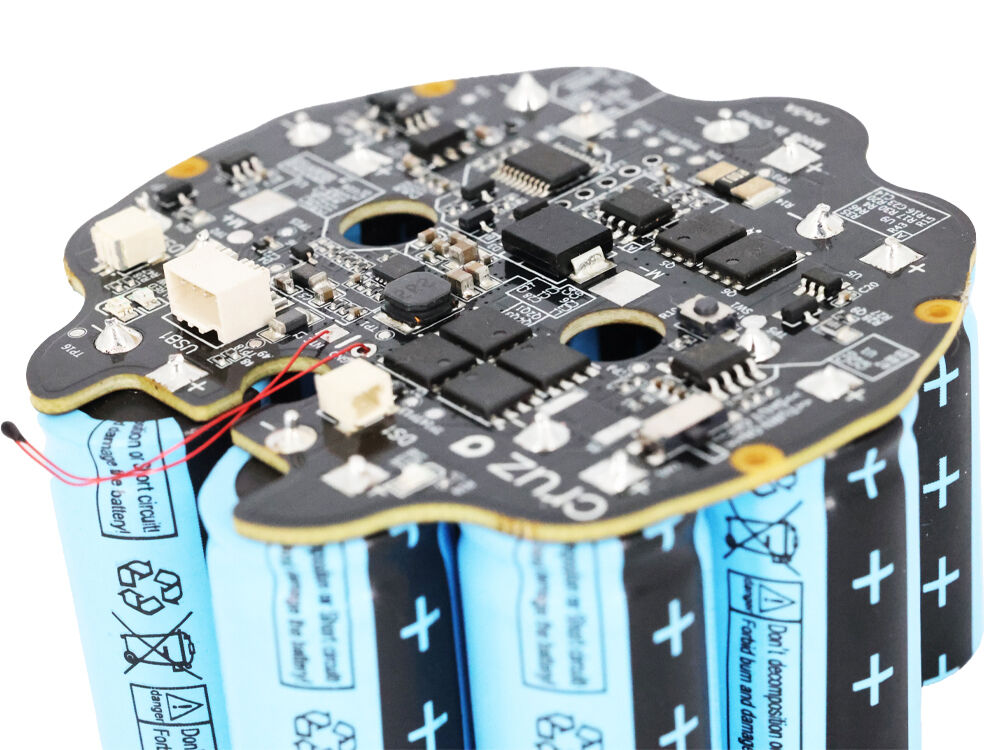

プリント回路基板(PCB)は、民生用ガジェットから安全性が極めて重要な医療機器、自律走行車両に至るまで、現代の電子機器の要です。しかし、その普及の度合いや、今日のPCB製造プロセスの高度さにもかかわらず、 PCB生産の遅延 は非常に頻繁に発生する障害です。このような遅延は時間的コストにとどまらず、製品の市場投入計画を頓挫させたり、予算を膨張させたり、さらには製品全体の信頼性を損なう可能性さえあります。

激しい競争が繰り広げられる技術市場において、迅速かつ欠陥のないPCBの製作およびアセンブリを確実にすることは極めて重要です。そして、ほぼすべての根本原因分析において、重大な遅れの主因は次の2つの要因に集約されます。 DFM(製造性設計)のミス と DFA(組立性設計)のミス pCB設計のガイドラインやベストプラクティスに関するリソースは豊富にあるにもかかわらず、経験豊富なエンジニアでさえも繰り返し発生する特定の落とし穴が存在します。これらのミスは一見単純に見えることがありますが、その影響は深刻であり、設計の再作業(リスピン)の増加、歩留まりのリスク、サプライチェーン全体に波及するボトルネックを引き起こします。

本記事では以下の内容を詳しく解説します。

迅速なプロトタイプから量産への移行を目指すハードウェアスタートアップ企業であれ、アセンブリ歩留まりの向上を目指す既存のエンジニアリングチームであれ、 製造設計(DFM) と 組立性設計(DFA) が、効率化への最短ルートです。

製造設計(DFM)は、信頼性が高くコスト効率に優れたPCB製造の基盤です。しかし、最先端のファブであっても、繰り返し発生する DFMミス の主な原因となっています。 PCB生産の遅延 これらの設計上の誤りはCAD画面上では些細に見えるかもしれませんが、工場現場では高価なボトルネックや廃棄、再設計につながる可能性があります。当社の製造専門家が、最も頻発する落とし穴と、より重要なことにそれらを回避する方法をまとめました。

バランスが取れていないまたは不十分な仕様のPCB積層構造は、特に多層基板において災難への道を開くものです。次のような問題が原因で 誘電体の厚みに関する詳細情報の欠如 、規定されていない 銅の厚さ , 非対称レイアウト 、インピーダンス制御の欠如、およびめっきや半田レジストの厚さに関するあいまいな指示は、しばしば以下のような結果を招きます。

PCBスタックアップ設計のベストプラクティス:

|

ステップ |

説明 |

参照 |

|

各層を明確に指定する |

すべての層について、銅の重量、誘電体の厚さおよび種類を定義する |

IPC-2221、IPC-4101 |

|

対称性を維持する |

中心のコアに対して上下でスタックアップを鏡像にする—機械的応力を低減 |

|

|

すべての処理を含める |

全体の厚さにめっき、はんだレジスト、表面処理を考慮に入れる |

IPC-4552 |

|

インピーダンス層のドキュメント |

インピーダンス制御ネットには明示的な注記を使用 |

IPC-2141, 2221 |

|

積層構成の呼び出し情報をアーカイブ |

過去のリビジョンと変更履歴を容易に参照可能にしておく |

|

配線設計は単純に思えるが 配線幅および間隔違反 はDFMミスの中で最も一般的なものの一つである。頻繁に発生するエラーには以下がある:

トレース設計チェックリスト:

表:一般的なトレース配線の落とし穴とその防止策

|

DFMエラー |

影響 |

ソリューション |

|

エッジにトレースが近すぎます |

ルーターによる銅箔の露出、短絡のリスク |

基板エッジから20ミル以上離す(製造ガイドライン) |

|

ビア/パッドにティアドロップがありません |

亀裂発生の可能性、歩留まり低下 |

信頼性向上のためティアドロップを追加 |

|

差動ペアの間隔が不均一 |

SI(信号完全性)の問題発生 |

間隔の一致を明確に指定 |

|

IPC-2152に基づく Clearance が確保されていません |

エッチング/ショート/不良なテスト歩留まり |

IPC-2152に従って間隔を広げる |

ビアは現代の多層PCBにとって不可欠ですが、不適切な設計選択は重要なDFM上の課題を引き起こします。

製造性を考慮したビア設計ルール:

ソルダーマスク層 の問題は、直前の段階での生産遅延や組立ミスの典型的な原因です。

離れる 表面仕上げ 未定義、互換性のないオプションを選択、または手順を指定しないことが生産を完全に停止させる可能性があります。同様に、あいまいまたは欠落している 機械の特徴 文書内容は、Vスコア、ブレイクアウェイノッチ、または機械加工スロットの適切な実装を妨げる可能性があります。

完成品データの不備や不一致は、驚くほどよく見られます。一般的なDFMミスには以下が含まれます:

PCB製造ノートのベストプラクティス:

PCB生産の遅延を引き起こす原因の一つとして、しばしば過小評価されているのは、 不完全または矛盾のある生産ファイルの提出 です。完璧な回路図やスタックアップを持っていても、文書化における些細な見落としがCAMエンジニアリング段階でボトルネックを生じ、注文が停止してしまうことがあります。たとえば Gerberとドリルデータの不一致 , 製造ノートの曖昧さ , 見落とされたリビジョン 、および重要なフォーマット(例:IPC-D-356Aネットリスト、ODB++、またはIPC-2581)の欠如は、時間のかかる確認作業や再作業を余儀なくさせます。

生産ファイルにおける一般的なDFMエラー:

PCB生産ドキュメント作成のベストプラクティス:

|

ステップ |

アクション |

参照 |

|

すべてのエクスポートをクロスチェックする |

Gerber、NCドリル、ファブ図面をビューアー(GC-Prevue、Altiumなど)で開く |

内部品質保証 |

|

一貫した命名規則とリビジョン管理を使用する |

生産ファイルを標準化された日付付きフォルダーにまとめること |

自動バージョン管理 |

|

必要なすべてのフォーマットを含める |

最低限必要なもの:Gerber RS-274X、NCドリル、ファブおよびアセンブリ図面、スタックアップ、BOM、ピックアンドプレース、ネットリスト(IPC-D-356AまたはODB++/IPC-2581) |

IPC準拠のフォーマット |

|

明確なファブノートを提供する |

文書の仕上げタイプ、インピーダンス詳細、機械的制約および試験要件 |

IPC-2221、IPC-D-356A、製造業者の対応能力 |

|

改訂履歴を添付する |

文書に簡単な変更履歴または改訂テーブルを含める |

ISO 9001:2015 文書 |

|

データが設計意図と一致していることを確認 |

実際のPCB CAD出力が元の設計(極性および方向を含む)と一致していることを検証 |

リリース前の設計者による承認 |

表:必須PCB文書チェックリスト

|

ファイル/文書 |

必須ですか? |

確認が必要な主な詳細 |

|

Gerber RS-274X |

はい |

ファブノートと一致、アーカイブ可能/リビジョン管理済み |

|

NCドリル |

はい |

ドリルサイズがパッド/ビアのスタックアップと一致 |

|

爆 |

はい |

最新の部品番号、サプライヤー、ライフサイクル情報 |

|

ピックアンドプレース |

はい |

実装座標、リファレンスデス、回転角度 |

|

製造図面 |

はい |

ネット名、スタックアップ、寸法、表面処理 |

|

IPC-D-356A / ODB++ |

強く |

電気テストおよびクロスチェック用 |

|

機械層 |

が必要な場合に提供します |

スロット、切り抜き、Vスコア、特殊機能 |

|

組立図 |

強く |

位置、ラベル、すべての部品の向き |

|

リビジョン履歴 |

ベストプラク. |

変更に対する完全なトレーサビリティ |

DFMは一度限りのチェックではなく、長期的に技術的およびビジネス上の優位性を築くための取り組みです PCB信頼性 sierra Circuitsでは、ビアアニュラーリング違反や不適切な積層構成の文書化など、DFMの誤りを早期に発見できたプロジェクトを記録しています プロトタイプから量産までのターンアラウンド時間を30%短縮 。短期間でPCBを製造する場合、このような節約が、業界最速の納品と、より機敏な競合他社に市場を奪われるかどうかの差になることがあります。

PCB生産の遅延を最小限に抑え、初回からすべての注文を確実に製造可能にすることをご希望ですか? 無料の[設計段階での製造性向上ハンドブック]をダウンロード —詳細なDFMチェックリスト、実際の事例、および最新のIPCガイドラインが満載。代表的なDFMミスを回避し、設計チームが自信を持って設計できるようにしましょう!

待って 製造設計(DFM) 基板の構造方法について扱い、 組立性設計(DFA) 基板が試作段階でも量産段階でも、どれだけ容易に、正確かつ信頼性高く組み立てられるかに焦点を当てます。DFAの誤りを見過ごすと、 DFAの誤り 高価な再作業、性能の低い製品、および慢性的な問題を引き起こします。 PCB生産の遅延 sierra CircuitsやProtoExpressといった一流施設での実際の製造経験に基づき、PCB組立で最も頻繁に見られる組立エラーと、回路基板が初回で無事に組立工程を通過できるようにするための対策を以下に示します。

理想的な回路図や層構成であっても、 部品の配置ミスやフットプリントのエラー は組立工程を大きく損なう可能性があります。代表的なDFA(設計上の組立性)の落とし穴には以下のようなものがあります。

コンポーネントのフットプリントおよび配置におけるDFAのベストプラクティス:

|

DFAエラー |

影響 |

対策/標準 |

|

フットプリントが一致していない |

部品が取り付けられない、はんだ接合不良が発生 |

IPC-7351のフットプリントを使用、BOMのレビューを実施 |

|

部品同士が近すぎる |

ピックアンドプレースが遅延、ショートブリッジが発生 |

≥0.5mm間隔のレビュー |

|

識別記号が欠落 |

誤実装または部品間違いのリスク |

シルクスクリーン層に明記 |

|

極性の誤り |

量産組立またはテストで不良発生 |

シルクスクリーン/組立図に表示 |

|

ファイドゥシャルマークの不在 |

マシンのアライメントエラー |

各面に3つ、マスク付き銅パッド |

熱を無視すること 実装リフロープロファイル 要件を無視することは、特に現代の小型化されたパッケージにおいて、はんだ接合欠陥や歩留まり低下の主な原因となる。

熱管理/実装プロファイルのためのDFAガイドライン:

|

熱問題 |

DFAのミス |

ソリューション |

|

トombstoning(墓石現象) |

アンバランスなフットプリント/はんだパッド |

センターパッドのサイズが幾何学的形状に近いこと |

|

シャドウイング |

隣接する高さのある部品が赤外線を遮る |

高さが似た部品をグループ化 |

|

リフロー時の温度低下 |

裏面に重い部品がある |

接着剤を使用、または大型部品を表面側に限定 |

モダン 表面実装技術アセンブリ 正確に制御されたはんだペーストのステンシルと互換性のあるフラックスに依存しています。しかし、多くの設計パッケージでは以下のような問題が見られます。

アフターアセンブリの洗浄および保護コーティングは、 PCB信頼性 特に自動車、航空宇宙、産業用途において不可欠です。ここでのDFAミスには以下が含まれます:

PCB生産の遅延 不具合は工場内でのみ発生するわけではありません。調達ミス、旧型部品、トレーサビリティの欠如はすべて再作業や品質低下の原因となります。一般的なDFAのミスには以下が含まれます:

|

DFAの問題 |

影響 |

緩和 |

|

EOL部品 |

直前の再設計 |

四半期ごとのBOMレビュー、長寿命化ポリシー |

|

トレーサビリティなし |

リコールまたは品質保証監査の失敗 |

COCアノテーション、バーコーディング、シリアル番号付きID |

あるロボット製造メーカーは、毎年の顧客向け新製品発表時に断続的な故障に見舞われていました。組立事業者による調査の結果、設計上の2つの関連するDFAミスが判明しました。

そのため、 追跡可能性 または統一された組立手順書が存在しなかったため、不良基板はシステムレベルのテストで失敗するまで検出されませんでした。IPC-7351フォトプリントの採用、明確なピン1マーキングの追加、および四半期ごとのBOMライフサイクル点検を導入したことで、その後の生産では歩留まり率99.8%以上を達成し、現場での重大な問題も解消されました。

一般的なDFAミスを防ぎ、アセンブリ工程を最適化し、市場投入までの時間を短縮するための実践的なガイダンスをさらに得たいですか? プロトタイプから量産まで適用できる詳細なDFAチェックリスト、実際のトラブルシューティング、専門家の知見をまとめた[Design for Assembly Handbook]をダウンロード してください。

製造向け設計 (DFM) は、プリント回路基板(PCB)の設計をデジタルレイアウトから物理的な製造および実装まで円滑に進めるためのエンジニアリング哲学と実用的なガイドラインのセットです。現代のエレクトロニクスにおいて、DFMは単なる「できれば良い」ものではなく、 pCB製造エラーを削減し、生産遅延を最小限に抑え、プロトタイプから量産への移行を飛躍的に加速させるために不可欠です。 .

設計図を作成することは、戦いの半分にすぎません。もしPCBレイアウトが、銅箔のエッチング、層構成、パネルのルーティング、表面処理の選定、実装時のはんだ付けなど、 製造プロセス —銅配線のエッチング、積層構造、パネルのルーティングから表面処理の選定や実装のはんだ付けに至るまで—製造上の制約を無視すれば、 高価な遅延 が急激に増加します。

よくあるケース:

|

原則 |

PCBの信頼性と歩留まりへの影響 |

|

ドキュメントの完全性 |

製造/組立チームが必要なものをすべて確実に取得できるようにする-推測の余地なし。 |

|

製造プロセスとの整合性 |

許容範囲外の特徴に関するリスクを低減し、歩留まりを向上させます。 |

|

明確な設計意図 |

誤解、要求事項の見落とし、または遅延を防止します。 |

|

現実的な公差 |

PCBの仕様をエッチング、ドリル、めっき、および実装プロセスの現実と一致させます。 |

エッジクリアランス デパネライズ中に露出した銅や短絡のリスクを防ぐため、銅パターンとPCB外周の間には十分なスペース(通常≥20ミル)を確保してください。

アシッドトラップ 銅のコーナー部分で鋭角(<90°)の形状を避けてください。このような形状はエッチングの不均一性を引き起こし、断線または短絡の原因となる可能性があります。

部品配置と配線の複雑さ 信号および電源配線を簡素化し、重なり合う層や制御インピーダンス配線を最小限に抑えます。収率を最大化するために、パネル配置を合理的に設計してください。

トレース幅と間隔 電流負荷および予想される温度上昇に応じて、IPC-2152に従ってトレース幅を選定してください。製造上の最小間隔要件および高電圧絶縁要件を遵守してください。

ソルダーレジストおよびシルクスクリーン パッド周囲に少なくとも4ミルのクリアランスを確保してソルダーレジスト開口を定義してください。はんだ接合の信頼性を確保するため、シルクスクリーンインクがパッド上にかからないようにしてください。

ビア設計 すべてのビアタイプ(スルービア、ブラインドビア、バーリッドビア)を明確に文書化してください。HDI基板またはBGA基板における充填ビアまたはキャップ付きビアの要件を明記してください。ビア保護方法についてはIPC-4761を参照してください。

表面処理の選定 機能的要件(ワイヤボンディング、RoHS適合など)および実装能力の両方に合わせて、表面処理(ENIG、HASL、OSPなど)を選んでください。

生産用ファイルの作成 標準化された命名規則を使用し、必要なすべての出力データ(ガーバーファイル、NCドリル、層構成、BOM、IPC-2581/ODB++、ネットリスト)を含めてください。

多くのPCB設計ソフトウェアは自動的にDFMチェックを強制しないため、多くの問題が見逃されます。 DFMミス 主要なツール(Altium Designer、OrCAD、Mentor Graphics PADS、オープンソースのKiCADなど)は以下を提供しています:

PCBレイアウトを製造性に最適化することは、PCB生産の遅延を引き起こすDFMミスやDFAエラーを防ぐために不可欠です。 以下の5つのレイアウト戦略は、ファブリケーションおよびアッセンブリの両方を効率化する実績のある方法であり、PCBの信頼性、歩留まり、長期的なコスト構造を大幅に向上させます。

正しい部品配置は、実装可能なPCB設計の基本です。部品を過度に密集させたり、間隔の規則を守らなかったり、敏感なデバイスを高ストレス領域に配置すると、ピックアンドプレース装置および作業者の両方に負担がかかります。 不適切な配置は、AOI(自動光学検査)の効果低下、不良率の増加、およびPCB実装時の再作業増加を招く可能性があります。

表:理想的な配置と問題のある配置

|

配置上の問題 |

効果 |

予防策 |

|

部品が密集している領域 |

AOIの死角、リワークリスク |

コーティャードおよびDFMルールを使用 |

|

端に高い部品がある |

はんだ付け不完全、デパネライズ時の破損 |

高い部品は中央に配置してください |

|

テストプローブ用のスペースがありません |

テストおよびデバッグの遅延 |

アクセス可能なテストパッドを割り当ててください |

トレースルーティングは単にA点からB点へ接続する以上のものです。不適切なルーティング—鋭角、不適切なトレース幅、不均一な間隔—は、信号品質の問題、はんだ付けの問題、および複雑なデバッグにつながります。 トレース幅と間隔は、エッチング歩留まり、インピーダンス制御、高速性能に直接影響します。

分散型の電源およびグラウンドポアを使用することで、電圧降下を低減し、熱性能を向上させ、EMI(頻繁に問題となる原因)を最小限に抑えることができます。 PCB信頼性 設計が不十分な基板でよく見られる苦情の原因です。

効率的なパネライゼーションは、基板製造および実装工程の両方における生産性を向上させます。一方で、銅箔クリアランスのない過度なVスコアなど、不適切なデパネライゼーション手法は、エッジ部のトレースを破損させたり、グラウンドポアを露出させたりする可能性があります。

例表:パネライゼーションガイドライン

|

考慮事項 |

典型的な値 |

規則/規格 |

|

Vスコアまでの最小銅距離 |

15 mils |

IPC-2221 |

|

基板間の最小ギャップ |

100 mils |

メーカー仕様 |

|

エッジあたりのタブ数 |

2+ |

生産規模 |

回路図やレイアウトがどれほど正確でも、不十分なドキュメントや一致しないBOMは、製造現場での混乱やスケジュールの遅延の主な原因となる。明確で一貫性のあるファイルは 質問を減らし、材料調達の遅延を防ぎ、調達スピードを向上させ、PCB実装工程から何日も短縮できる .

ある大学の研究チームは、製造業者が提供するDFM/DFAチェックリストをレイアウト、配線、ドキュメンテーションに採用したことで、実験で数週間分に及ぶ学期全体を救いました。最初のプロトタイプ量産バッチは、質問事項ゼロでDFMおよびAOIレビューを通過し、これらの基本的な5つのレイアウト戦略を遵守することで実際に時間短縮が可能であることを示しました。

DFM(製造設計)のベストプラクティスを導入することは、高価なミスを避けるためだけではなく、効率を最適化し、製品品質を向上させ、PCB生産スケジュールを確実に維持するための秘策です。 DFMガイドラインを設計プロセスに組み込むことで、歩留まりの向上に加え、円滑なコミュニケーション、容易なトラブルシューティング、優れたコスト管理の恩恵も得られます。これらはすべて、ハードウェアが最初の製作時から信頼性を持つように保証しながら実現されます。

DFMは理論上のPCB設計を、堅牢で再現性があり、迅速に製造可能な物理的な基板へと変換します。その仕組みは以下の通りです。

リスピンおよび手直しの削減

製造遅延の最小化

歩留まりと信頼性の向上

調達および組立の効率化

試作から量産へのスムーズな拡張

|

DFMメリット |

測定可能な成果 |

業界基準 |

|

設計リワークの削減 |

eCOの30~50%削減 |

IPCおよびシリコンバレー調査 |

|

初回通過率の向上 |

複雑な基板(8層以上)で99.5%以上 |

迅速対応メーカーのデータ |

|

市場投入までの時間を短縮 |

サイクルタイム最大30%短縮 |

Sierra Circuitsのケーススタディ |

|

再作業/廃棄率の低下 |

高適合性の製造で1%未満の廃棄率 |

自動車/航空宇宙工場 |

|

スムーズなNPI引継ぎ |

ファイル確認ステップを80%削減 |

NPIプロセス監査 |

設計をデジタル回路図から物理的な実装ボードへと移行する際、 PCB組み立ての欠陥 は何カ月にもわたる綿密なエンジニアリングを台無しにし、高額な遅延を引き起こし、製品全体の信頼性を損なう可能性があります。こうした故障は決して偶然ではなく、ほとんど常にレイアウト、ドキュメンテーション、またはプロセス上のギャップに根本原因があります。これらの多くは設計段階の初期から適切に組み込まれた堅牢な DFMおよびDFAガイドライン によって防止可能です。

|

欠陥タイプ |

症状/検出方法 |

典型的な根本原因 |

|

はんだ接合の欠陥 |

冷たはんだ、ブリッジ、はんだ不足 |

ペースト印刷不良、誤ったフットプリント、パッドの位置ずれ |

|

部品の位置ずれ |

オフセンター、傾き、回転方向の誤り |

不正確なフットプリント、極性の欠落、AOI/ガーバーエラー |

|

トombstoning(墓石現象) |

受動部品の一端が「浮く」 |

熱バランスの不具合、パッドサイズの不一致、加熱ムラ |

|

ソルダーマスクの問題 |

ショート、開口部の露出不良、マスクされていないパッド |

ガーバーデータの誤り、マスク/パッドのオーバーラップ、クリアランスの欠落 |

|

実装テストのギャップ |

テストカバレッジの不備、漏れがある |

テストポイントの欠落/不適切な配置、ネットリストの欠如、不明確なドキュメント |

|

オープン/不完全な接合部 |

目視による開路、テスト失敗 |

パッド内ビアへのウィッキング、リリーフパッドの欠落による冷れんだはんだ |

BGA、細ピッチQFP、高密度両面基板など、複雑さが増すにつれ、自動検査およびテストが中心的な役割を果たします。

医療機器メーカーは、検査で3%の基板に「潜在的」なはんだ接合部が見つかったため、ロットを拒否しました。これらの接合部はAOIでは正常でしたが、熱サイクル後に故障しました。事後分析により、設計上の誤り(DFMエラー)が特定されました。すなわち、ソルダーレジストのクリアランスが不十分であったため、はんだの吸上量にばらつきが生じ、熱負荷下で弱い接合部となっていたのです。改良されたDFMチェックと厳格化されたDFAルールを導入した結果、今後の製造では広範な信頼性試験後も故障はゼロになりました。

|

欠陥 |

DFM/DFAガイドライン |

品質管理のステップ |

|

冷汗/ブリッジ接合 |

IPC-7351パッド、正しいペースト層、DFMチェック |

AOI、外観検査 |

|

部品の位置ずれ |

参照記号(Refdes)、極性マーク、DFAレイアウトレビュー |

ピックアンドプレース検証 |

|

トombstoning(墓石現象) |

バランスの取れたパッド、サーマルリリーフ、早期DFAレビュー |

プロファイルシミュレーション、AOI |

|

ソルダーマスクのエラー |

IPC-2221 マスク規則、Gerber DFMチェック |

AOI、外観検査 |

|

テスト漏れ |

ネットごとのテストポイント、ネットリスト付き |

インサーキット/機能試験 |

最小化における主要因の一つ PCB生産の遅延 および組立欠陥を最小限に抑えるための主要因の一つは、高度に自動化された先進的な製造設備を使用することです。適切な機械装置とプロセス専門知識、およびDFM/DFAに準拠したワークフローを組み合わせることで、迅速なプロトタイピング用であれ高信頼性の大規模生産用であれ、あらゆる設計が最高水準で製造されることを保証します。 PCB信頼性 そして効率性。

キングフィールドの本社には完全に統合された 70,000平方フィート規模の最先端施設が備わっており、 次世代のPCB製造および組立工程を体現しています。これはお客様のプロジェクトにとって以下のような意味を持ちます:

「エンジニアリングがどれほど優れていても、最高の結果は先進的な設備とDFM準拠の設計が一致したときにのみ得られます。これにより、防げるはずのエラーを排除し、一回合格率を向上させ、市場のスケジュールに常に先行できるのです。」 — 製造技術ディレクター、Sierra Circuits

迅速対応能力: 最新の表面実装装置、AOI、プロセス自動化ツールにより、プロトタイプから量産までの完全な工程に対応できます。航空宇宙、防衛、あるいは急速に変化する民生用電子機器向けなど、高難易度のPCBであっても、納期は数日単位で済み、数週間かかることはありません。

|

設備/システム |

機能 |

DFM/DFAへのメリット |

|

LDI露光 |

トレースイメージング |

トレース幅/ピッチの誤差を低減 |

|

AOI(製造/組立) |

目視検査 |

早期の欠陥検出、DFM適合性 |

|

SMT実装機(ピックアンドプレース) |

組み立て |

ファインピッチ/高密度部品に対応 |

|

リフロー炉(マルチゾーン) |

はんだ付け |

最適化されたはんだ接合、不良なし(無鉛) |

|

ロボットはんだ付け |

組立/品質管理 |

一貫性のある接合部、特にスルーホール部品/特殊部品 |

|

放射線検査 |

非破壊 |

BGA、隠れた/内部の欠陥を検証 |

|

洗浄/コーティング |

最終保護 |

過酷な使用条件での信頼性を保証 |

|

トレーサビリティ/ERP |

すべての工程 |

完全なCOC、責任の明確化、迅速な対応 |

今日の極めて競争が激しい電子機器市場において、 品質と同様にスピードが重要です 。新しいデバイスを投入する場合でも、重要なプロトタイプを繰り返し改良する場合でも、量産移行の場合でも、迅速かつ信頼性の高い納品は大きな差別化要因となります。PCB製造の遅延は金銭的な損失以上の代償を払わせます。これにより、より迅速な競合他社に市場全体を奪われてしまう可能性があります。

短期間で提供可能なPCB —製造のみならずフルターンキーアセンブリでも、最短1日、多くても5日という納期—は、シリコンバレーおよびその他の地域における新たな標準となっています。このような俊敏性は、設計が製造プロセスにシームレスに流れ込む場合にのみ可能になります。DFMおよびDFAの取り組みにより、ボトルネックが全く発生しないようにするのです。

|

生産工程 |

標準リードタイム |

急ぎのリードタイム |

|

PCB製造 |

4~7日間 |

1日(迅速対応) |

|

組立(SMT/THT) |

7~10日間 |

2~5日 |

|

機能テスト |

2~3日 |

当日/翌日出荷 |

|

トータルソリューション(基板一式) |

2〜3週間 |

5~7日 |

シリコンバレーにあるウェアラブルテック企業がある高額投資家向けピッチ用に、4日間で動作するプロトタイプを必要としていました。DFM/DFA検証済みファイルを地元の迅速対応パートナーに提供したことで、AOIテスト済み・完全組立・機能確認済みの基板10枚を納期通りに受け取りました。一方、製造ノートが不完全でBOMが欠落していた競合チームは、「設計変更」の状態に1週間費やし、ビジネスチャンスを失いました。

プロトタイプ作成であれ量産拡大であれ、 即時見積もりを取得 sierra Circuitsまたは選択したパートナーから、リアルタイムの納期見積もりが得られます。DFM/DFA検証済みファイルをアップロードすれば、CADから完成基板までのプロジェクトが記録的なスピードで進行します。

プリント回路基板(PCB)の製造は、万人に共通するプロセスではありません。 ウェアラブル電子機器のプロトタイプの要件は、ミッションクリティカルな医療機器や高信頼性の航空宇宙制御基板とはまったく異なります。DFMおよびDFAガイドライン、ならびに製造業者の業界別専門知識は、正常に機能するだけでなく、それぞれの特殊な環境で優れた性能を発揮するPCBを構築するための柱です。

業界のリーダーたちが、さまざまな分野で最高の成果を得るためにDFM/DFAおよび高度なPCB製造技術をどのように活用しているかを見ていきましょう。

|

業界 |

主なDFM/DFAの重点ポイント |

コンプライアンス/規格 |

|

航空宇宙/防衛 |

積層構造の均一性、トレーサビリティ、COC、高度なAOI |

IPC Class 3, AS9100D, ITAR |

|

自動車 |

堅牢な接合部、振動防止、迅速テスト |

ISO 26262, ISO/TS 16949 |

|

民生用/ウェアラブル |

小型化、パネル化、コスト効率 |

IPC Class 2, RoHS |

|

医療機器 |

洗浄性、テストポイントへのアクセス性、生体適合性 |

ISO 13485、FDA 21 CFR 820 |

|

産業用/IoT |

環境保護、耐久性、トレーサビリティ |

RoHS、REACH、UL |

|

大学/研究機関 |

プロトタイプのスピード、学習ツール、ドキュメントテンプレート |

IPC-2221、迅速なDFMレビュー |

高度な電子技術が常に加速する世界において、 PCBの製造遅延や組立不良は単なる技術的課題ではなく、ビジネスリスクである 。本ガイドで詳しく説明してきた通り、納期の遅れや再作業、歩留まり低下の根本原因は、ほぼ常に予防可能な要因に起因している。 DFMミス と DFAの誤り スタックアップ層の不一致、判読不能なシルクスクリーン、テストポイントの欠落など、それぞれのエラーが数週間の遅延、予算超過、あるいは製品の立ち上げ失敗につながる可能性がある。

業界トップのPCBチームやメーカーとそうでないものの差を生み出しているのは、一貫したDFMへの取り組みにある 製造性を考慮した設計 と 組立設計 —後付けではなく、コアとなる能動的な設計手法として。DFMおよびDFAガイドラインを各段階に統合することで、開発プロセス全体を次の通り強化できます。

当社のDFMおよびDFAハンドブックをダウンロード 即座に活用可能なDFM/DFAチェックリスト、トラブルシューティングガイド、実用的なIPC規格参照資料。すべて、次のPCB設計におけるリスクを低減するために作成されています。

業界最高レベルのツールとワークフローを活用 Altium DesignerやOrCADなどの、組み込みDFM/DFAチェック機能を備えたPCB設計ソフトウェアを選択し、出力データは常に製造業者が推奨するフォーマットに合わせましょう。

設計チームと鋳造所エンジニア間で 製造業者を設計プロセスの早い段階から巻き込みましょう。定期的な設計レビュー、製造前における積層構成の承認、共有ドキュメントプラットフォームの活用により、予期せぬ問題を回避し時間を節約できます。

継続的改善の姿勢を採用 各生産工程からの教訓を記録しましょう。内部チェックリストを更新し、製造および実装に関するメモをアーカイブし、パートナーとのフィードバックループを閉じることで、PDCA(Plan-Do-Check-Act)アプローチを採用し、収率と効率の継続的な向上を実現します。

最先端のスタートアップ企業であれ、業界のベテラン企業であれ、DFMおよびDFAをプロセスの中核に据えることが、 欠陥を減少させ、組立を迅速化し、成功裏にスケールアップする最も強力な方法です。 . Sierra CircuitsやProtoExpressのような実績があり、技術主導のメーカーと提携してください。 そして設計凍結から市場投入まで自信を持って進んでください。

Dfm (製造性を考慮した設計)は、エッチング、ドリル加工、めっき、ルーティングなどの基板製造工程が迅速かつ正確に、大規模に実施できるよう、PCBレイアウトと資料を最適化することに焦点を当てます。 DFA (組立性を考慮した設計)は、部品実装、はんだ付け、検査、テスト工程において、誤りや再作業のリスクを最小限に抑えながら円滑に進行できるように基板を設計することを保証します。

|

必ず含めるファイル |

目的 |

|

Gerber RS-274X / ODB++ |

製造用のイメージ/レイヤーデータ |

|

NCドリルファイル |

穴/ビア数および仕様 |

|

スタックアップ図 |

層の材料および厚さの基準 |

|

詳細なBOM(部品表) |

正しい調達情報、ライフサイクル追跡 |

|

ピックアンドプレースファイル |

自動組立機のガイド情報 |

|

ネットリスト(IPC-D-356A) |

電気接続のテストと検証 |

|

製造に関する備考 |

仕上げ、公差、および工程の要件 |

|

機械的/クーティヤード層 |

フライス加工、スロット、およびエッジクリアランス情報 |

設計段階で曖昧さを排除し、最初から製造可能な設計にすることで、直前の設計変更ややり取りによる確認作業、意図しない製造および組立の遅延を回避できます。これにより より迅速なプロトタイピング、信頼性の高い短納期生産、および要求仕様が変更された際に迅速に転換できる能力 .

ホットニュース

ホットニュース2026-01-17

2026-01-16

2026-01-15

2026-01-14

2026-01-13

2026-01-12

2026-01-09

2026-01-08