Các bo mạch in (PCB) là trái tim của thiết bị điện tử hiện đại – cung cấp năng lượng cho mọi thứ, từ các thiết bị tiêu dùng đến các thiết bị y tế quan trọng về an toàn và phương tiện tự hành. Tuy nhiên, mặc dù sự phổ biến rộng rãi và độ tinh vi ngày càng cao của quy trình sản xuất PCB hiện nay, Sự chậm trễ trong sản xuất PCB là một trở ngại quá phổ biến. Những sự chậm trễ này không chỉ làm mất thời gian, mà còn có thể phá hỏng việc ra mắt sản phẩm, làm tăng ngân sách và thậm chí ảnh hưởng đến độ tin cậy tổng thể của sản phẩm.

Trong thị trường công nghệ cạnh tranh khốc liệt, đảm bảo việc chế tạo và lắp ráp PCB nhanh chóng, không lỗi là điều sống còn. Và trong hầu hết các phân tích nguyên nhân gốc rễ, các vấn đề nghiêm trọng chủ yếu bắt nguồn từ hai nguyên nhân chính: Lỗi DFM (Thiết kế để sản xuất) và Lỗi DFA (Thiết kế để lắp ráp) . Mặc dù có rất nhiều tài liệu hướng dẫn và các phương pháp tốt nhất về thiết kế PCB, nhưng một số lỗi phổ biến vẫn tiếp diễn ngay cả với các kỹ sư giàu kinh nghiệm. Những sai lầm này thường trông có vẻ đơn giản ở bề mặt, nhưng lại gây ra tác động sâu rộng: làm tăng số lần thiết kế lại, ảnh hưởng đến tỷ lệ sản phẩm đạt chuẩn và tạo ra các điểm nghẽn lan tỏa qua toàn bộ chuỗi cung ứng.

Bài viết chuyên sâu này sẽ đi tìm hiểu:

Dù bạn là một công ty khởi nghiệp phần cứng đang hướng tới việc chuyển đổi nhanh chóng từ mẫu thử sang sản xuất, hay là một nhóm kỹ thuật đã được thiết lập muốn tối ưu hóa tỷ lệ thành phẩm lắp ráp, thì việc làm chủ Thiết kế cho Sản xuất (DFM) và Thiết kế để dễ lắp ráp (DFA) chính là con đường nhanh nhất để đạt được hiệu quả.

Thiết kế cho Sản xuất (DFM) là nền tảng của việc chế tạo PCB đáng tin cậy và tiết kiệm chi phí. Tuy nhiên, ngay cả trong các nhà máy hàng đầu thế giới, những sai lầm DFM vẫn là nguyên nhân chính gây ra Sự chậm trễ trong sản xuất PCB các vấn đề. Những lỗi thiết kế này có thể trông nhỏ trên màn hình CAD, nhưng lại có thể dẫn đến các điểm nghẽn tốn kém, phế phẩm hoặc phải thiết kế lại trên dây chuyền sản xuất. Các chuyên gia sản xuất của chúng tôi đã tổng hợp những rủi ro phổ biến nhất — và quan trọng hơn, cách để tránh chúng.

Một cấu hình PCB không cân bằng hoặc được chỉ định không chính xác là nguyên nhân dẫn đến thảm họa, đặc biệt trong các thiết kế nhiều lớp. Các vấn đề như thiếu thông tin về độ dày lớp cách điện , không xác định rõ trọng lượng đồng , bố trí bất đối xứng , thiếu kiểm soát trở kháng và các yêu cầu mơ hồ về độ dày mạ hoặc lớp phủ hàn thường dẫn đến:

Các phương pháp tốt nhất cho thiết kế cấu trúc lớp PCB:

|

Bậc |

Mô tả |

Tham khảo |

|

Xác định từng lớp |

Xác định trọng lượng đồng, độ dày điện môi và loại vật liệu cho mỗi lớp |

IPC-2221, IPC-4101 |

|

Duy trì tính đối xứng |

Phản chiếu cấu trúc lớp trên/dưới lõi trung tâm — giảm ứng suất cơ học |

|

|

Bao gồm tất cả các lớp hoàn thiện |

Tính đến mạ, lớp phủ hàn và lớp hoàn thiện bề mặt trong tổng độ dày |

IPC-4552 |

|

Tài liệu các lớp trở kháng |

Sử dụng ghi chú rõ ràng cho các mạng điều khiển trở kháng |

IPC-2141, 2221 |

|

Lưu trữ các chú thích cấu trúc lớp |

Giữ các phiên bản lịch sử và thay đổi dễ truy cập |

|

Thiết kế dây nối có vẻ đơn giản, nhưng vi phạm độ rộng dây nối và khoảng cách thường là một trong những lỗi DFM phổ biến nhất. Các lỗi thường gặp bao gồm:

Danh sách kiểm tra thiết kế đường mạch:

Bảng: Các lỗi phổ biến khi đi dây đường mạch và cách phòng tránh

|

Lỗi DFM |

Hậu quả |

Giải Pháp |

|

Đường mạch quá gần mép |

Lớp đồng bị lộ do router, nguy cơ đoản mạch |

>20 mil cách mép bảng (hướng dẫn sản xuất) |

|

Thiếu teardrop tại via/khe hàn |

Nguy cơ nứt, giảm tỷ lệ thành phẩm |

Thêm teardrop để tăng độ tin cậy |

|

Cặp vi sai không đồng nhất |

Lỗi về độ toàn vẹn tín hiệu (SI) |

Chỉ rõ khoảng cách phù hợp |

|

Khoảng cách nhỏ hơn tiêu chuẩn IPC-2152 |

Ăn mòn/hở mạch/hiệu suất kiểm tra thấp |

Tăng khoảng cách theo IPC-2152 |

Các lỗ via rất cần thiết cho các bảng mạch in nhiều lớp hiện đại, nhưng những lựa chọn thiết kế không phù hợp sẽ tạo ra các thách thức nghiêm trọng về khả năng sản xuất (DFM):

Quy tắc thiết kế lỗ via để đảm bảo khả năng sản xuất:

Lớp chống hàn là nguyên nhân kinh điển gây chậm trễ sản xuất vào phút chót và lỗi lắp ráp:

Rời khỏi hoàn thiện bề mặt không xác định, lựa chọn các tùy chọn không tương thích, hoặc không chỉ rõ trình tự có thể làm ngừng sản xuất ngay lập tức. Tương tự, mơ hồ hoặc thiếu đặc điểm kỹ thuật trong tài liệu của bạn có thể cản trở việc thực hiện đúng cách rãnh V-score, rãnh tách rời hoặc khe gia công.

Dữ liệu sản xuất không đầy đủ hoặc không khớp là lỗi khá phổ biến. Các sai sót DFM thường gặp bao gồm:

Thực hành tốt nhất cho Ghi chú Sản xuất PCB:

Một nguyên nhân thường bị đánh giá thấp gây chậm trễ sản xuất PCB là việc nộp tệp sản xuất không đầy đủ hoặc mâu thuẫn . Ngay cả khi sơ đồ mạch và cấu trúc lớp hoàn hảo, những thiếu sót nhỏ trong tài liệu cũng tạo ra điểm nghẽn làm đình trệ đơn hàng trong quá trình kỹ thuật CAM. Các vấn đề như Sai lệch giữa Gerber và lỗ khoan , mập mờ trong ghi chú sản xuất , các bản sửa đổi bị bỏ qua , và việc thiếu các định dạng quan trọng (ví dụ: danh sách mạng IPC-D-356A, ODB++, hoặc IPC-2581) làm phát sinh các yêu cầu làm rõ và xử lý lại tốn thời gian.

Các lỗi DFM phổ biến với hồ sơ sản xuất:

Các phương pháp tốt nhất cho tài liệu sản xuất PCB:

|

Bậc |

Hành động |

Tham khảo |

|

Kiểm tra chéo tất cả các bản xuất |

Mở Gerbers, NC Drill và bản vẽ sản xuất trong phần mềm xem (GC-Prevue, Altium, v.v.) |

Kiểm tra chất lượng nội bộ |

|

Sử dụng quy ước đặt tên và kiểm soát phiên bản nhất quán |

Gom nhóm các tệp sản xuất vào các thư mục tiêu chuẩn có ghi ngày tháng |

Quản lý phiên bản tự động |

|

Bao gồm tất cả các định dạng yêu cầu |

Tối thiểu: Gerber RS-274X, NC Drill, bản vẽ sản xuất và lắp ráp, cấu trúc lớp, BOM, dữ liệu đặt linh kiện, danh sách kết nối (IPC-D-356A hoặc ODB++/IPC-2581) |

Định dạng phù hợp tiêu chuẩn IPC |

|

Cung cấp ghi chú sản xuất rõ ràng |

Loại hoàn thiện tài liệu, chi tiết trở kháng, các ràng buộc cơ học và yêu cầu kiểm tra |

IPC-2221, IPC-D-356A, năng lực nhà sản xuất |

|

Đính kèm lịch sử sửa đổi |

Bao gồm bảng ghi chú đơn giản về thay đổi hoặc bảng sửa đổi cùng với tài liệu |

Tài liệu ISO 9001:2015 |

|

Xác nhận dữ liệu phù hợp với mục đích thiết kế |

Kiểm tra đầu ra CAD PCB thực tế có khớp với thiết kế gốc hay không — bao gồm cực tính và định hướng |

Xác nhận của nhà thiết kế trước khi phát hành |

Bảng: Danh sách kiểm tra tài liệu PCB thiết yếu

|

Tệp/Tài liệu |

Bắt buộc? |

Chi tiết chính cần xác nhận |

|

Gerber RS-274X |

Có |

Phù hợp với ghi chú sản xuất, có thể lưu trữ/theo phiên bản |

|

NC Drill |

Có |

Kích thước lỗ khoan phù hợp với pad/via theo cấu trúc lớp |

|

BOM |

Có |

Số hiệu linh kiện cập nhật mới nhất, nhà cung cấp, thông tin vòng đời |

|

Gắp và Đặt |

Có |

Tọa độ đặt linh kiện, ký hiệu tham chiếu, hướng xoay |

|

Bản vẽ gia công |

Có |

Tên mạng, cấu trúc lớp, kích thước, lớp hoàn thiện |

|

IPC-D-356A / ODB++ |

Mạnh mẽ |

Để kiểm tra điện và đối chiếu chéo |

|

Lớp cơ khí |

Khi cần |

Khe, rãnh cắt, V-score, các tính năng đặc biệt |

|

Bản vẽ lắp ráp |

Mạnh mẽ |

Vị trí, nhãn, mọi hướng linh kiện |

|

Lịch sử sửa đổi |

Thực hành tốt nhất. |

Đảm bảo truy xuất nguồn gốc đầy đủ cho các thay đổi |

DFM không phải là kiểm tra một lần mà là một quy trình tạo lợi thế lâu dài Độ tin cậy của PCB sierra Circuits đã ghi nhận các dự án trong đó việc phát hiện sai sót DFM như vi phạm vòng tròn vành lỗ thông hoặc tài liệu cấu trúc lớp không đúng giảm thời gian chuyển đổi từ mẫu thử sang sản xuất hàng loạt 30% . Đối với sản xuất bảng mạch in (PCB) nhanh, khoản tiết kiệm này có thể tạo ra sự khác biệt giữa việc giao hàng nhanh nhất phân khúc và thua kém các đối thủ linh hoạt hơn.

Sẵn sàng để giảm thiểu chậm trễ trong sản xuất PCB và đảm bảo mọi đơn hàng đều khả thi về mặt sản xuất ngay từ lần đầu tiên? Tải xuống miễn phí [Sổ tay Thiết kế Đảm bảo Sản xuất] —được tích hợp đầy đủ danh sách kiểm tra DFM chi tiết, các ví dụ thực tế và hướng dẫn IPC mới nhất. Tránh những lỗi DFM kinh điển và trang bị cho đội thiết kế của bạn khả năng tự tin trong thiết kế!

Trong khi Thiết kế cho Sản xuất (DFM) liên quan đến cách thức xây dựng bảng mạch của bạn Thiết kế để dễ lắp ráp (DFA) tập trung vào mức độ dễ dàng, chính xác và đáng tin cậy khi lắp ráp PCB của bạn—cả trong các đợt sản xuất mẫu thử lẫn sản xuất hàng loạt. Việc bỏ qua Lỗi DFA dẫn đến việc phải làm lại tốn kém, sản phẩm hoạt động kém và các vấn đề kéo dài Sự chậm trễ trong sản xuất PCB . Dựa trên kinh nghiệm sản xuất thực tế tại các cơ sở hàng đầu như Sierra Circuits và ProtoExpress, dưới đây là những lỗi lắp ráp mà chúng tôi thường gặp nhất — và cách đảm bảo bảng mạch của bạn vượt qua quy trình lắp ráp PCB ngay từ lần đầu tiên.

Ngay cả khi có sơ đồ lý tưởng và cấu trúc lớp phù hợp, lỗi vị trí đặt linh kiện hoặc chân linh kiện không đúng có thể làm đình trệ quá trình lắp ráp. Các lỗi phổ biến trong thiết kế để dễ lắp ráp (DFA) bao gồm:

Các phương pháp tốt nhất cho DFA trong bố trí và dấu chân linh kiện:

|

Lỗi DFA |

Tác động |

Giải pháp / Tiêu chuẩn |

|

Chân đế không phù hợp |

Linh kiện không lắp vừa, lỗi hàn |

Chân đế theo tiêu chuẩn IPC-7351; rà soát BOM |

|

Các linh kiện quá gần nhau |

Làm chậm quá trình lấy và đặt, gây nối tắt |

đánh giá khoảng cách ≥0.5mm |

|

Thiếu ký hiệu thiết kế |

Nguy cơ đặt sai vị trí hoặc linh kiện sai |

Bắt buộc trên lớp silkscreen |

|

Sai cực tính |

Lỗi lắp ráp hoặc kiểm tra hàng loạt |

Ghi chú trên silkscreen/bản vẽ lắp ráp |

|

Thiếu dấu chuẩn (fiducials) |

Lỗi căn chỉnh máy |

3 điểm mỗi mặt, pad đồng có lớp phủ che |

Bỏ qua yếu tố nhiệt hồ sơ hàn lại lắp ráp là nguyên nhân hàng đầu gây ra các lỗi hàn và tổn thất năng suất, đặc biệt với các gói linh kiện thu nhỏ hiện đại.

Hướng dẫn DFA cho Hồ sơ Nhiệt/Lắp ráp:

|

Vấn đề Nhiệt |

Lỗi DFA |

Giải Pháp |

|

Hiện tượng đứng mộ |

Chân linh kiện/bản mạch không cân xứng |

Kích thước pad trung tâm, phù hợp chặt chẽ về hình học |

|

Hiện tượng che khuất |

Các linh kiện cao chặn tia hồng ngoại |

Gom nhóm các linh kiện có chiều cao tương tự |

|

Sụt nhiệt trong quá trình hàn hồi lưu |

Các bộ phận nặng ở mặt dưới |

Sử dụng keo hoặc hạn chế các bộ phận lớn chỉ ở mặt trên |

Hiện đại Lắp ráp smt dựa vào khuôn hàn chính xác được kiểm soát và chất trợ hàn tương thích. Tuy nhiên, chúng tôi thấy nhiều bộ thiết kế:

Việc làm sạch sau lắp ráp và các lớp phủ bảo vệ là yếu tố thiết yếu đối với Độ tin cậy của PCB —đặc biệt là các ứng dụng ô tô, hàng không vũ trụ và công nghiệp. Những sai sót phổ biến trong DFA ở đây bao gồm:

Sự chậm trễ trong sản xuất PCB và sự cố không chỉ phát sinh tại nhà máy. Lỗi trong mua sắm, linh kiện lỗi thời và thiếu khả năng truy xuất nguồn gốc đều góp phần gây ra việc sửa chữa lại và chất lượng kém. Các lỗi phổ biến trong DFA bao gồm:

|

Vấn đề DFA |

Tác động |

Giảm nhẹ |

|

Linh kiện EOL |

Thiết kế lại vào phút chót |

Xem xét BOM định kỳ hàng quý, chính sách tuổi thọ dài hạn |

|

Không có khả năng truy xuất |

Thất bại trong thu hồi hoặc kiểm toán QA |

Chú thích COC, mã vạch, ID theo từng đơn vị |

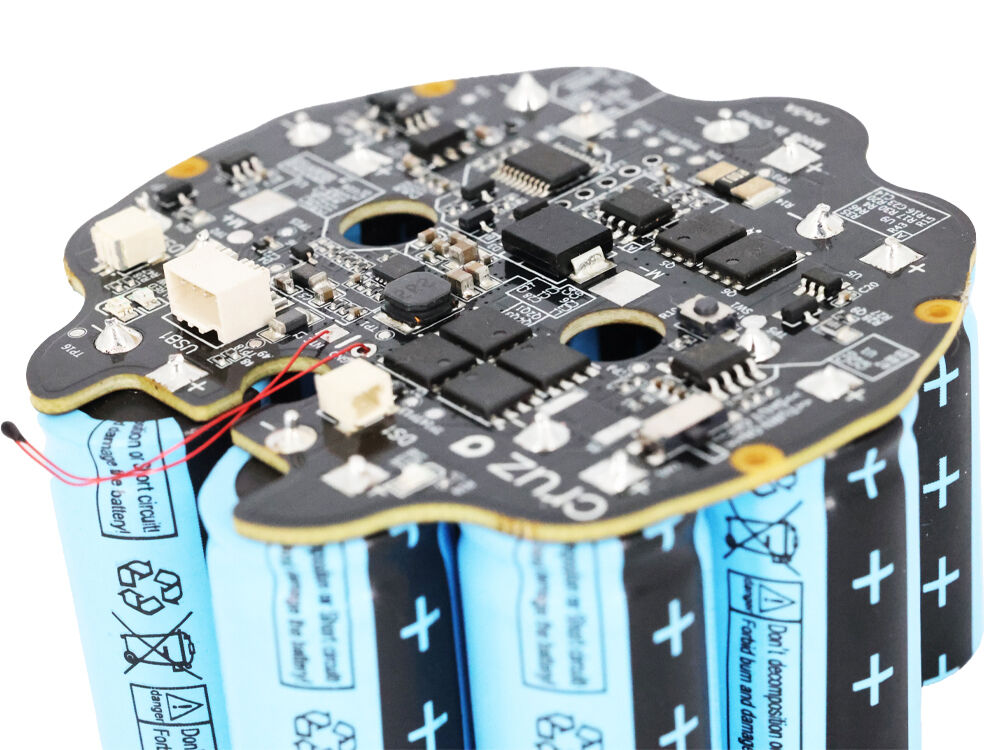

Một nhà sản xuất robot đang gặp phải sự cố ngắt quãng trong buổi ra mắt khách hàng hàng năm. Một cuộc điều tra của bộ phận lắp ráp đã phát hiện hai lỗi DFA liên quan:

Do không có khả năng truy xuất hoặc hướng dẫn lắp ráp đồng bộ, các bo mạch lỗi không được phát hiện cho đến khi xảy ra lỗi trong kiểm tra ở cấp độ hệ thống. Bằng cách bổ sung footprint theo chuẩn IPC-7351, đánh dấu chân Pin 1 rõ ràng, và kiểm tra định kỳ vòng đời BOM hàng quý, các lô sản xuất sau đó đạt tỷ lệ hoàn thiện trên 99,8% và loại bỏ các sự cố nghiêm trọng tại hiện trường.

Bạn muốn có thêm hướng dẫn cụ thể để tránh những lỗi DFA phổ biến, tối ưu hóa quy trình lắp ráp và rút ngắn thời gian đưa sản phẩm ra thị trường? Tải về [Sổ tay Thiết kế Dành cho Lắp ráp] toàn diện của chúng tôi với các danh sách kiểm tra DFA chi tiết, xử lý sự cố thực tế và những phân tích chuyên sâu mà bạn có thể áp dụng từ giai đoạn mẫu thử đến sản xuất hàng loạt.

Thiết kế cho khả năng sản xuất (DFM) là một triết lý kỹ thuật và tập hợp các hướng dẫn thực tiễn nhằm đảm bảo thiết kế bảng mạch in (PCB) của bạn chuyển đổi trơn tru từ bố trí kỹ thuật số sang gia công và lắp ráp vật lý. Trong điện tử hiện đại, DFM không chỉ đơn thuần là yếu tố "mong muốn có"—mà là điều cần thiết để giảm lỗi sản xuất PCB, tối thiểu hóa sự chậm trễ trong sản xuất và tăng tốc đáng kể quá trình từ mẫu thử đến sản xuất hàng loạt .

Thiết kế sơ đồ chỉ là một nửa chặng đường. Nếu bố trí PCB của bạn bỏ qua các quá trình sản xuất yếu tố sản xuất—từ ăn mòn đường dẫn đồng, cấu trúc lớp, định tuyến tấm, đến lựa chọn lớp hoàn thiện bề mặt và hàn trong lắp ráp—khả năng xảy ra sự chậm trễ tốn kém sẽ tăng vọt.

Các Tình Huống Thường Gặp:

|

Nguyên tắc |

Tác động đến Độ tin cậy và Tỷ lệ Thành phẩm của PCB |

|

Độ Đầy đủ của Tài liệu |

Đảm bảo đội ngũ sản xuất/lắp ráp có mọi thứ cần thiết—không phải phỏng đoán. |

|

Sự Phù hợp với Quy trình Sản xuất |

Giảm rủi ro các đặc điểm vượt dung sai, cải thiện tỷ lệ thành phẩm. |

|

Mục đích Thiết kế Rõ ràng |

Ngăn ngừa hiểu nhầm, thiếu yêu cầu hoặc chậm trễ. |

|

Dung sai thực tế |

Phù hợp thông số PCB của bạn với thực tế về ăn mòn, khoan, mạ và các quá trình lắp ráp. |

Khoảng cách lề Để khoảng cách đủ lớn từ các yếu tố bằng đồng đến chu vi PCB (thường ≥20 mil) để tránh hiện tượng hở đồng và nguy cơ đoản mạch trong quá trình tách panel.

Bẫy axit Tránh các hình học góc nhọn (<90°) ở các góc đổ đồng—những góc này gây ra sự không đồng đều khi ăn mòn và nguy cơ đứt mạch hoặc đoản mạch.

Bố trí linh kiện và độ phức tạp trong đi dây Đơn giản hóa việc đi dây tín hiệu và nguồn, giảm thiểu các lớp chồng lấn và các đường truyền trở kháng kiểm soát. Tối ưu hóa việc bố trí panel để đạt tỷ lệ sản phẩm tốt cao nhất.

Chiều rộng và khoảng cách đường mạch Sử dụng tiêu chuẩn IPC-2152 để chọn chiều rộng đường mạch phù hợp với dòng tải và mức tăng nhiệt độ dự kiến. Tuân thủ các quy tắc khoảng cách tối thiểu đối với sản xuất và cách ly điện áp cao.

Lớp phủ hàn và ký hiệu in Xác định các khoảng trống lớp phủ hàn với độ rộng tối thiểu 4 mil xung quanh các pad. Giữ mực in ký hiệu không chạm vào các pad để đảm bảo độ tin cậy của mối hàn.

Thiết kế lỗ via Ghi rõ tất cả các loại via (qua lỗ, via chìm, via kín). Chỉ định yêu cầu về via được đổ đầy hoặc bịt kín trên các bảng HDI hoặc BGA. Tham chiếu tiêu chuẩn IPC-4761 cho các phương pháp bảo vệ via.

Lựa chọn lớp hoàn thiện bề mặt Chọn lớp hoàn thiện phù hợp (ENIG, HASL, OSP, v.v.) dựa trên nhu cầu chức năng (ví dụ: nối dây, đáp ứng RoHS) và khả năng lắp ráp.

Chuẩn bị tệp sản xuất Sử dụng quy tắc đặt tên tiêu chuẩn, bao gồm tất cả các đầu ra cần thiết (Gerbers, NC drill, cấu trúc lớp, BOM, IPC-2581/ODB++, danh sách kết nối).

Không phải tất cả phần mềm thiết kế PCB đều tự động thực thi kiểm tra DFM, đó là lý do tại sao nhiều DFM trượt qua. Các công cụ hàng đầu (như Altium Designer, OrCAD, Mentor Graphics PADS, và KiCAD mã nguồn mở) cung cấp:

Tối ưu hóa bố trí PCB của bạn nhằm đảm bảo khả năng sản xuất là điều cần thiết để ngăn ngừa các lỗi DFM và sai sót DFA gây chậm trễ trong sản xuất PCB. Năm chiến lược sắp xếp sau đây đã được chứng minh là giúp tối ưu hóa quá trình gia công và lắp ráp, cải thiện đáng kể độ tin cậy, tỷ lệ sản phẩm đạt chuẩn và cấu trúc chi phí dài hạn của bo mạch in (PCB).

Việc đặt linh kiện đúng cách là nền tảng để tạo ra một PCB có thể sản xuất được. Việc bố trí các linh kiện quá sát nhau, không tuân thủ quy tắc khoảng cách hoặc đặt các thiết bị nhạy cảm vào khu vực chịu nhiều tác động sẽ gây khó khăn cho cả máy dán linh kiện và nhân công vận hành. Việc bố trí sai cũng có thể dẫn đến kiểm tra quang học tự động (AOI) kém hiệu quả, tỷ lệ lỗi cao hơn và tăng nhu cầu sửa chữa trong quá trình lắp ráp PCB.

Bảng: Cách bố trí lý tưởng so với cách bố trí có vấn đề

|

Vấn đề bố trí |

Tác động |

Chiến lược Phòng Ngừa |

|

Các khu vực linh kiện chật chội |

Điểm mù AOI, rủi ro sửa chữa |

Sử dụng quy tắc courtyard và DFM |

|

Linh kiện cao ở cạnh |

Hàn không đầy đủ, gãy khi tách bảng |

Đặt các linh kiện cao ở vị trí trung tâm |

|

Không đủ chỗ cho đầu dò kiểm tra |

Chậm trễ trong kiểm tra và gỡ lỗi |

Bố trí các pad kiểm tra dễ tiếp cận |

Tuyến tính không chỉ đơn thuần là nối từ điểm A đến điểm B. Việc tuyến tính kém — các góc nhọn, chiều rộng dây dẫn không đúng, khoảng cách không đồng đều — sẽ gây ra các vấn đề về độ toàn vẹn tín hiệu, hàn khó và gỡ lỗi phức tạp. Chiều rộng và khoảng cách dây dẫn ảnh hưởng trực tiếp đến tỷ lệ ăn mòn, điều khiển trở kháng và hiệu suất tốc độ cao.

Việc sử dụng các lớp đổ nguồn và mass phân tán sẽ giảm sụt áp, cải thiện hiệu suất tản nhiệt và giảm thiểu EMI – nguyên nhân phổ biến gây Độ tin cậy của PCB khiếu nại trên các bảng mạch được thiết kế kém.

Việc phân vùng bảng mạch hiệu quả sẽ cải thiện năng suất trong cả giai đoạn chế tạo và lắp ráp, trong khi các phương pháp tách bảng kém (ví dụ như xẻ rãnh V quá sâu mà không có khoảng cách an toàn cho lớp đồng) có thể làm hỏng các đường dẫn ở mép hoặc làm hở lớp đổ đồng nối đất.

Bảng ví dụ: Hướng dẫn phân vùng bảng mạch

|

Cần xem xét |

Giá trị điển hình |

Quy tắc/Tiêu chuẩn |

|

Khoảng cách tối thiểu từ đồng đến V-score |

15 mils |

IPC-2221 |

|

Khe hở bảng tối thiểu |

100 mils |

Thông số của nhà sản xuất |

|

Số lượng tab trên mỗi cạnh |

2+ |

Quy mô sản xuất |

Dù sơ đồ hay bố trí của bạn được thiết kế kỹ lưỡng đến đâu, tài liệu kém và BOM không khớp luôn là nguyên nhân hàng đầu gây nhầm lẫn trong sản xuất và kéo dài tiến độ. Các tệp rõ ràng, nhất quán giảm bớt thắc mắc, ngăn ngừa việc tạm giữ vật tư, cải thiện tốc độ mua sắm và rút ngắn vài ngày trong quy trình lắp ráp PCB .

Một nhóm nghiên cứu tại trường đại học từng cứu vãn cả một học kỳ—hàng tuần thực hiện thí nghiệm—bằng cách áp dụng bảng kiểm DFM/DFA của nhà sản xuất cho bố trí, đi dây và tài liệu. Lô mẫu đầu tiên của họ vượt qua đánh giá DFM và AOI mà không có bất kỳ câu hỏi nào, chứng minh rõ ràng lợi ích tiết kiệm thời gian nhờ tuân thủ năm chiến lược bố trí cơ bản này.

Việc áp dụng các phương pháp tốt nhất DFM (Thiết kế Để Sản Xuất) không chỉ đơn thuần là tránh những sai sót tốn kém—đây còn là vũ khí bí mật để tối ưu hóa hiệu suất, nâng cao chất lượng sản phẩm và đảm bảo tiến độ sản xuất PCB luôn đúng kế hoạch. Khi các hướng dẫn DFM được tích hợp vào quy trình thiết kế của bạn, không chỉ năng suất được cải thiện mà bạn còn được hưởng lợi từ việc giao tiếp thuận lợi hơn, xử lý sự cố dễ dàng hơn và kiểm soát chi phí tốt hơn — tất cả trong khi vẫn đảm bảo phần cứng của bạn đáng tin cậy ngay từ lần sản xuất đầu tiên.

DFM biến các thiết kế PCB lý thuyết thành các bảng mạch vật lý chắc chắn, có thể lặp lại và sản xuất nhanh chóng. Dưới đây là cách thực hiện:

Giảm thiểu việc thiết kế lại và sửa chữa

Giảm thiểu chậm trễ trong sản xuất

Tăng Cường Hiệu Suất và Độ Tin Cậy

Tối Ưu Hóa Quy Trình Mua Sắm và Lắp Ráp

Dễ Dàng Mở Rộng Từ Nguyên Mẫu Sang Sản Xuất Số Lượng Lớn

|

Lợi ích DFM |

Kết quả đo lường được |

TIÊU CHUẨN NGÀNH |

|

Ít phải thiết kế lại hơn |

giảm 30–50% số lượng ECO |

Khảo sát IPC và Thung lũng Silicon |

|

Tỷ lệ sản phẩm đạt ngay từ lần đầu cao hơn |

>99,5% trên các bảng mạch phức tạp (>8 lớp) |

Dữ liệu từ nhà sản xuất nhanh |

|

Thời gian bán nhanh hơn |

Tiết kiệm tới 30% thời gian chu kỳ |

Các nghiên cứu điển hình của Sierra Circuits |

|

Tỷ lệ sửa chữa/lãng phí thấp hơn |

lãng phí dưới 1% trong các bản thiết kế độ chính xác cao |

Nhà máy ô tô/hàng không vũ trụ |

|

Chuyển giao NPI mượt mà hơn |

số bước làm rõ tệp giảm 80% |

Kiểm toán quy trình NPI |

Khi nói đến việc chuyển một thiết kế từ sơ đồ kỹ thuật số sang một bo mạch được lắp ráp thực tế, Các lỗi lắp ráp PCB có thể làm mất đi hàng tháng trời thiết kế cẩn thận, gây ra sự chậm trễ tốn kém và làm suy giảm độ tin cậy của toàn bộ sản phẩm. Những sự cố này không phải ngẫu nhiên; chúng gần như luôn có nguyên nhân gốc rễ từ bố trí, tài liệu hoặc khoảng trống trong quy trình — phần lớn trong số đó có thể được khắc phục bằng cách áp dụng nghiêm ngặt các hướng dẫn DFM và DFA từ giai đoạn thiết kế ban đầu.

|

Loại lỗi |

Triệu chứng/Phát hiện |

Nguyên nhân gốc rễ điển hình |

|

Lỗi hàn |

Mối hàn nguội, cầu nối, thiếu thiếc hàn |

Bố trí hồ sơ kém, dấu chân sai, các pad lệch vị trí |

|

Lệch vị trí linh kiện |

Lệch tâm, nghiêng, quay sai |

Footprint không chính xác, thiếu cực tính, lỗi AOI/Gerber |

|

Hiện tượng đứng mộ |

Một đầu của linh kiện thụ động bị "nâng lên" |

Mất cân bằng nhiệt, kích thước pad không phù hợp, gia nhiệt không đều |

|

Vấn đề về lớp phủ hàn |

Chập, tiếp xúc hở, pad không có lớp phủ |

Gerber không chính xác, chồng lấn giữa mặt nạ và pad, thiếu khoảng cách an toàn |

|

Khoảng trống trong kiểm tra lắp ráp |

Phạm vi kiểm tra không đầy đủ, lỗi sót |

Thiếu điểm kiểm tra hoặc đặt không đúng, không có danh sách kết nối (netlist), tài liệu không rõ ràng |

|

Các mối nối hở/chưa hoàn thiện |

Các vết nứt nhìn thấy được, lỗi trong kiểm tra |

Thấm tràn qua lỗ thông (via-in-pad), mối hàn lạnh do thiếu các pad giảm ứng suất |

Khi độ phức tạp tăng lên—ví dụ như BGAs, QFPs bước nhỏ, hoặc các bo mạch hai mặt dày đặc—việc kiểm tra tự động và kiểm tra sẽ trở thành trọng tâm:

Một nhà sản xuất thiết bị y tế đã loại bỏ một lô hàng sau khi kiểm tra phát hiện 3% các bo mạch có mối hàn 'ẩn suy yếu' — hoàn hảo trong kiểm tra AOI nhưng thất bại sau chu kỳ nhiệt. Phân tích hậu kiểm xác định lỗi là do thiết kế không phù hợp với DFM: khoảng cách mặt nạ hàn không đủ dẫn đến hiện tượng thấm mao dẫn biến đổi và tạo ra các mối nối yếu dưới tải nhiệt. Sau khi áp dụng các kiểm tra DFM sửa đổi và quy tắc DFA nghiêm ngặt hơn, các lần sản xuất tiếp theo đạt được số lỗi bằng không sau các bài kiểm tra độ tin cậy mở rộng.

|

Lỗi |

Hướng dẫn DFM/DFA |

Bước kiểm soát chất lượng |

|

Mối hàn lạnh/chập |

Pad IPC-7351, lớp kem hàn chính xác, kiểm tra DFM |

Kiểm tra AOI, kiểm tra trực quan |

|

Linh kiện đặt sai vị trí |

Ký hiệu tham chiếu (Refdes), đánh dấu cực tính, rà soát bố trí DFA |

Xác minh máy đặt linh kiện |

|

Hiện tượng đứng mộ |

Pad cân bằng, giải nhiệt, rà soát sớm DFA |

Mô phỏng hồ sơ, AOI |

|

Lỗi lớp phủ hàn |

Quy tắc mặt nạ theo IPC-2221, kiểm tra DFM Gerber |

AOI, kiểm tra thực tế |

|

Lỗi thoát kiểm tra |

Điểm kiểm tra trên mỗi mạng, kèm danh sách mạng |

Kiểm tra mạch/chức năng |

Một yếu tố cốt lõi trong việc giảm thiểu Sự chậm trễ trong sản xuất PCB và lỗi lắp ráp là việc sử dụng thiết bị sản xuất tiên tiến, tự động hóa cao. Thiết bị phù hợp—kết hợp với chuyên môn quy trình và quy trình làm việc được thiết kế theo DFM/DFA—đảm bảo mọi thiết kế, dù cho mẫu nhanh hay sản xuất hàng loạt độ tin cậy cao, đều có thể được chế tạo đạt tiêu chuẩn cao nhất Độ tin cậy của PCB và hiệu quả.

trụ sở kingfield có cơ sở tích hợp hoàn toàn, quy mô 70.000 feet vuông, hiện đại bậc nhất , phản ánh thế hệ tiếp theo của các hoạt động sản xuất và lắp ráp PCB. Dưới đây là ý nghĩa đối với các dự án của bạn:

"Dù kỹ thuật của bạn có vững mạnh đến đâu, kết quả tốt nhất chỉ xảy ra khi thiết bị tiên tiến và thiết kế tuân thủ DFM kết hợp với nhau. Đó là cách để loại bỏ các lỗi có thể tránh được, nâng cao tỷ lệ sản phẩm đạt ngay từ lần đầu tiên, và liên tục vượt qua tiến độ thị trường." — Giám đốc Công nghệ Sản xuất, Sierra Circuits

Khả năng Gia công Nhanh: Các công cụ dán bề mặt, kiểm tra quang học tự động (AOI) và tự động hóa quy trình mới nhất cho phép thực hiện trọn vẹn quy trình từ mẫu thử đến sản xuất hàng loạt. Ngay cả các mạch in phức tạp cao—như những mạch dùng trong hàng không vũ trụ, quốc phòng hoặc điện tử tiêu dùng thay đổi nhanh—cũng có thể được chế tạo và lắp ráp trong vài ngày thay vì vài tuần.

|

Thiết bị/Hệ thống |

Chức năng |

Lợi ích DFM/DFA |

|

Tiếp xúc LDI |

Chụp ảnh dấu vết |

Giảm lỗi chiều rộng/khoảng cách dấu vết |

|

AOI (chế tạo/lắp ráp) |

Kiểm tra bằng mắt |

Phát hiện lỗi sớm, tuân thủ DFM |

|

SMT Pick-and-Place |

Cuộc họp |

Xử lý các linh kiện bước nhỏ/mật độ cao |

|

Lò hàn hồi lưu (nhiều vùng) |

Hàn |

Tối ưu hóa, mối nối không lỗi (không chì) |

|

Hàn robot |

Lắp ráp/Kiểm tra chất lượng |

Các mối hàn đồng nhất, đặc biệt là linh kiện THT/linh kiện đặc biệt |

|

Kiểm tra tia X |

Không phá hủy |

Xác minh BGAs, các khuyết tật ẩn/bên trong |

|

Vệ sinh/Phủ lớp bảo vệ |

Bảo vệ cuối cùng |

Đảm bảo độ tin cậy cho các ứng dụng khắc nghiệt |

|

Truy xuất nguồn gốc/ERP |

Tất cả các bước |

COO đầy đủ, trách nhiệm rõ ràng, truy vấn nhanh chóng |

Trong thị trường điện tử siêu cạnh tranh ngày nay, tốc độ quan trọng không kém chất lượng . Dù bạn đang ra mắt một thiết bị mới, cải tiến mẫu thử nghiệm then chốt hay chuyển sang sản xuất số lượng lớn, việc giao hàng nhanh chóng và đáng tin cậy đều là yếu tố tạo sự khác biệt lớn. Những sự chậm trễ trong sản xuất PCB tốn kém hơn cả tiền bạc — chúng có thể khiến bạn mất toàn bộ thị trường vào tay các đối thủ nhanh hơn.

PCB sản xuất nhanh —với thời gian xử lý nhanh tới mức chỉ trong 1 ngày đối với giai đoạn chế tạo và ít nhất 5 ngày cho toàn bộ quy trình lắp ráp chìa khóa trao tay—đang trở thành tiêu chuẩn mới tại Thung lũng Silicon và nhiều nơi khác. Sự linh hoạt này chỉ khả thi khi thiết kế của bạn được luân chuyển liền mạch qua dây chuyền sản xuất, với các thực hành DFM và DFA đảm bảo không có điểm nghẽn nào.

|

Bước Sản xuất |

Thời gian Giao hàng Tiêu chuẩn |

Thời gian sản xuất nhanh |

|

Sản xuất PCB |

4–7 ngày |

1 ngày (nhanh) |

|

Lắp ráp (SMT/THT) |

7–10 ngày |

2–5 ngày |

|

Kiểm tra chức năng |

2–3 ngày |

Trong ngày/Ngày hôm sau |

|

Giải pháp trọn gói (Hoàn chỉnh bảng mạch) |

2–3 tuần |

5–7 ngày |

Một công ty công nghệ đeo tay tại Thung lũng Silicon cần các nguyên mẫu hoạt động cho buổi thuyết trình nhà đầu tư quan trọng — trong vòng bốn ngày. Bằng cách cung cấp các tệp đã được xác minh DFM/DFA cho đối tác gia công nhanh địa phương, họ đã nhận được 10 bo mạch hoàn chỉnh, đã kiểm tra bằng AOI và hoạt động đúng hạn. Một đội cạnh tranh khác với ghi chú sản xuất không đầy đủ và thiếu BOM đã phải mất cả tuần trong tình trạng chờ thay đổi kỹ thuật, bỏ lỡ cơ hội cạnh tranh.

Dù bạn đang phát triển nguyên mẫu hay mở rộng sản xuất, nhận Báo Giá Ngay Lập Tức và dự toán thời gian gia công theo thời gian thực từ Sierra Circuits hoặc đối tác lựa chọn của bạn. Tải lên các tệp đã xác minh DFM/DFA và chứng kiến dự án của bạn chuyển từ CAD sang bo mạch hoàn thiện trong thời gian kỷ lục.

Quy trình sản xuất bảng mạch in (PCB) hoàn toàn không phải là một quy trình áp dụng chung cho mọi trường hợp. Yêu cầu đối với một mẫu thử thiết bị điện tử mặc trên người hoàn toàn khác biệt so với một thiết bị y tế quan trọng về nhiệm vụ hoặc một bo mạch điều khiển hàng không vũ trụ độ tin cậy cao. Các hướng dẫn DFM và DFA—cùng với chuyên môn đặc thù ngành của nhà sản xuất—là nền tảng để chế tạo các bảng mạch PCB không chỉ hoạt động được, mà còn vượt trội trong môi trường sử dụng riêng biệt của chúng.

Hãy cùng xem các doanh nghiệp hàng đầu tận dụng các nguyên tắc DFM/DFA và công nghệ sản xuất PCB tiên tiến như thế nào để đạt kết quả tối ưu trong các lĩnh vực khác nhau:

|

Ngành nghề |

Tập trung chính vào DFM/DFA |

Tuân thủ/Chuẩn mực |

|

Hàng không/Quốc phòng |

Đối xứng chồng lớp, truy xuất nguồn gốc, COC, AOI tiên tiến |

IPC Class 3, AS9100D, ITAR |

|

Ô tô |

Mối nối bền, chống rung, kiểm tra nhanh |

ISO 26262, ISO/TS 16949 |

|

Tiêu dùng/Thiết bị đeo |

Thu nhỏ kích thước, dạng bảng mạch, hiệu quả chi phí |

IPC Class 2, RoHS |

|

Thiết bị Y tế |

Làm sạch, tiếp cận điểm kiểm tra, tính tương thích sinh học |

ISO 13485, FDA 21 CFR 820 |

|

Công nghiệp/IoT |

Bảo vệ môi trường, độ bền cao, khả năng truy xuất nguồn gốc |

RoHS, REACH, UL |

|

Đại học/Nghiên cứu |

Tốc độ tạo mẫu nhanh, công cụ học tập, mẫu tài liệu |

IPC-2221, đánh giá nhanh DFM |

Trong thế giới điện tử tiên tiến không ngừng gia tăng tốc độ, Sự chậm trễ trong sản xuất PCB và các lỗi lắp ráp không chỉ đơn thuần là những trở ngại kỹ thuật—mà còn là rủi ro kinh doanh . Như chúng tôi đã trình bày chi tiết trong hướng dẫn này, nguyên nhân gốc rễ của việc bỏ lỡ thời hạn, phải làm lại và thất thoát tỷ lệ sản phẩm đạt yêu cầu gần như luôn bắt nguồn từ những yếu tố có thể ngăn ngừa được DFM và Lỗi DFA . Mỗi lỗi—dù là lớp xếp chồng không phù hợp, nhãn in silkscreen mơ hồ, hay điểm kiểm tra bị thiếu—đều có thể khiến bạn mất hàng tuần lễ, vượt ngân sách, hoặc thậm chí làm trì hoãn việc ra mắt sản phẩm.

Điều làm nên sự khác biệt cho các đội và nhà sản xuất PCB hàng đầu trong ngành là cam kết không ngừng nghỉ đối với Thiết kế Dành cho Sản xuất và Thiết kế để Lắp ráp —không phải là những suy nghĩ bổ sung, mà là các nguyên tắc thiết kế chủ chốt và chủ động. Khi bạn tích hợp các hướng dẫn DFM và DFA ở mọi giai đoạn, bạn sẽ trao quyền cho toàn bộ chu trình phát triển của mình để:

Tải về sổ tay DFM và DFA của chúng tôi Các danh sách kiểm DFM/DFA có thể thực hiện ngay lập tức, tài liệu hướng dẫn khắc phục sự cố và các tài liệu tham khảo theo tiêu chuẩn IPC—tất cả đều được thiết kế để giảm rủi ro cho thiết kế PCB tiếp theo của bạn.

Tận dụng các công cụ và quy trình làm việc tốt nhất trong ngành Chọn phần mềm thiết kế PCB (ví dụ: Altium Designer, OrCAD) có tích hợp sẵn các kiểm tra DFM/DFA và luôn căn chỉnh đầu ra theo định dạng được nhà sản xuất ưa chuộng.

Thiết lập kênh liên lạc mở Hãy đưa nhà sản xuất vào cuộc trao đổi thiết kế từ sớm. Các buổi xem xét thiết kế định kỳ, phê duyệt cấu trúc lớp trước sản xuất và nền tảng chia sẻ tài liệu chung sẽ giúp tránh bất ngờ và tiết kiệm thời gian.

Áp dụng tư duy cải tiến liên tục Ghi nhận bài học từ mỗi lần sản xuất. Cập nhật danh sách kiểm tra nội bộ, lưu trữ ghi chú về gia công và lắp ráp, đồng thời khép kín vòng phản hồi với các đối tác — áp dụng phương pháp PDCA (Hoạch định - Thực hiện - Kiểm tra - Hành động) để liên tục cải thiện năng suất và hiệu quả.

Dù bạn là một startup tiên phong hay một doanh nghiệp lâu năm trong ngành, việc đặt DFM và DFA vào trung tâm quy trình chính là cách mạnh mẽ nhất để giảm lỗi, tăng tốc độ lắp ráp và mở rộng sản xuất thành công . Hợp tác cùng một nhà sản xuất uy tín, đi đầu về công nghệ như Sierra Circuits hoặc ProtoExpress — và tự tin chuyển từ thiết kế cuối cùng đến ra mắt thị trường.

Dfm (Thiết kế cho Sản xuất) tập trung tối ưu hóa bố trí và tài liệu thiết kế PCB của bạn để quá trình gia công — ăn mòn, khoan, mạ, định tuyến — có thể diễn ra nhanh chóng, chính xác và ở quy mô lớn. DFA (Thiết kế cho Lắp ráp) đảm bảo bảng mạch của bạn sẽ được chuyển qua các giai đoạn đặt linh kiện, hàn, kiểm tra và thử nghiệm một cách trơn tru với nguy cơ lỗi hoặc phải làm lại tối thiểu trong quá trình lắp ráp PCB.

|

Tệp bắt buộc phải có |

Mục đích |

|

Gerber RS-274X / ODB++ |

Dữ liệu hình ảnh/lớp dùng cho chế tạo |

|

Tệp NC Drill |

Số lượng và thông số kỹ thuật lỗ/liên kết thông (via) |

|

Bản vẽ cấu trúc lớp (Stack-Up Drawing) |

Tài liệu tham chiếu vật liệu và độ dày các lớp |

|

BOM chi tiết (Danh sách Vật tư) |

Nguồn cung cấp chính xác, theo dõi vòng đời |

|

Tệp Pick-and-place |

Hướng dẫn máy lắp ráp tự động |

|

Danh sách kết nối (IPC-D-356A) |

Kiểm tra và xác minh các kết nối điện |

|

Ghi chú sản xuất |

Hoàn thiện, dung sai và yêu cầu quy trình |

|

Lớp Cơ khí/Khoảng trống an toàn |

Thông tin phay, rãnh và khoảng cách cạnh |

Bằng cách loại bỏ sự mơ hồ và đảm bảo thiết kế của bạn có thể chế tạo được ngay từ đầu, bạn sẽ tránh được những thay đổi kỹ thuật vào phút chót, các yêu cầu làm rõ qua lại và những sự chậm trễ vô tình trong cả giai đoạn gia công lẫn lắp ráp. Điều này cho phép chế tạo mẫu nhanh hơn, chạy sản xuất nhanh đáng tin cậy và khả năng chuyển đổi nhanh chóng khi yêu cầu thay đổi .

Tin Tức Nổi Bật

Tin Tức Nổi Bật2026-01-17

2026-01-16

2026-01-15

2026-01-14

2026-01-13

2026-01-12

2026-01-09

2026-01-08