Einführung

Leiterplatten (PCBs) sind das Herzstück moderner Elektronik – sie versorgen alles von Consumer-Geräten bis hin zu sicherheitskritischen medizinischen Geräten und autonomen Fahrzeugen mit Energie. Doch trotz ihrer weiten Verbreitung und der raffinierten heutigen PCB-Fertigungsverfahren sind Verzögerungen in der PCB-Produktion ein allzu häufiges Hindernis. Diese Verzögerungen kosten nicht nur Zeit, sondern können auch Produkt-Einführungen vereiteln, Budgets sprengen und sogar die Gesamtzuverlässigkeit des Produkts beeinträchtigen.

Auf dem hart umkämpften Technologiemarkt ist eine schnelle, fehlerfreie PCB-Fertigung und -Bestückung entscheidend. Und bei nahezu jeder Ursachenanalyse lassen sich größere Probleme auf zwei Hauptursachen zurückführen: DFM-Fehler (Design for Manufacturing) und DFA-Fehler (Design for Assembly) . Trotz des umfangreichen Angebots an Ressourcen zu Leiterplattendesign-Richtlinien und Best Practices verfallen selbst erfahrene Ingenieure immer wieder in bestimmte Fallstricke. Diese Fehler erscheinen auf den ersten Blick oft harmlos, haben jedoch tiefgreifende Auswirkungen: Sie führen zu zusätzlichen Neudurchläufen, beeinträchtigen die Ausbeute und verursachen Engpässe, die sich entlang der Lieferkette fortpflanzen.

Dieser ausführliche Artikel behandelt:

- Die häufigsten DFM- und DFA-Fehler, die Verzögerungen bei der Leiterplattenfertigung und -bestückung verursachen, wie sie von professionellen Fertigungs- und Bestückungsteams beobachtet werden.

- Praktische, praxisnahe Lösungen für jedes Problem, einschließlich Prozessänderungen, Checklisten und der Nutzung von IPC-Standards.

- Die entscheidende Rolle der Fertigungsreife bei der Fehlervermeidung, Reduzierung von Nacharbeit und Unterstützung der schnellen Leiterplattenfertigung.

- Umsetzbare Best Practices für Dokumentation, Layout, Schichtaufbau, Via-Design, Lötstoplack, Beschriftung und mehr.

- Einblicke in fortschrittliche Werkzeuge und moderne Ausrüstung, die von führenden Leiterplattenherstellern wie Sierra Circuits und ProtoExpress eingesetzt werden.

- Eine Schritt-für-Schritt-Anleitung zur Ausrichtung Ihres Leiterplattendesigns auf Fertigung und Montage, optimiert für minimale Verzögerungen und maximale Zuverlässigkeit.

Egal, ob Sie ein Hardware-Startup sind, das einen schnellen Übergang vom Prototypen zur Produktion anstrebt, oder ein etabliertes Engineering-Team, das seine Montagedurchlaufquote optimieren möchte – die Beherrschung von Design for Manufacturing (DFM) und Konstruktion für Montage (DFA) ist der schnellste Weg zu Effizienz.

Wiederkehrende DFM-Fehler, beobachtet von unserem Fertigungsteam

Design for Manufacturing (DFM) ist das Rückgrat einer zuverlässigen und kosteneffizienten Leiterplattenfertigung. Doch selbst in erstklassigen Fertigungsstätten sind wiederkehrende DFM-Fehler eine Hauptursache für Verzögerungen in der PCB-Produktion diese Konstruktionsfehler mögen auf einem CAD-Bildschirm als geringfügig erscheinen, können sich jedoch in teure Engpässe, Ausschuss oder Neuentwicklungen auf der Produktionsfläche umwandeln. Unsere Fertigungsexperten haben die hartnäckigsten Fallstricke zusammengestellt – und noch wichtiger, wie man sie vermeidet.

1. Unausgewogene Leiterplatten-Stapelbauweise

Problem:

Ein unausgeglichener oder schlecht spezifizierter PCB-Aufbau ist eine Einladung zur Katastrophe, insbesondere bei mehrlagigen Aufbauten. Probleme wie fehlende Angaben zur Dielektrikumdicke , nicht festgelegte kupfergewichte , asymmetrische Grundrisse , fehlende Impedanzkontrolle und mehrdeutige Vorgaben für Plattierungs- oder Lötstopplackdicke führen oft zu:

- Verzug und Verdrehung während der Laminierung, gebrochene Vias oder Risse in Lötverbindungen

- Signalintegritätsprobleme aufgrund unvorhersehbarer Impedanz

- Herstellungsunsicherheiten aufgrund unvollständiger oder widersprüchlicher Schichtaufbauangaben

- Verzögerungen bei Beschaffung und Prozessplanung

Lösung:

Best Practices für das PCB-Layer-Design:

|

Stufe

|

Beschreibung

|

Referenz

|

|

Geben Sie jede Schicht an

|

Legen Sie Kupfergewicht, Dielektrikumdicke und -typ für jede Schicht fest

|

IPC-2221, IPC-4101

|

|

Symmetrie bewahren

|

Spiegeln Sie den Schichtverbund oberhalb/unterhalb des zentralen Kerns – reduziert mechanische Spannungen

|

|

|

Alle Oberflächenbehandlungen einbeziehen

|

Berücksichtigen Sie Beschichtung, Lötmaske und Oberflächenbeschichtung bei der Gesamtdicke

|

IPC-4552

|

|

Dokumentieren Sie Impedanzschichten

|

Verwenden Sie explizite Hinweise für impedanzgesteuerte Leiterbahnen

|

IPC-2141, 2221

|

|

Archivieren Sie Schichtaufbaubeschreibungen

|

Halten Sie historische Revisionen und Änderungen einfach zugänglich

|

|

2. Leiterbahnbreite, Abstände und Routing-Fehler

Problem:

Die Leiterbahngestaltung erscheint einfach, aber verletzungen der Leiterbahnbreite und -abstände gehören zu den häufigsten DFM-Fehlern. Häufige Fehler sind:

- Unzureichender Freiraum zwischen Leiterbahnen, im Verstoß gegen IPC-2152, was zu Kurzschlüssen oder gestörten Signalen führen kann

- Unzureichender Abstand von Kupfer zum Rand , was Delaminierung oder freiliegende Leiterbahnen nach dem Fräsen riskiert

- Inkonsistenzen beim Abstand von Differenzialpaaren , verursacht Impedanzanpassungsprobleme und Signalintegritätsstörungen

- Gemischte Kupferstärken oder Ätzkompensationsfehler in Hochstromleitungen

- Fehlende Tränenfüllungen an Pads , die die mechanische Zuverlässigkeit an Übergängen von Leiterbahnen zu Via/Pad verringern

Lösung:

Leiterbahn-Design-Checkliste:

- Verwendung leiterbahnbreiten-Rechner (IPC-2152) für jede Leiterbahn basierend auf Strom und Temperaturanstieg

- Mindestabstandsregeln einhalten (>6 mil für Signale, >8–10 mil für Strom/Leiterbahnen in Randnähe)

- Differenzialpaare gleichmäßig anordnen; Impedanzvorgaben in der Schichtaufbaubeschreibung referenzieren

- Immer hinzufügen tränenfüße an Pad/Via/Verbindungsstellen um Bohrungenverlagerung und Alterungsrissbildung zu vermeiden

- Kupfergewicht innerhalb jeder Schicht gleichmäßig halten, sofern nicht anders dokumentiert

Tabelle: Häufige Fehler bei der Leiterbahnführung und deren Vermeidung

|

DFM-Fehler

|

Folge

|

Lösung

|

|

Leiterbahn zu nah am Rand

|

Kupfer durch Fräsen freigelegt, Risiko von Kurzschlüssen

|

>20 mil von der Platinekante entfernt (Fertigungsrichtlinie)

|

|

Kein Tränenanschluss an Via/Pad

|

Rissbildung, Ausschuss bei der Ausbeute

|

Tränenanschlüsse für höhere Zuverlässigkeit hinzufügen

|

|

Inkonsistentes Differenzialpaar

|

SI (Signalintegrität) Fehler

|

Gleichen Abstand explizit vorgeben

|

|

Abstand unterhalb IPC-2152

|

Ätzen/Kurzschluss/niedrige Test-Ausbeute

|

Abstandserhöhung gemäß IPC-2152

|

3. Falsche Via-Designentscheidungen

Problem:

Vias sind essenziell für moderne mehrschichtige Leiterplatten, aber ungeeignete Designentscheidungen führen zu kritischen DFM-Herausforderungen:

- Unzureichende Annularrings was zu unvollständiger Via-Beschichtung oder unterbrochenen Verbindungen führt (Verstoß gegen IPC-2221)

- Zu geringer Via-Abstand verursacht Bohrversatz, Beschichtungsbrücken oder Kurzschlüsse

- Schlecht dokumentierte Via-in-Pad-Designs bei BGAs und HF-Schaltungen, was das Durchsickern von Lot und Verbindungsverluste riskiert

- Mehrdeutigkeit hinsichtlich der Anforderungen an blinde/begrabene Vias oder fehlende Behandlungsspezifikationen für Überdachung, Verstopfung oder Füllung (IPC-4761)

- Fehlende Angaben zu verfüllten oder verdeckten Durchkontaktierungen, die für HDI-Platinen erforderlich sind

Lösung:

Via-Designregeln für die Herstellbarkeit:

- Minimum durchlaufring : ≥6 mil für die meisten Verfahren (gemäß IPC-2221 Abschnitt 9.1.3)

- Bohrabstand: ≥10 mil für mechanische Bohrungen, mehr falls Mikroviaden verwendet werden

- Explizit kennzeichnen via-in-Pad, blinde und vergrabene Via-Typen in den Fertigungsanmerkungen

- Überdachung/Verstopfung logisch anfordern, basierend auf den Montagezielen

- IPC-4761 als Referenz für Via-Schutztechniken heranziehen

- Stellen Sie stets eine Abstimmung mit Ihrem Hersteller her: Einige Fähigkeiten unterscheiden sich zwischen Schnellfertigung und Serienproduktion

4. Lackierschicht- und Beschriftungsfehler

Problem:

Lackierschicht probleme sind eine klassische Ursache für kurzfristige Produktionsverzögerungen und Montagefehler:

- Fehlende oder falsch ausgerichtete Öffnungen in der Lackschicht können benachbarte Pins kurzschließen oder wichtige Leiterbahnen freilegen

- Kein Abstand zu Via-Pads , was zu Lotwanderung oder Brückenbildung führt

- Überdimensionierte Gemeinschaftsöffnungen freilegen von Masseflächen unnötigerweise

- Unscharfe, überlappende oder Silkscreendruck mit geringem Kontrast – schwer lesbar, besonders bei der Einrichtung von Bestückmaschinen

Lösung:

- Definieren lackfensterabstände : IPC-2221 für minimale Lötstopplackstegbreite befolgen, typischerweise ≥4 mil

- Vias verdecken wo erforderlich, um das Durchsickern von Lot zu verhindern

- Vermeiden Sie „geblockte“ Lacköffnungen; halten Sie jede Pads isoliert, es sei denn, der Prozess erfordert etwas anderes

- Verwendung silkscreen-Regeln : Linienbreite ≥0,15 mm, Schrifthöhe ≥1,0 mm, farblich hoher Kontrast, keine Tinte auf blankem Kupfer

- Führen Sie immer DFM-Prüfungen auf Überlappungen und Lesbarkeit des Silkscreens durch

- Fügen Sie Orientierungssymbole und Polungs-Markierungen in der Nähe wichtiger Bauteile hinzu

5. Oberflächenfinish-Auswahl und mechanische Vorgaben

Problem:

Verlassen oberflächenbearbeitung undefiniert, inkompatible Optionen auswählen oder die Reihenfolge nicht angeben kann die Produktion abrupt stoppen. Ebenso können vage oder fehlende maschinelle Merkmale in Ihrer Dokumentation die korrekte Implementierung von V-Schnitt, Trennkerbe oder gefrästem Schlitz verhindern.

Lösung:

- Deutlich geben Sie den Oberflächentyp an (ENIG, HASL, OSP, etc.) und die erforderliche Dicke gemäß IPC-4552

- Verwenden Sie eine spezielle mechanische Ebene, um alle Aussparungen, V-Schnitte, verzinnten Bohrungen und Z-Achsen-Merkmale zu dokumentieren

- Beachten Sie die empfohlene V-Schnitt-Freistellung —mindestens 15 mil Abstand zwischen Kupfer und V-Schnitt-Linien

- Status erforderlich toleranzen und auf die Fähigkeiten Ihres Leiterplattenherstellers abstimmen

6. Fehlende oder inkonsistente Produktionsdateien

Problem:

Unvollständige oder nicht übereinstimmende Produktionsdaten sind erstaunlich häufig. Typische DFM-Fehler sind:

- Gerber-Datei-Abweichungen bei Bohr- oder Bestückdaten

- Widersprüchliche Fertigungsanmerkungen oder mehrdeutige Schichtaufbauangaben

- Fehlende IPC-D-356A-Netzlisten oder ODB++/IPC-2581-Formate, die von modernen Fertigungsstätten benötigt werden

Lösung:

Best Practice für Leiterplattenfertigungsanmerkungen:

- Bieten Gerber-Dateien , NC-Bohrung, detaillierte Fertigungszeichnung, Schichtaufbau und Stückliste in einem konsistenten, standardisierten Benennungsschema

- IPC-D-356A-Netzliste zur Überprüfung einschließen

- Überprüfen Sie die „CAM-Ausgabe“ immer gemeinsam mit Ihrem Hersteller, bevor der Aufbau erfolgt

- Versionierung bestätigen und Querverweise zu Ihren Designänderungen prüfen

7. Fehlende oder inkonsistente Produktionsdateien

Problem:

Eine oft unterschätzte Ursache für Verzögerungen bei der Leiterplattenfertigung ist die Abgabe von unvollständigen oder widersprüchlichen Produktionsdateien . Selbst bei einem fehlerfreien Schaltplan und Schichtaufbau entstehen durch kleine Fehler in der Dokumentation Engpässe, die Bestellungen während des CAM-Engineering-Prozesses stoppen. Probleme wie Gerber-Bohrdatenabweichungen , mehrdeutige Fertigungshinweise , übersehene Revisionen , und das Fehlen entscheidender Formate (z. B. IPC-D-356A-Netzliste, ODB++ oder IPC-2581) führt zu zeitaufwändigen Abstimmungen und Nacharbeiten.

Häufige DFM-Fehler bei Produktionsdateien:

- Widersprüchliche Schichtaufbauten im Vergleich zu den Fertigungszeichnungen

- Bohrdateien verweisen auf Schichten, die in den Gerber-Dateien nicht vorhanden sind

- Inkonsistente Bauteile-Layouts zwischen Stückliste und Bestückungsdateien

- Veraltete oder fehlende Netzliste für den elektrischen Test

- Mehrdeutige mechanische Angaben oder Nutpositionen

- Nicht standardisierte Dateibenennungen (z. B. „Final_PCB_v13_FINALFINAL.zip“)

Lösung:

Best Practices für die Dokumentation von Leiterplattenfertigung:

|

Stufe

|

Aktion

|

Referenz

|

|

Alle Exporte gegenseitig prüfen

|

Öffnen Sie Gerber-, NC-Bohr- und Fertigungszeichnungen in einer Viewer-Software (GC-Prevue, Altium, etc.)

|

Interne Qualitätsprüfung

|

|

Konsistente Benennung und Änderungsverwaltung verwenden

|

Produktionsdateien in standardisierten, datierten Ordnern bündeln

|

Automatisierte Versionsverwaltung

|

|

Alle erforderlichen Formate beifügen

|

Mindestens: Gerber RS-274X, NC-Bohrdatei, Fertigungs- und Baugruppenzeichnungen, Schichtaufbau, BOM, Bestückungsdatei, Netzliste (IPC-D-356A oder ODB++/IPC-2581)

|

IPC-konforme Formate

|

|

Klare Fertigungshinweise bereitstellen

|

Oberflächenart, Impedanzangaben, mechanische Beschränkungen und Prüfanforderungen dokumentieren

|

IPC-2221, IPC-D-356A, Herstellfähigkeiten

|

|

Überarbeitungshistorie anhängen

|

Einfaches Änderungsprotokoll oder eine Überarbeitungstabelle zusammen mit der Dokumentation beifügen

|

ISO 9001:2015 Dokumentation

|

|

Bestätigen, dass die Daten der Konstruktionsabsicht entsprechen

|

Überprüfen, ob die tatsächliche PCB-CAD-Ausgabe mit dem ursprünglichen Design übereinstimmt – einschließlich Polarität und Ausrichtung

|

Freigabe durch den Konstrukteur vor Veröffentlichung

|

Tabelle: Wichtige Prüfliste für die Leiterplattendokumentation

|

Datei/Dokument

|

Obligatorisch?

|

Wichtige Angaben zu bestätigen

|

|

Gerber RS-274X

|

Ja

|

Entspricht Fertigungsanmerkungen, archivierbar/überarbeitet

|

|

NC-Bohrdatei

|

Ja

|

Bohrgrößen entsprechen Lötflächen-/Via-Aufbau

|

|

BOM

|

Ja

|

Aktuelle Teilenummern, Lieferant, Lebenszyklusinformationen

|

|

Bestückung

|

Ja

|

Bestückungskoordinaten, Bauteilegierung, Ausrichtung

|

|

Fertigungszeichnung

|

Ja

|

Netznamen, Schichtaufbau, Maße, Oberfläche

|

|

IPC-D-356A / ODB++

|

Stark

|

Für elektrische Prüfungen und Gegenkontrollen

|

|

Mechanische Schicht

|

Je nach Bedarf

|

Schlitze, Ausschnitte, V-Score, Besonderheiten

|

|

Montagezeichnung

|

Stark

|

Positionen, Beschriftungen, alle Bauteilorientierungen

|

|

Versionshistorie

|

Beste Praxis

|

Vollständige Rückverfolgbarkeit für Änderungen

|

DFM in Aktion: Einsparung von Wochen über den gesamten Produktlebenszyklus

DFM ist keine einmalige Überprüfung, sondern eine Disziplin, die langfristig Wettbewerbs- und Geschäftsvorteile schafft Zuverlässigkeit von Leiterplatten sierra Circuits hat Projekte dokumentiert, bei denen das Erkennen von DFM-Fehlern wie Verstöße gegen den Durchkontaktierungsring oder fehlerhafte Stack-up-Dokumentation die Durchlaufzeiten vom Prototyp bis zur Produktion um 30 % reduziert haben . Bei der schnellen Leiterplattenfertigung kann diese Einsparung den Unterschied zwischen einer marktführenden Lieferzeit und dem Verlust gegenüber agileren Wettbewerbern ausmachen.

Handlungsaufforderung: Laden Sie das DFM-Handbuch herunter

Bereit, Ihre Verzögerungen in der Leiterplattenfertigung zu minimieren und sicherzustellen, dass jeder Auftrag bereits beim ersten Mal herstellbar ist? Laden Sie unser kostenloses [Design for Manufacturing Handbook] herunter —gefüllt mit detaillierten DFM-Checklisten, praktischen Beispielen und den neuesten IPC-Richtlinien. Vermeiden Sie klassische DFM-Fehler und stärken Sie Ihr Entwicklungsteam, um sicher und effizient zu konstruieren!

Wiederkehrende DFA-Fehler, die unser Montageteam beobachtet hat

Während Design for Manufacturing (DFM) bezieht sich darauf, wie Ihre Leiterplatte aufgebaut ist, Konstruktion für Montage (DFA) konzentriert sich darauf, wie einfach, genau und zuverlässig Ihre Leiterplatte montiert werden kann – sowohl bei Prototypen als auch in der Serienproduktion. Die Vernachlässigung von DFA-Fehlern führt zu kostspieligem Nacharbeiten, schlecht funktionierenden Produkten und anhaltenden Problemen Verzögerungen in der PCB-Produktion . Basierend auf realen Erfahrungen aus der Fertigung in führenden Einrichtungen wie Sierra Circuits und ProtoExpress, hier sind die am häufigsten auftretenden Montagefehler – und wie Sie sicherstellen, dass Ihre Leiterplatte bereits beim ersten Mal problemlos durch die Leiterplattenbestückung kommt.

1. Falsche Bauteil-Footprints und Platzierungen

Problem:

Selbst bei einem idealen Schaltplan und Layeraufbau können falsche Bauteilplatzierungen oder Footprint-Fehler die Montage erheblich beeinträchtigen. Typische DFA-Probleme sind:

- Footprints, die nicht zur Stückliste (BOM) oder zu den tatsächlichen Bauteilen passen: Verursacht oft durch nicht übereinstimmende CAD-Bibliotheken oder übersehene Änderungen in den Datenblättern.

- Bauteile, die zu nahe an Platinnenrändern, Prüfpunkten oder zueinander platziert sind: Hindert mechanische Greifer, Reflow-Öfen oder sogar automatische optische Inspektionssysteme (AOI) daran, zuverlässig zu funktionieren.

- Fehlende oder mehrdeutige Positionsbezeichnungen: Beeinträchtigt die Genauigkeit beim Bestücken und führt zu Verwirrung bei manueller Nacharbeit.

- Falsche Ausrichtung oder fehlende Polaritäts-/Pin-1-Markierungen —eine Rezeptur für massenhafte Fehlplatzierungen, die weit verbreitete Funktionsausfälle und Nacharbeit verursachen.

- Courtyard-Verletzungen: Unzureichender Abstand um Bauteile verhindert eine ordnungsgemäße Montage, insbesondere bei hohen Bauteilen oder Steckverbindern.

- Höhenkonflikte: Hohe oder unterseitig bestückte Bauteile behindern Förderbänder oder die Bestückung der zweiten Seite.

- Keine Fiducial-Marken: AOI- und Bestückmaschinen sind auf klare Bezugspunkte für die Ausrichtung angewiesen. Fehlende Fiducials erhöhen die Wahrscheinlichkeit katastrophaler Fehlplatzierungen.

Lösung:

Best Practices für DFA bei Bauteilfußabdruck und Platzierung:

- Immer verwenden IPC-7351-konforme Bauteilfußabdrücke —Überprüfung der Flächenmustergröße, der Lötflächenform und der Umrisse im Lötstoppfilm.

-

Abstandsregeln überprüfen:

- Minimum 0,5 mm Abstand von Kante zu Lötfläche

- ≥0,25 mm zwischen SMT-Lötflächen

- „Keepout“-Bereiche für Befestigungslöcher und Steckverbinder einhalten.

- Sicherstellen bauteilbezeichnungen sind vorhanden und lesbar .

- Polarität und Pin-1-Ausrichtung müssen eindeutig gekennzeichnet sein und mit Datenblatt und Lötstoppfilm übereinstimmen.

- Höchstes Bauteil auf beiden Seiten überprüfen (simultane Bestückung, Förderbahnbreite, Höhenbeschränkungen).

- Fügen Sie 3 globale Fiducials pro Seite hinzu in PCB-Ecken für die Maschinenvison; kennzeichnen Sie sie mit Kupferflächen mit blankem Zinn oder ENIG-Beschichtung.

|

DFA-Fehler

|

Auswirkungen

|

Lösung / Standard

|

|

Fußabdruck stimmt nicht überein

|

Bauteil passt nicht, Lötfehler

|

IPC-7351-Fußabdrücke; BOM-Prüfung

|

|

Bauteile zu nah beieinander

|

Verzögertes Bestücken, Kurzschlüsse durch Überbrücken

|

≥0,5 mm Abstandsüberprüfung

|

|

Fehlende Kennzeichnung

|

Gefahr der Fehlplatzierung oder Verwendung des falschen Bauteils

|

Auf Lötstoppmaske verpflichtend vorsehen

|

|

Falsche Polarität

|

Massenfertigungs- oder Testfehler

|

Auf Lötstoppmaske/Bestückungszeichnung kennzeichnen

|

|

Fehlende Fiducials

|

Maschinenjustierfehler

|

3 pro Seite, Kupferpad mit Maske

|

2. Unzureichende Rücksichtnahme auf Reflow und thermische Einflüsse

Problem:

Thermische Faktoren ignorieren lötprofil für die Bestückung anforderungen sind eine der Hauptursachen für Lötfehler und Ausschuss, insbesondere bei modernen miniaturisierten Gehäusen.

- Tombstoning und Schatteneffekte: Ungleichmäßige Wärmezufuhr oder ungeeignete Pad-Größen führen dazu, dass kleine passive Bauelemente angehoben werden (Tombstoning) oder die Lötung unter hohen Bauteilen verhindert wird (Schatteneffekt).

- Bauteile auf beiden Seiten montiert: Ohne sorgfältige Platzierung können schwere oder wärmeempfindliche Bauteile auf der Unterseite abfallen oder bei der zweiten Lötung falsch verlötet werden.

- Uneinheitliche Zonenheizung: Fehlende thermische Entlastungen an Pads oder Masseflächen verhindern eine gleichmäßige Erwärmung und bergen das Risiko von Kaltlötstellen und inkonsistenten Lötverbindungen.

- Keine thermischen Entlastungen an Strom-/Masseanschlüssen: Verursacht unvollständige Lötverbindungen bei großen Kupferflächen oder Masseebenen.

Lösung:

DFA-Richtlinien für thermisches/Bestückungsprofil:

- Gleichmäßige SMT-Bauteilplatzierung: Größte/höchste Bauteile auf der Oberseite platzieren. Bei zweiseitigem Reflow das Gewicht an der Unterseite begrenzen oder Klebepunkte zur zusätzlichen Halterung vorsehen.

- Thermische Entkopplungspads hinzufügen an jedes Durchkontaktions- oder SMT-Pad, das mit Kupferflächen verbunden ist.

- Layout-DRCs verwenden, um die Wärmeverteilung zu bewerten – Simulation mit dem generischen Reflow-Profil des Herstellers durchführen oder IPC-7530 für bleifreie Prozessfenster konsultieren.

- Überprüfung der Bestückungsreihenfolge anfordern und alle kritischen Prozessanforderungen in den Fertigungsnotizen angeben.

|

Thermisches Problem

|

DFA-Fehler

|

Lösung

|

|

Tombstoning

|

Ungleiche Lötflächen/Lötpads

|

Mittlere Pad-Größen, geometrisch genau abgestimmt

|

|

Abschattung

|

Hohe Nachbarkomponenten blockieren die Infrarotbestrahlung

|

Komponenten mit ähnlicher Höhe gruppieren

|

|

Abkühlung während des Reflows

|

Schwere Teile auf der Unterseite

|

Kleber verwenden oder große Bauteile auf die Oberseite beschränken

|

3. Ignorieren der Lotpastenschicht und Flussmittelverträglichkeit

Problem:

Modern SMT-Montage basiert auf einer präzise gesteuerten Lotpastenschablone und kompatiblem Flussmittel. Dennoch sehen wir viele Design-Pakete:

- Ausschluss der Paste-Schicht für bestimmte Footprints (insbesondere bei kundenspezifischen oder exotischen Bauteilen).

- Nicht-Lötflächen-Öffnungen in der Paste-Schicht, paste dort riskierend, wo keine Lötflächen vorhanden sind, was zu Kurzschlüssen führt.

- Keine Spezifikation der Flux-Klasse oder Trockenbackanforderungen, insbesondere für RoHS im Vergleich zu bleihaltigen Prozessen oder feuchtigkeitsempfindlichen Bauteilen.

Lösung:

- Paste-Schicht einfügen und validieren für alle bestückten SMT-Lötflächen; Schablone an den tatsächlichen Lötflächendimensionen ausrichten.

- Nicht-Lötflächen-Bereiche von der Paste-Schicht ausschließen.

- Fluxtyp / Reinigungsanforderungen spezifizieren —unter Hinweis auf RoHS/Pb-freie Verträglichkeit (IPC-610, J-STD-004) und Angabe, ob eine Vorwärmung oder besondere Handhabung erforderlich ist.

- Verweis auf erforderlichen Lotpastentyp und Schablonenspezifikationen in Ihrer Montagedokumentation.

4. Überspringen von Reinigungs- und Konformbeschichtungsvorschriften

Problem:

Die Nachmontage-Reinigung und Schutzbeschichtungen sind entscheidend für Zuverlässigkeit von Leiterplatten —insbesondere für Automobil-, Luft- und Raumfahrt- sowie Industrieanwendungen. Zu den typischen DFA-Fehlern gehören:

- Nicht definierte Reinigungsprozesse: Lötflussmittelklasse, Reinigungschemikalien und -verfahren nicht spezifiziert.

- Fehlende Maskierungen für Konformbeschichtungen: Keine Angabe von Auslassbereichen, was zu überdeckten Schaltern oder Steckverbindern führen kann.

Lösung:

- Verwenden Sie explizite Hinweise zur Definition flussmittelklasse (z. B. J-STD-004, RO L0), Reinigungschemikalien (Lösungsmittel oder wässrig) und Reinigungsmethode.

- Geben Sie Bereiche für Konformbeschichtungen mithilfe mechanischer Schichten oder farbkodierter Überlagerungen an; kennzeichnen Sie deutlich „nicht beschichten“ und Maskierungsbereiche.

- Stellen Sie COC-Spezifikationen (Certificate of Conformance) bereit, falls Kundenvorgaben oder behördliche Anforderungen bestehen.

5. Übersehen des Komponenten-Lebenszyklus und der Rückverfolgbarkeit

Problem:

Verzögerungen in der PCB-Produktion und Fehler entstehen nicht nur im Werk. Beschaffungsfehler, veraltete Bauteile und fehlende Rückverfolgbarkeit führen allesamt zu Nacharbeit und geringer Qualität. Häufige DFA-Fehler sind:

- Stückliste enthält baugleiche (EOL) oder beschaffungsrisikobehaftete Bauteile —häufig erst beim Einkauf erkannt, was späte Konstruktionsänderungen erforderlich macht.

- Keine Rückverfolgbarkeit oder COC-Anfrage (Certificate of Conformance): Ohne Bauteil-Rückverfolgung ist die Ursachenanalyse von Fehlern oder Produktrückrufen unmöglich.

Lösung:

- Führen Sie regelmäßig Ihre Stückliste durch Lieferantendatenbanken (z. B. Digi-Key, Mouser, SiliconExpert), um Lebenszyklus und verfügbaren Lagerbestand zu prüfen.

- Kennzeichnen Sie die Stückliste mit COC- und Rückverfolgbarkeitsanforderungen, insbesondere für Anwendungen in der Luft- und Raumfahrt, Medizintechnik und Automobilindustrie.

- Geben Sie eindeutige Kennzeichnungen (Loskennungen, Datumskennungen) auf Montagezeichnungen an und fordern Sie Bauteile nur aus autorisierten, rückverfolgbaren Quellen.

|

DFA-Problem

|

Auswirkungen

|

Minderung

|

|

EOL-Bauteile

|

Letztminutiger Neuentwurf

|

Vierteljährliche Stücklistenprüfung, Langlebigkeitsrichtlinie

|

|

Keine Rückverfolgbarkeit

|

Rückruf oder QA-Audit-Fehlschlag

|

COC-Kennzeichnung, Barcode, serienmäßige ID

|

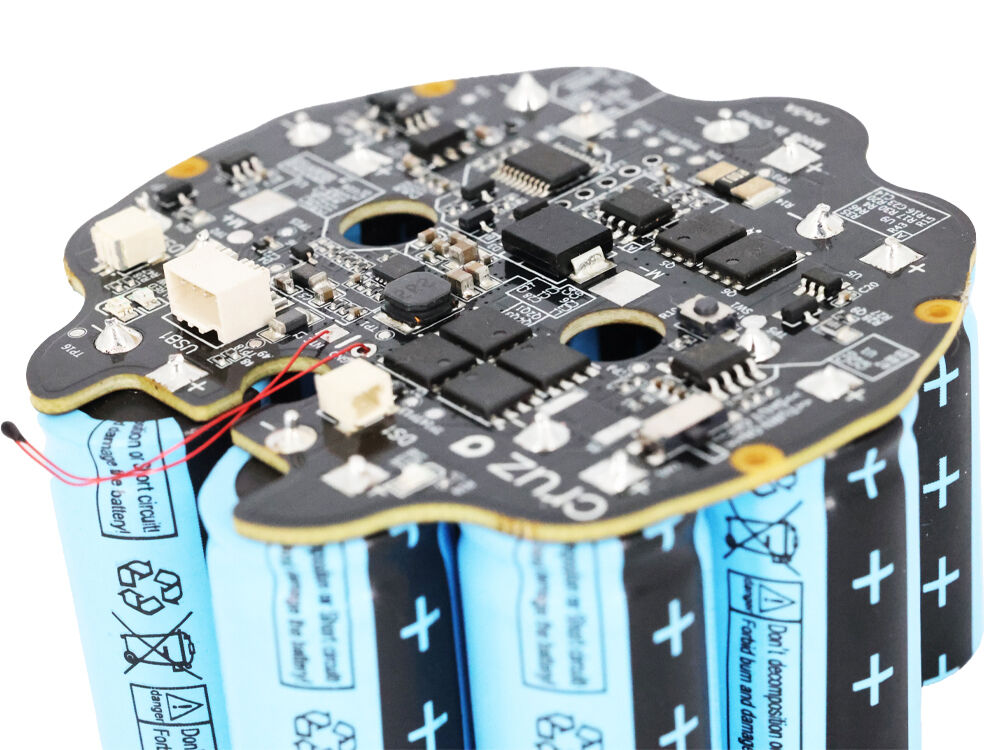

Fallstudie: Durch DFA-getriebene Verbesserung der Ausbeute

Ein Hersteller von Robotern hatte bei der jährlichen Kundenpräsentation sporadische Ausfälle. Eine Untersuchung durch den Bestücker ergab zwei zusammenhängende DFA-Fehler:

- Die Stückliste enthielt einen Logikpuffer am Ende des Lebenszyklus (End-of-Life), der durch ein baugleiches, aber elektrisch anderes Bauteil ersetzt wurde, und

- Die Pin-1-Orientierung des neuen Puffers war im Vergleich zur Siebdruckmarkierung umgekehrt.

Da es keine rückverfolgbarkeit oder koordinierten Montageanweisungen gab, blieben fehlerhafte Leiterplatten bis zu Fehlfunktionen beim Systemtest unentdeckt. Durch die Hinzunahme von IPC-7351-Bauteileinheiten, sichtbaren Pin-1-Markierungen und vierteljährlichen Überprüfungen des Lebenszyklus in der Stückliste erreichten nachfolgende Produktionsläufe eine Ausbeute von über 99,8 % und beseitigten kritische Feldprobleme.

DFA-Fehler: Wichtige Erkenntnisse für die Leiterplattenbestückung

- Stellen Sie immer sicher, dass Stückliste, Bauteilfußabdruck und Platzierungsdateien übereinstimmen mithilfe automatisierter Prüftools in Ihrer Leiterplattendesign-Software (z. B. Altium Designer, OrCAD oder KiCAD).

- Dokumentieren Sie alle montagebezogenen Anforderungen, einschließlich Reinigungsmethoden, Konformbeschichtungsmasken und COC/Nachverfolgbarkeitsanforderungen direkt in Ihren Montage- und Fertigungsanweisungen.

- Nutzen Sie fortschrittliche Fertigungsanlagen : Hochwertige Bestückautomaten, automatische optische Inspektion (AOI) und In-Circuit-Testverfahren erhöhen die Zuverlässigkeit der Montage, vorausgesetzt Ihre Dateien und Designregeln sind korrekt.

- Offene Kommunikation pflegen mit Ihrem Leiterplattenbestückungsservice – Anbieter wie Sierra Circuits und ProtoExpress bieten technische Unterstützung bei der Konstruktion mit Schwerpunkt auf Montagetauglichkeit (DFA) und Qualitätskontrolle.

Aktion erforderlich: Laden Sie das DFA-Handbuch herunter

Möchten Sie noch mehr praktische Anleitungen, um häufige DFA-Fehler zu vermeiden, Ihren Montageprozess zu optimieren und Ihre Markteinführungszeit zu verkürzen? Laden Sie unser umfassendes [Handbuch für Montagetaugliches Design] herunter, mit detaillierten DFA-Checklisten, praxisnahen Fehlerbehebungen und Expertentipps, die Sie vom Prototyp bis zur Serienproduktion anwenden können.

Was ist Leiterplattenlayout-Design für die Fertigungstauglichkeit?

Design for Manufacturability (DFM) ist eine ingenieurtechnische Philosophie und ein Satz praktischer Richtlinien, die sicherstellen sollen, dass Ihr Leiterplattendesign (PCB) reibungslos vom digitalen Layout zur physischen Fertigung und Montage übergeht. In der modernen Elektronik ist DFM nicht nur ein „schönes Extra“, sondern entscheidend für die Reduzierung von Fertigungsfehlern bei Leiterplatten, die Minimierung von Produktionsverzögerungen und die Beschleunigung Ihres Wegs vom Prototyp zur Serienproduktion .

Warum DFM in der Leiterplattenfertigung wichtig ist

Ein Schaltplan zu entwerfen, ist nur die halbe Miete. Wenn Ihr PCB-Layout die herstellungsverfahren —vom Ätzen der Kupferspuren, Layeraufbau und Platinenfräsen bis zur Auswahl der Oberflächenbeschichtung und Lötung in der Bestückung—ignoriert, steigt die Wahrscheinlichkeit von kostspieligen Verzögerungen sprunghaft an.

Häufige Szenarien:

- Eine Platine mit falscher Spurbreite oder -abständen besteht Ätztests nicht und erfordert Neukonstruktionen.

- Eine schlecht definierte Lackschutzlacklage führt zu Kurzschlüssen oder Reflow-Lötfehlern in der Bestückung.

- Weggelassen durch Details (z. B. Via-in-Pad ohne Füllvorgabe) oder mehrdeutige Fertigungshinweise bringen die Produktion zum Erliegen.

Kern-DFM-Grundsätze für die Leiterplattenfertigung

|

Die Kommission

|

Auswirkungen auf die Zuverlässigkeit und Ausbeute von Leiterplatten

|

|

Vollständigkeit der Dokumentation

|

Stellt sicher, dass die Fertigungs-/Bestückungsteams alles Notwendige haben – kein Raten erforderlich.

|

|

Abstimmung des Fertigungsprozesses

|

Reduziert das Risiko von außerhalb der Toleranz liegenden Merkmalen, verbessert die Ausbeute.

|

|

Klare Konstruktionsabsicht

|

Verhindert Fehlinterpretationen, übersehene Anforderungen oder Verzögerungen.

|

|

Realistische Toleranzen

|

Stimmt Ihre Leiterplatten-Spezifikationen mit den Gegebenheiten der Ätz-, Bohr-, Beschichtungs- und Bestückungsprozesse ab.

|

Wichtigste DFM-Richtlinien für die Leiterplattendesigner

Randabstand Halten Sie ausreichend Abstand von Kupferstrukturen zur Leiterplattenkante (typischerweise ≥20 mil), um freiliegendes Kupfer und Kurzschlussrisiken während der Depanelisierung zu vermeiden.

Säurefallen Vermeiden Sie spitze Winkelgeometrien (<90°) in den Ecken von Kupferflächen – diese führen zu ungleichmäßigem Ätzen und potenziellen Unterbrechungen oder Kurzschlüssen.

Bauteilplatzierung und Routing-Komplexität Vereinfachen Sie das Signal- und Stromlauf-Layout, minimieren Sie überlappende Lagen und Leiterbahnen mit kontrollierter Impedanz. Optimieren Sie Ihre Panelisierung für die beste Ausbeute.

Leiterbahnbreite und -abstand Verwenden Sie IPC-2152, um Leiterbahnbreiten entsprechend der Stromlast und dem erwarteten Temperaturanstieg auszuwählen. Beachten Sie die Mindestabstandsregeln für Fertigung und Hochspannungsisolation.

Lötmaske und Beschriftung Lötmaskenöffnungen mit einem Mindestabstand von 4 mil um die Pads herum definieren. Schriftzugstinte von den Pads fernhalten, um eine zuverlässige Lötverbindung sicherzustellen.

Via-Design Alle Via-Typen klar dokumentieren (Durchkontaktierung, blinde, vergrabene). Für HDI- oder BGA-Platinen festlegen, ob gefüllte oder verschlossene Vias erforderlich sind. IPC-4761 für Methoden zum Via-Schutz heranziehen.

Oberflächenbeschichtungsauswahl Wählen Sie die Oberflächenbeschichtung (ENIG, HASL, OSP usw.) entsprechend den funktionellen Anforderungen (z. B. Drahtbonden, RoHS-Konformität) und den Fähigkeiten der Baugruppenbestückung aus.

Vorbereitung der Produktionsdateien Standardisierte Benennung verwenden und alle notwendigen Ausgabedateien einbeziehen (Gerber, NC-Bohrdatei, Schichtaufbau, BOM, IPC-2581/ODB++, Netlist).

Die richtige Design-Software wählen

Nicht alle PCB-Design-Software erzwingt automatisch DFM-Prüfungen, weshalb viele DFM-Fehler durchrutschen. Marktführende Tools (wie Altium Designer, OrCAD, Mentor Graphics PADS und die Open-Source-Lösung KiCAD) bieten:

- DFM und fabrikationsregel-Assistenten

- Echtzeit-DRC- und Abstandsanalyse

- Integrierte Unterstützung für neueste IPC-Standards , Design-Layerschichten und fortschrittliche Via-Typen

- Automatische Erstellung umfassender Ausgabedokumente und Fertigungsdokumentation

5 Layout-Entwürfe für eine fehlerfreie Fertigung

Die Optimierung Ihres Leiterplatten-Layouts hinsichtlich der Fertigungsgerechtheit ist entscheidend, um DFM-Fehler und DFA-Fehler zu vermeiden, die Produktionsverzögerungen verursachen. Die folgenden fünf Layout-Strategien haben sich bewährt, um sowohl die Fertigung als auch die Bestückung zu beschleunigen und Zuverlässigkeit, Ausschussrate sowie langfristige Kosten Ihrer Leiterplatte erheblich zu verbessern.

1. Komponentenplatzierung: Zugänglichkeit und automatisierte Montage priorisieren

Warum es wichtig ist:

Eine korrekte Komponentenplatzierung ist die Grundlage für eine realisierbare Leiterplatte. Wenn Komponenten zu dicht gruppiert werden, Abstandsregeln nicht eingehalten werden oder empfindliche Bauteile in Bereichen mit hoher Belastung platziert werden, erschwert dies sowohl den Bestückungsautomaten als auch menschlichen Bedienern die Arbeit. Eine schlechte Platzierung kann außerdem zu ineffektiver AOI (automatisierte optische Inspektion), höheren Ausschussraten und mehr Nacharbeit während der Leiterplattenbestückung führen.

Bewährte Layout-Methoden:

- Platzieren Sie zuerst die wichtigsten und komplexesten integrierten Schaltungen (ICs), Steckverbinder und hochfrequente Komponenten. Umgeben Sie diese gemäß den Herstellerangaben mit Entkopplungskondensatoren und passiven Bauelementen.

-

Beachten Sie die vom Hersteller und nach IPC-7351 festgelegten Mindestabstände:

- ≥0,5 mm zwischen benachbarten SMD-Bauteilen

- ≥1 mm vom Rand entfernt für Steckverbinder oder Prüfpunkte

- Vermeiden Sie hohe Bauteile in der Nähe von Platinekanten (verhindert Kollisionen während der Depanelisierung und Prüfung).

- Stellen Sie ausreichenden Zugang zu wichtigen Testpunkten und den Strom-/Masseleitungen sicher.

- Halten Sie einen ausreichenden Abstand zwischen analogen und digitalen Bereichen ein, um elektromagnetische Störungen (EMI) zu reduzieren.

Tabelle: Ideale vs. problematische Platzierung

|

Platzierungsproblem

|

Effekt

|

Vorbeugungsstrategie

|

|

Überladene Bauteilbereiche

|

AOI-Blindbereiche, Risiko bei Nacharbeit

|

Verwenden Sie Courtyard- und DFM-Regeln

|

|

Hohes Bauteil am Rand

|

Unvollständige Lötung, Bruch während der Depanelisierung

|

Platzieren Sie hohe Bauteile zentral

|

|

Kein Platz für Testsonden

|

Verzögerungen bei Tests und Fehlerbehebung

|

Weisen Sie zugängliche Testflächen zu

|

2. Optimales Routing: Saubere Signalintegrität und Herstellbarkeit

Warum es wichtig ist:

Das Leiterbahnrouting ist mehr als nur die Verbindung von Punkt A zu Punkt B. Schlechtes Routing – scharfe Winkel, falsche Spurbreite, inkonsistenter Abstand – führt zu Problemen mit der Signalintegrität, Lotproblemen und komplizierter Fehlersuche. Spurbreite und -abstand beeinflussen direkt die Ätzqualität, Impedanzkontrolle und Hochgeschwindigkeitsleistung.

Bewährte Layout-Methoden:

- Verwenden Sie 45-Grad-Knicke; vermeiden Sie 90-Grad-Winkel, um Säureeinschlüsse zu verhindern und den Signalpfad zu verbessern.

- IPC-2152 Spurbreitenrechner: Wählen Sie Spurbreiten entsprechend der Strombelastung (z. B. 10 mil für 1 A bei 1 Unze Kupfer).

- Beibehaltung eines konstanten Abstands bei Differenzpaaren für Leitungen mit kontrollierter Impedanz; dokumentieren Sie dies in Ihren Fertigungsanmerkungen.

- Erhöhen Sie den Leiterbahnrandabstand auf ≥20 mil, um nach dem Fräsen der Platine freiliegendes Kupfer zu vermeiden.

- Minimieren Sie die Länge von Leiterbahnen bei Hochgeschwindigkeitssignalen.

- Vermeiden Sie übermäßigen Via-Einsatz in HF-/Hochgeschwindigkeitspfaden, um Verluste und Reflexionen zu reduzieren.

3. Robuste Strom- und Masseflächen: Zuverlässige Stromversorgung und EMI-Steuerung

Warum es wichtig ist:

Die Verwendung verteilter Strom- und Masseflächen verringert Spannungsabfälle, verbessert die thermische Leistung und minimiert elektromagnetische Störungen (EMI), eine häufige Ursache für Zuverlässigkeit von Leiterplatten beschwerden bei schlecht konzipierten Leiterplatten.

Bewährte Layout-Methoden:

- Verwenden Sie nach Möglichkeit komplette Layer für Masse und Stromversorgung.

- Nutzen Sie „Stern“- oder segmentierte Verbindungen, um Übersprechen zwischen digitalen/analogeren Bereichen zu minimieren.

- Vermeiden Sie geschlitzte oder „unterbrochene“ Masseflächen unter Signalleitungen (insbesondere bei Hochgeschwindigkeit).

- Verbinden Sie Ebenen mit mehreren niederinduktiven Durchkontaktierungen, um die Fläche der Stromschleife zu verringern.

- Beziehen Sie den Aufbau der Referenzebene für Stromversorgung/Masse in Ihre Dokumentation für den Hersteller ein.

4. Effektive Panelisierung und Depanelisierung: Vorbereitung für die Skalierung der Produktion

Warum es wichtig ist:

Eine effiziente Panelisierung verbessert den Durchsatz sowohl bei der Fertigung als auch beim Bestücken, während ungeeignete Depanelisierungsverfahren (wie aggressive V-Nuten ohne ausreichenden Kupferabstand) Randspuren beschädigen oder Masseflächen freilegen können.

Bewährte Layout-Methoden:

- Gruppieren Sie Leiterplatten in Standardpanelen; ziehen Sie die Panelanforderungen Ihres Herstellers (Größe, Werkzeugbohrungen, Fiducial-Marken) heran.

- Verwenden Sie dedizierte Abbruchlaschen und Mauselöcher, und führen Sie niemals Leiterbahnen zu nahe an die Kontur der Platine heran.

- Halten Sie einen Kupfer-abstand zur V-Nut von mindestens 15 mil ein (IPC-2221).

- Geben Sie klare Anweisungen zur Depanelisierung in den Fertigungsnotizen/Mechanikebenen an.

Beispieltabelle: Richtlinien zur Panelisierung

|

Überlegung

|

Typischer Wert

|

Regel/Standard

|

|

Min. Kupfer bis V-Schnitt

|

15 mils

|

IPC-2221

|

|

Min. Platinenabstand

|

100 mils

|

Herstellerspezifikation

|

|

Tabs pro Kante

|

2+

|

Produktionsgröße

|

5. Dokumentation und BOM-Konsistenz: Der Klebstoff zwischen CAD und der Fabrik

Warum es wichtig ist:

Egal wie gut durchdacht Ihr Schaltplan oder Layout ist, schlechte Dokumentation und inkonsistente Stücklisten sind eine Hauptursache für Missverständnisse in der Fertigung und verzögerte Zeitpläne. Klare, konsistente Dateien reduzieren Rückfragen, vermeiden Materialrückhaltungen, beschleunigen die Beschaffung und sparen Tage im Leiterplattenbestückungsprozess .

Bewährte Layout-Methoden:

- Verwenden Sie standardisierte, versionskontrollierte Benennung und Dateibündelung.

- Stellen Sie vor der Freigabe eine Gegenprüfung von BOM, Bestückungsplan, Gerber- und Baugruppenzeichnungen sicher.

- Beziehen Sie alle Angaben zur Ausrichtung/Polarität, Beschriftung (Silkscreen) und mechanischen Daten ein.

- Überprüfen Sie nochmals die neuesten Teileversionen und kennzeichnen Sie „Do Not Install“ (DNI)-Positionen deutlich.

Erfolgsgeschichte: Schaltplan trifft Silkscreen

Ein Forschungsteam einer Universität rettete einmal ein ganzes Semester – wochenlange Experimentierzeit – indem es die DFM/DFA-Checkliste eines Herstellers für Layout, Routing und Dokumentation übernahm. Ihre erste Prototypenserie bestand die DFM- und AOI-Prüfung ohne Rückfragen, was die messbaren Zeiteinsparungen beim Anwenden dieser fünf grundlegenden Layout-Strategien unter Beweis stellte.

Wie DFM-Richtlinien die Effizienz der Leiterplattenfertigung verbessern

Die Umsetzung von DFM-(Design for Manufacturing-)Best-Practices dient nicht nur dazu, kostspielige Fehler zu vermeiden – sie ist die Geheimwaffe, um die Effizienz zu optimieren, die Produktqualität zu steigern und die Fertigungszeiten für Leiterplatten einzuhalten. Wenn DFM-Richtlinien in Ihren Designprozess integriert werden, verbessert sich nicht nur Ihre Ausbeute, sondern Sie profitieren auch von reibungsloserer Kommunikation, einfacherem Fehlerbeheben und besserer Kostenkontrolle – alles bei gleichbleibend zuverlässiger Hardware bereits ab dem ersten Aufbau.

Der Effizienz-Einfluss: DFM-Richtlinien in der Praxis

DFM verwandelt theoretische Leiterplattendesigns in physische Platinen, die robust, reproduzierbar und schnell herstellbar sind. So funktioniert es:

Reduzierte Neubearbeitungen und Nacharbeiten

-

- Frühzeitige DFM-Prüfungen erkennen geometrische Fehler, Schichtaufbau-Probleme und Routing-Fehler, bevor Leiterplatten gefertigt werden.

- Weniger Designiterationen bedeuten weniger verlorene Zeit sowie niedrigere Kosten für Prototypen und Serienfertigung.

- Tatsache: Branchenstudien zeigen, dass die Anwendung vollständiger DFM/DFA-Checklisten die durchschnittliche Anzahl technischer Änderungsaufträge (ECOs) halbiert und so pro Projekt mehrere Wochen einspart.

Minimierte Produktionsverzögerungen

-

- Vollständige Dokumentation und standardisierte Fertigungsanmerkungen beseitigen Unterbrechungen zur Abklärung zwischen Entwicklung und Fertigungs-/Bestückungsteams.

- Automatische DFM-Regelprüfungen (in Tools wie Altium oder OrCAD) helfen dabei, sicherzustellen, dass Dateien während des gesamten Workflows fehlerfrei sind.

- Die Einhaltung von DFM-Vorgaben vereinfacht Schnellproduktionsaufträge – Leiterplatten können innerhalb weniger Stunden nach Freigabe der Dateien in die Produktion gehen.

Verbesserte Ausbeute und Zuverlässigkeit

-

- Korrekte Leiterbahnbreite und -abstände gemäß IPC-2152 führen zu weniger Kurzschlüssen und besserer Signalintegrität.

- Robuste Via-Konstruktion (gemäß IPC-4761, IPC-2221) gewährleistet hohe Durchlaufmengen und Langzeit-Zuverlässigkeit, auch bei dichten BGAs oder Feinraster-Bauteilen.

- Daten zeigen, dass Fabriken mit strengen DFM-Programmen eine Erstlaufquote von >99,7 % bei hochkomplexen Leiterplatten erreichen.

Vereinfachte Beschaffung und Bestückung

-

- Saubere erstellte Stücklisten (BOM) und vollständige Bestückungsdateien ermöglichen es Beschaffungs- und Montagepartnern, ohne Verzögerungen mit der Arbeit zu beginnen.

- Vollständig spezifizierte Oberflächenbeschichtung und Schichtaufbau verkürzen die Lieferzeit und stellen sicher, dass Bauteile entsprechend der Bestellung beschafft werden können.

Einfache Skalierung vom Prototyp bis zur Serienproduktion

-

- Leiterplatten, die für die Herstellbarkeit konzipiert sind, lassen sich leichter panelisieren, testen und für Serienfertigung hochskalieren – entscheidend für Start-ups und schnelle Hardware-Änderungen.

DFM-Vorteilstabelle: Effizienz-Kennzahlen

|

DFM-Vorteil

|

Messbares Ergebnis

|

BRANCHENSTANDARD

|

|

Weniger Designüberarbeitungen

|

30–50 % Reduzierung von ECOs

|

IPC & Silicon Valley Umfrage

|

|

Höhere Erstpass-Ausbeute

|

>99,5 % bei komplexen Leiterplatten (>8 Lagen)

|

Daten von Schnellfertigern

|

|

Schnellere Markteinführungszeit

|

Bis zu 30 % Zeitersparnis im Produktionszyklus

|

Sierra Circuits Fallstudien

|

|

Geringere Nacharbeit/Ausschussraten

|

<1 % Ausschuss bei hochkomplexen Baugruppen

|

Automobil-/Luftfahrtfabriken

|

|

Reibungslosere NPI-Übergaben

|

80 % weniger Schritte zur Dateiklärung

|

NPI-Prozessaudits

|

Best Practices: DFM in Ihren Prozess integrieren

- DFM frühzeitig beginnen: Behandeln Sie DFM nicht als letzte Checkliste. Prüfen Sie DFM-Randbedingungen und Schichtaufbauoptionen, sobald Sie mit der Schaltplanerfassung beginnen.

- Zusammenarbeit mit Fertigungspartnern: Geben Sie frühe Layoutentwürfe zur Überprüfung frei. Proaktive Eingaben Ihres Bestückungspartners oder Fertigers verhindern kostspielige Iterationen.

- Dokumentationsstandards durchsetzen: Verwenden Sie IPC-2221 für klare Schichtaufbauten, IPC-2152 für Leiterbahnbemessung und IPC-7351 für Bauteilfußabdrücke.

- DFM-Prüfungen automatisieren: Moderne PCB-Design-Tools können Klarform-, Bohr-/Fräs- und Lötstopplackfehler kontextbezogen erkennen, bevor Dateien versandt werden.

- Aktualisieren und archivieren Sie Ihre DFM-Checkliste: Dokumentieren Sie Erkenntnisse aus jedem Projekt, um kontinuierliche Verbesserungen des Prozesses sicherzustellen.

Grundlagen und Vermeidung von Fehlern bei der Leiterplattenbestückung

Wenn es darum geht, ein Design von der digitalen Schaltung bis hin zur physisch bestückten Platine umzusetzen, Fehler bei der Leiterplattenbestückung können Monate sorgfältiger Konstruktion rückgängig machen, kostspielige Verzögerungen verursachen und die Zuverlässigkeit Ihres gesamten Produkts beeinträchtigen. Diese Ausfälle sind nicht zufällig; sie haben fast immer ihre Ursachen in Layout, Dokumentation oder Prozesslücken – die meisten davon lassen sich durch robuste DFM- und DFA-Richtlinien bereits in einer frühen Phase Ihres Entwurfsprozesses beheben.

Häufigste Fehler bei der Leiterplattenbestückung

|

Fehlertyp

|

Symptome/Erkennung

|

Typische Ursache(n)

|

|

Lötfehler

|

Kaltlötstellen, Brücken, unzureichendes Lot

|

Schlechte Pastenapplikation, falscher Footprint, falsch ausgerichtete Pads

|

|

Bauteilfehlausrichtung

|

Außermittig, verdreht, falsche Ausrichtung

|

Falsche Bauteilumrisse, fehlende Polung, AOI/Gerber-Fehler

|

|

Tombstoning

|

Ein Ende eines passiven Bauelements „hebt ab“

|

Thermisches Ungleichgewicht, nicht passende Lötflächen, ungleichmäßige Erwärmung

|

|

Lackierungsprobleme

|

Kurzschlüsse, offene Entlastungen, unmaskierte Lötflächen

|

Falsche Gerber-Daten, Überlappung von Lack und Lötfläche, fehlende Abstände

|

|

Lücken in der Baugruppenprüfung

|

Unvollständige Testabdeckung, durchschlüpfende Fehler

|

Fehlende/schlecht platzierte Prüfpunkte, keine Netlist, unklare Dokumentation

|

|

Offene/unvollständige Verbindungen

|

Sichtbare „offene“ Stellen, Prüffehlschläge

|

Vias in Pad mit Benetzung, kalte Lötstelle aufgrund fehlender Entlastungspads

|

Fehlerverhütung: DFM, DFA und Integration des Fertigungsprozesses

1. Lötfehler (kalte Lötstellen, Brücken, ungenügendes Lot)

- Ursache: Kleine oder falsch ausgerichtete Pads, ungeeignet dimensionierte Schablonenöffnungen, falsche Bauteilplatzierung oder unregelmäßige Reflow-Lötprofile.

-

Prävention:

- Verwendung IPC-7351-Bauteilefussabdrücke für die Dimensionierung von Pads und Öffnungen.

- Überprüfen Sie die Lötstopplack-Schicht, um sicherzustellen, dass die Öffnungen korrekt sind.

- Simulieren und optimieren Sie Reflow-Profile für bleihaltiges und bleifreies Löten.

- Gewährleisten Sie eine gleichmäßige, glatte Auftragung der Paste mithilfe von Schablonen, die auf die Lötflächengröße abgestimmt sind.

2. Fehlplatzierung oder Fehlausrichtung von Bauteilen

- Ursache: Nicht übereinstimmende Lötstopplack- und Bestückungsdaten, fehlende oder unklare Pin-1-Kennzeichnungen, Platzierung zu nahe an den Platinerändern.

-

Prävention:

- Überprüfen Sie Design-Daten und Montageanweisungen gegenseitig.

- Machen Sie Polarisierungs-, Orientierungs- und Bauteilekennzeichnungen im Lötstopplack eindeutig.

- Halten Sie einen Mindestabstand (≥0,5 mm) ein und verwenden Sie AOI für die Inspektion in frühen Prozessstadien.

3. Tombstoning und Verschattung

- Ursache: Ungleiche Lötflächengrößen, thermische Gradienten über die Pads hinweg oder Platzierung in der Nähe großer Kupferflächen (fehlende Wärmesperren).

-

Prävention:

- Gleichen Sie die Pad-Geometrie für passive Bauelemente (z. B. Widerstände, Kondensatoren) an.

- Fügen Sie Wärmesperren bei Pads hinzu, die mit Masse- oder Stromflächen verbunden sind.

- Platzieren Sie kleine Passivbauelemente fernab von großen, wärmeleitenden Kupferflächen.

4. Lötstopplack- und Beschriftungsfehler

- Ursache: Überlappende Beschriftung auf Lötflächen, zu kleine oder zu große Öffnungen im Lötstopplack, fehlende Via-Vergussung oder unbedeckte kritische Leiterbahnen.

-

Prävention:

- Beachten Sie die IPC-2221 DFM/DFA-Checklisten bezüglich der Breite der Lötstopplackbrücken und der Größen der Öffnungen.

- Prüfen Sie die Gerber- und ODB++-Ausgaben vor Freigabe zur Fertigung mit einem DFM-Tool.

- Trennen Sie Beschriftungselemente eindeutig von bestückbaren Bereichen.

5. Prüflücken und Zugänglichkeit

- Ursache: Unzureichender Prüfzugang (Prüfpunkte), unvollständige Netlist, unklare elektrische Prüfanweisungen.

-

Prävention:

- Stellen Sie mindestens einen zugänglichen Prüfpunkt pro Netz bereit.

- Geben Sie eine vollständige IPC-D-356A- oder ODB++-Netlist an die Hersteller weiter.

- Dokumentieren Sie alle Anforderungen und erwarteten Testverfahren.

Erweiterte Qualitätskontrolle: AOI, Röntgen und In-Circuit-Test

Mit zunehmender Komplexität – denken Sie an BGAs, feinrastige QFPs oder dicht bestückte Doppelseitenplatinen – rücken automatisierte Inspektion und Prüfung in den Vordergrund:

- Automatische optische Inspektion (AOI): Prüft jede Lötstelle auf Fehler bei Bauteilplatzierung, Lotanwendung und Ausrichtung. Branchendaten zeigen, dass AOI mittlerweile über 95 % aller Fehler im ersten Fertigungsdurchlauf erfasst.

- Röntgeninspektion: Unverzichtbar bei Bauteilen mit verdeckten Lötstellen (BGAs, Wafer-Level-Gehäuse), um Poren oder unvollständige Verbindungen zu erkennen, die AOI nicht sichtbar machen kann.

- In-Circuit-Test (ICT) und Funktionstest: Stellen Sie nicht nur eine korrekte Montage sicher, sondern auch die elektrische Funktion unter extremen Temperatur- und Umgebungsbedingungen.

Beispiel: DFM/DFA rettet den Tag

Ein Hersteller medizinischer Geräte lehnte eine Charge ab, nachdem Tests ergaben, dass 3 % der Leiterplatten „latente“ Lötstellen aufwiesen – perfekt bei der AOI, fielen aber nach thermischem Zyklus aus. Die Ursachenanalyse identifizierte einen DFM-Fehler: unzureichender Abstand der Lötstopplack führte zu variabler Saugwirkung und schwachen Verbindungen unter thermischer Belastung. Mit überarbeiteten DFM-Prüfungen und strengeren DFA-Regeln erreichten zukünftige Baugruppen null Ausfälle nach umfangreichen Zuverlässigkeitstests.

Zusammenfassungstabelle: DFM/DFA-Präventionstechniken

|

Fehler

|

DFM/DFA-Richtlinie

|

Qualitätskontrollschritt

|

|

Kalte/überbrückte Lötstellen

|

IPC-7351-Pads, korrekte Paste-Ebene, DFM-Prüfungen

|

AOI, optische Inspektion

|

|

Falsch platzierte Bauteile

|

Bauteilkennzeichnung, Polungsmarkierung, DFA-Layoutprüfung

|

Pick-and-Place-Verifikation

|

|

Tombstoning

|

Ausgeglichene Pads, Wärmeführung, frühe DFA-Prüfung

|

Profil-Simulation, AOI

|

|

Lötstopplackfehler

|

IPC-2221-Lackregeln, Gerber-DFM-Prüfung

|

AOI, optische Inspektion

|

|

Testdurchlässe

|

Prüfpunkt pro Netz, Netzanbindung enthalten

|

In-Circuit-/Funktionsprüfung

|

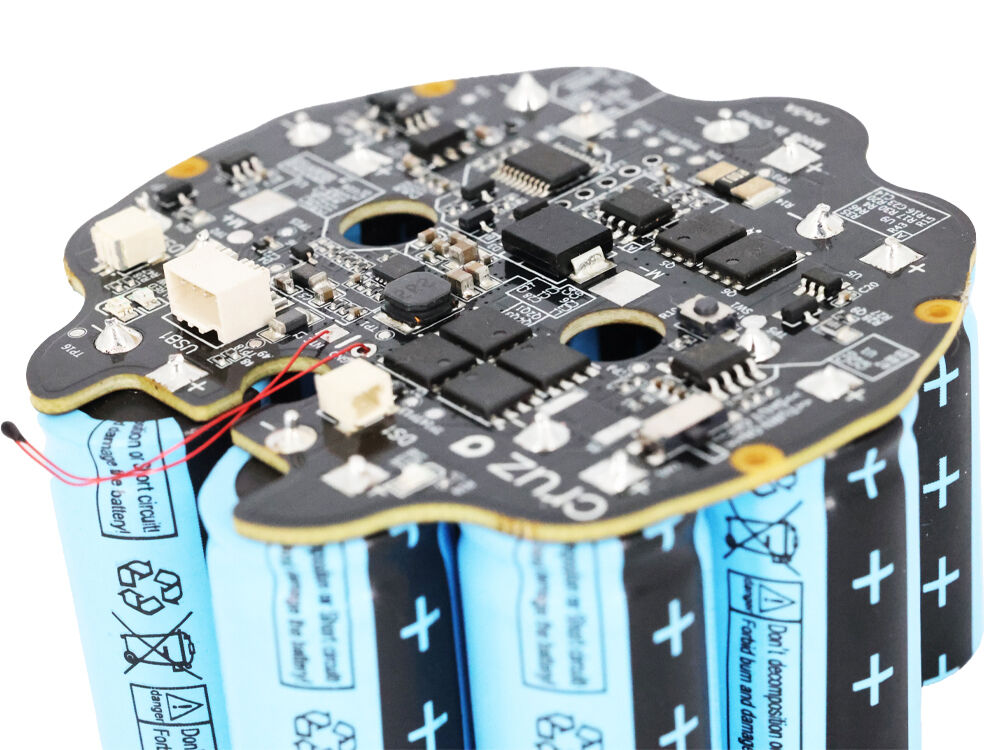

Fertigungsausrüstung bei Sierra Circuits

Ein zentraler Faktor zur Minimierung Verzögerungen in der PCB-Produktion und Bauteilfehlern ist der Einsatz fortschrittlicher, hochautomatisierter Fertigungsausrüstung. Die richtige Maschinentechnik – kombiniert mit Prozesskompetenz und DFM/DFA-abgestimmten Arbeitsabläufen – gewährleistet, dass jedes Design, sei es für schnelle Prototypenerstellung oder hochzuverlässige Serienfertigung, nach höchsten Qualitätsstandards hergestellt werden kann Zuverlässigkeit von Leiterplatten und Effizienz steigert.

In einem modernen PCB-Fertigungscampus

das Kingfield-Hauptquartier verfügt über eine vollständig integrierte 70.000 Quadratfuß große, hochmoderne Einrichtung , die die nächste Generation der Leiterplattenfertigung und -bestückung widerspiegelt. Das bedeutet Folgendes für Ihre Projekte:

Leiterplatten-Fertigungsbereich

- Mehrlagige Presslinien : Ermöglichen Mehrschicht- und HDI-Designs; enge Kontrolle über die Symmetrie des Schichtaufbaus und die Konsistenz des Kupfergewichts.

- Laserdirektabbildung (LDI): Präzise Spurbreite/Abstand bis hin zu mikroskopisch kleinen Strukturen, wodurch Ausschuss durch Ätz-/Fertigungsfehler reduziert wird.

- Automatisierte Bohr- und Fräsanlagen: Saubere und präzise Bohr- und Via-Definition (konform mit IPC-2221 und IPC-4761) für komplexe Via-in-Pad-, Blinde- und Buried-Via-Strukturen.

- AOI- und Röntgeninspektion: Inline-Kontrollen gewährleisten fehlerfreie Belichtung und erkennen innere Fehler bereits vor der Bestückung.

Leiterplattenbestückungsabteilung

- SMT-Bestückungslinien: Platzierungsgenauigkeit von ±0,1 mm, unterstützt kleinste Bauteile wie 0201 sowie große modulare Komponenten, entscheidend für den Erfolg von DFA.

- Bleifreie Reflow-Öfen: Mehrzonen-Regelung für konsistente Lötprofile (240–260 °C), geeignet für hochzuverlässige Anwendungen (Medizintechnik, Luft- und Raumfahrt, Automobil).

- Roboterbasiertes Löten: Eingesetzt für Spezialbauteile und Hochgeschwindigkeits-Serienläufe, liefert gleichmäßige Lötverbindungen und reduziert menschliche Fehler.

- Automatische optische Inspektion (AOI): Die Echtzeitüberwachung nach jedem Montageschritt erkennt fehlerhafte Bauteilplatzierungen, Orientierungsfehler und kalte Lötstellen – wodurch die meisten Fehler bereits vor dem abschließenden Test ausgeschlossen werden.

- Röntgeninspektion für BGAs: Ermöglicht eine zerstörungsfreie Qualitätskontrolle für verdeckte Lötstellen bei fortschrittlichen Gehäusen.

- Konformbeschichtung und selektive Reinigungssysteme: Für Leiterplatten, die in rauen Umgebungen eingesetzt werden, bieten sie zusätzlichen Schutz und erfüllen Zuverlässigkeitsanforderungen für Automotive-, Industrie- und IoT-Anwendungen.

Fabrikanalyse und Qualitätsverfolgung

- ERP-integrierte Rückverfolgbarkeit: Jede Leiterplatte wird nach Charge, Prozessschritt und Bediener verfolgt, um eine schnelle Ursachenanalyse und eine lückenlose COC-Dokumentation sicherzustellen.

- Datenbasierte Prozessoptimierung: Gerätelogs und QA-Statistiken ermöglichen kontinuierliche Verbesserungen und helfen dabei, Fehlermuster über mehrere Produktlinien hinweg zu erkennen und zu beseitigen.

- Virtuelle Fabrikführungen und Design-Unterstützung: Sierra Circuits bietet virtuelle und persönliche Führungen, die Echtzeit-Kennzahlen aus der Fertigung anzeigen und wichtige DFM/DFA-Prüfungen in der Praxis verdeutlichen.

Warum Ausrüstung für PCB DFM/DFA wichtig ist

"Unabhängig von der Stärke Ihrer Konstruktion entstehen die besten Ergebnisse dort, wo fortschrittliche Ausrüstung und DFM-konforme Designs zusammenkommen. Nur so lassen sich vermeidbare Fehler eliminieren, die Erstversuch-Ausbeute steigern und Marktvorgaben regelmäßig unterbieten." — Leiter der Fertigungstechnologie, Sierra Circuits

Schnellwechsel-Fähigkeiten: Die neuesten Bestückungs-, AOI- und Prozessautomatisierungssysteme ermöglichen nahtlose Abläufe von Prototyp bis Produktion. Selbst hochkomplexe Leiterplatten – wie sie in Luft- und Raumfahrt, Verteidigung oder im sich schnell wandelnden Bereich der Unterhaltungselektronik eingesetzt werden – können innerhalb weniger Tage statt Wochen gefertigt und bestückt werden.

Fabrikausrüstungstabelle: Übersicht der Fähigkeiten

|

Ausrüstung/Anlage

|

Funktion

|

DFM/DFA-Vorteil

|

|

LDI-Exposition

|

Spurbildgebung

|

Reduziert Spurbreiten/Abstandsfehler

|

|

AOI (Fertigung/Bestückung)

|

Visuelle Inspektion

|

Frühe Fehlererkennung, DFM-Konformität

|

|

SMT Bestückautomat

|

Montage

|

Verarbeitet Feinraster/hohe Bauteildichte

|

|

Reflow-Öfen (Mehrzonen)

|

Löten

|

Optimierte, fehlerfreie Verbindungen (bleifrei)

|

|

Roboterbasiertes Löten

|

Montage/QC

|

Konsistente Verbindungen, besonders THT/unübliche Bauteile

|

|

Röntgenuntersuchung

|

Nichtzerstörend

|

Überprüft BGAs, versteckte/innere Defekte

|

|

Reinigung/Beschichtung

|

Endschutz

|

Gewährleistet Zuverlässigkeit für raue Einsatzbedingungen

|

|

Rückverfolgbarkeit/ERP

|

Alle Schritte

|

Vollständiges COC, Verantwortlichkeit, schnelle Anfragen

|

Lieferzeiten bis zu 1 Tag

Im heutigen hyperwettbewerbsintensiven Elektronikmarkt ist Geschwindigkeit genauso wichtig wie Qualität . Egal, ob Sie ein neues Gerät auf den Markt bringen, einen kritischen Prototyp weiterentwickeln oder in Serie gehen – schnelle und zuverlässige Lieferung ist ein entscheidender Wettbewerbsvorteil. Verzögerungen bei der Leiterplattenfertigung kosten mehr als nur Geld – sie können ganzen Märkten schnellere Konkurrenten überlassen.

Der Vorteil der Schnellfertigung

Schnellfertigungs-Leiterplatten – mit Fertigungszeiten ab 1 Tag für die Platinenfertigung und ab 5 Tagen für die komplette schlüsselfertige Montage – sind mittlerweile Standard im Silicon Valley und darüber hinaus. Diese Agilität ist nur möglich, wenn Ihr Design reibungslos durch die Fertigungslinie fließt, wobei DFM- und DFA-Methoden sicherstellen, dass es keine Engpässe gibt.

Wie kurze Durchlaufzeiten erreicht werden

- DFM/DFA-gerechte Designs: Jede Platine wird von Anfang an auf Herstellbarkeit und Montagebereitschaft überprüft. Das bedeutet keine iterativen Dateiprüfungen, fehlenden Informationen oder mehrdeutige Dokumentation, die die Produktion verlangsamen könnten.

- Automatisierte Dateiverarbeitung: Standardisierte Gerber-, ODB++/IPC-2581-, Bestückungs-, BOM- und Netzlistendateien werden direkt aus Ihren Design-Tools in die CAM-/ERP-Systeme des Fertigungspartners eingespeist.

- Lokale Lager- und Prozesssteuerung: Bei schlüsselfertigen Projekten werden die Beschaffung von Bauteilen, das Zusammenstellen der Sets und die Montage allesamt auf einem einzigen Gelände verwaltet, wodurch Verzögerungen reduziert werden, die bei Arbeitsabläufen mit mehreren Anbietern entstehen können.

- produktionskapazität rund um die Uhr: Moderne Leiterplattenfabriken arbeiten mit mehreren Schichten und nutzen automatisierte Inspektion und Bestückung, um die Durchlaufzeiten noch weiter zu verkürzen.

Typische Durchlaufzeittabelle

|

Produktionsschritt

|

Standard-Lieferzeit

|

Kurze Lieferzeit

|

|

PCB-Fertigung

|

4–7 Tage

|

1 Tag (Eilbearbeitung)

|

|

Bestückung (SMT/THT)

|

7–10 Tage

|

2–5 Tage

|

|

Funktionelle Prüfung

|

2–3 Tage

|

Am selben Tag / am nächsten Tag

|

|

Schlüsselfertige Lösung (Vollbestückte Platine)

|

2–3 Wochen

|

5–7 Tagen

|

Wie DFM und DFA schnellere Durchlaufzeiten ermöglichen

- Minimale Rückfragen: Vollständige Konstruktionspakete bedeuten keine kurzfristigen Fragen oder Verzögerungen durch Klärungsbedarf.

- Verminderte Ausschuss- und Nacharbeit: Weniger Fehler und eine höhere Erstprüf-Ausschussquote ermöglichen einen vollständig effizienten Produktionsablauf.

- Automatisierte Prüfung und Inspektion: Die neuesten AOI-, Röntgen- und ICT-Systeme ermöglichen eine schnelle Qualitätssicherung ohne manuelle Verzögerungen.

- Vollständige Dokumentation und Rückverfolgbarkeit: Vom COC bis hin zu ERP-verknüpften Chargenunterlagen – alles ist bereit für behördliche oder kundenseitige Audits, selbst bei hohen Geschwindigkeiten.

Fallbeispiel: Produktlaunch eines Start-ups

Ein Wearable-Tech-Unternehmen aus dem Silicon Valley benötigte funktionstüchtige Prototypen für einen entscheidenden Investorenpitch – innerhalb von vier Tagen. Indem sie DFM/DFA-verifizierte Dateien an einen lokalen Schnellfertigungspartner lieferten, erhielten sie rechtzeitig 10 vollständig bestückte, AOI-getestete und funktionale Leiterplatten. Ein konkurrierendes Team mit unvollständigen Fertigungsanweisungen und fehlender Stückliste verbrachte eine ganze Woche im Zustand der „technischen Änderung“, wodurch ihr Wettbewerbsvorteil verloren ging.

Angebot anfordern

Egal, ob Sie Prototypen erstellen oder für die Produktion skalieren, jetzt ein Angebot anfordern und einer Echtzeit-Angabe zur Durchlaufzeit von Sierra Circuits oder Ihrem bevorzugten Partner. Laden Sie Ihre DFM/DFA-verifizierten Dateien hoch und verfolgen Sie, wie Ihr Projekt in Rekordzeit von CAD zur fertigen Leiterplatte wird.

Lösungen nach Branchen

Die Herstellung von Leiterplatten (PCB) ist alles andere als ein universeller Prozess. Die Anforderungen an einen Prototyp für tragbare Elektronik unterscheiden sich vollständig von denen eines sicherheitskritischen medizinischen Geräts oder einer hochzuverlässigen Steuerplatine für die Luft- und Raumfahrt. DFM- und DFA-Richtlinien – zusammen mit branchenspezifischem Know-how des Herstellers – sind die Grundpfeiler für Leiterplatten, die nicht nur funktionieren, sondern sich in ihren einzigartigen Umgebungen bewähren.

Branchen, die durch zuverlässige PCB-Produktion transformiert wurden

Schauen wir uns an, wie Branchenführer DFM/DFA und fortschrittliche PCB-Fertigungstechnologien nutzen, um hervorragende Ergebnisse in verschiedenen Bereichen zu erzielen:

1. Luft- und Raumfahrt & Verteidigung

- Strengste Anforderungen an Zuverlässigkeit, Rückverfolgbarkeit und Compliance.

- Alle Leiterplatten müssen den IPC-Klasse-3-Standards entsprechen und oft zusätzliche militärische bzw. luft- und raumfahrttechnische Normen erfüllen (AS9100D, ITAR, MIL-PRF-31032).

- Die Konstruktionen erfordern eine robuste Schichtaufbaustruktur, gesteuerte Impedanz, konforme Beschichtung und eine rückverfolgbare COC (Certificate of Conformance).

- Fortgeschrittene automatisierte Prüfverfahren (Röntgen, AOI, ICT) und vollständige Dokumentation sind für jede Charge zwingend vorgeschrieben.

2. Automobilindustrie

- Fokus: Sicherheit, Umweltbeständigkeit, schnelle NPI-Zyklen.

- Muss die funktionale Sicherheit nach ISO 26262 erfüllen und harten Bedingungen unter der Motorhaube (Vibration, thermisches Zyklen) standhalten.

- DFA-Richtlinien stellen robuste Lötverbindungen sicher (thermische Entlastung, ausreichende Paste) und automatisierte AOI-/Röntgenprüfung für fehlerfreie Montage.

- Panelisierung und Dokumentation müssen die Transparenz in der globalen Lieferkette unterstützen.

3. Consumer & Wearables

- Aggressiver Zeitplan bis zur Markteinführung, Kosteneffizienz und Miniaturisierung.

- DFM verkürzt die Zykluszeit von Prototyp zu Produktion, unterstützt HDI-/Starre-Flex-Konstruktion und minimiert Kosten durch optimierte Schichtaufbauten und effiziente Montageprozesse.

- DFA-Prüfungen stellen sicher, dass jede Taste, jeder Anschluss und jeder Mikrocontroller für eine nahtlose hochgeschwindigkeitsautomatisierte Montage positioniert ist.

4. Medizintechnik

- Uneingeschränkte Zuverlässigkeit, strenge Reinigung und Rückverfolgbarkeit.

- Erfordert rigorose Anwendung von DFM für Impedanzsteuerung, biokompatible Materialien und DFA für korrekte Reinigungs- und Beschichtungsvorgaben.

- Testpunkte, Netzanmeldelisten und COC-Verfahren sind aufgrund der FDA- und ISO-13485-Anforderungen nicht verhandelbar.

5. Industrie und IoT

- Anforderungen: Langlebigkeit, Skalierbarkeit und robustes Design.

- DFM-Regeln für kontrollierte Impedanz, Via-Schutz und widerstandsfähige Lötstopplacke werden mit DFA-Maßnahmen (Beschichtung, Reinigung, Test) kombiniert, um hohe Verfügbarkeitsziele zu erreichen.

- Fortgeschrittene Prozesssteuerung und ERP-gestützte Rückverfolgbarkeit gewährleisten die vollständige Einhaltung von Vorschriften und unterstützen Upgrades/Varianten mit minimaler Verzögerung.

6. Universitäten und Forschung

- Geschwindigkeit und Flexibilität sind besonders wichtig, bei sich weiterentwickelnden Designs und knappen Budgets.

- Schnell verfügbare, DFM-gestützte Prototypen und Dokumentationvorlagen ermöglichen es akademischen Teams, schneller zu experimentieren, zu lernen und zu publizieren.

- Der Zugang zu Online-Tools, Simulationsassistenten und standardisierten Checklisten reduziert die Einarbeitungszeit und hilft Studierenden, typische Fehler zu vermeiden.

Tabelle der Anwendungen in der Industrie

|

Branche

|

Wesentliche DFM/DFA-Schwerpunkte

|

Konformität/Standards

|

|

Luft-/und Raumfahrt/Verteidigung

|

Stapelungssymmetrie, Rückverfolgbarkeit, COC, erweiterte AOI

|

IPC Class 3, AS9100D, ITAR

|

|

Automobilindustrie

|

Robuste Verbindungen, vibrationsfest, schnelle Prüfung

|

ISO 26262, ISO/TS 16949

|

|

Consumer/Tragbare Geräte

|

Miniaturisierung, Panelisierung, Kosteneffizienz

|

IPC Class 2, RoHS

|

|

Medizintechnik

|

Reinigung, Zugang zu Testpunkten, Biokompatibilität

|

ISO 13485, FDA 21 CFR 820

|

|

Industrie/IoT

|

Umweltschutz, Langlebigkeit, Rückverfolgbarkeit

|

RoHS, REACH, UL

|

|

Universität/Forschung

|

Schnelligkeit beim Prototyping, Lernwerkzeuge, Dokumentenvorlagen

|

IPC-2221, schnelle DFM-Prüfung

|

Fazit: Stärken Sie Ihren PCB-Prozess – mit DFM, DFA und Partnerschaft

In der sich ständig beschleunigenden Welt der fortschrittlichen Elektronik Verursachen Verzögerungen in der Leiterplattenfertigung und Montagefehler nicht nur technische Probleme – sie sind geschäftliche Risiken . Wie in diesem Leitfaden detailliert beschrieben, lassen sich die Ursachen für verpasste Termine, Nacharbeit und Ausschuss fast immer auf vermeidbare Fehler zurückführen DFM-Fehler und DFA-Fehlern jeder Fehler – sei es eine falsche Schichtaufbau-Konfiguration, ein mehrdeutiger Lackschriftzug oder ein fehlender Prüfpunkt – kann Sie Wochen, Budget oder sogar eine Produktlancierung kosten.

Was die besten PCB-Teams und -Hersteller der Branche auszeichnet, ist eine konsequente Hingabe zu Design für die Fertigung und Konstruktion für Montage —nicht als nachträgliche Überlegungen, sondern als zentrale, proaktive Konstruktionsdisziplinen. Wenn Sie DFM- und DFA-Richtlinien in jeder Phase integrieren, stärken Sie Ihren gesamten Entwicklungsprozess, um:

- Kostenintensive Iterationen zu reduzieren indem Sie PCB-Konstruktionsfehler erkennen, bevor sie die Fertigung erreichen.

- Die Markteinführungszeit zu beschleunigen —nahtlos vom Prototypen in die Produktion übergehen, selbst bei anspruchsvollen Zeitvorgaben.

- Die höchsten Standards für Zuverlässigkeit und Qualität von Leiterplatten beizubehalten über alle Branchen hinweg, von der Luft- und Raumfahrt bis hin zum vernetzten Verbraucherelektronikbereich.

- Kosten zu optimieren , da optimierte Prozesse und weniger Fehler zu weniger Ausschuss, geringerem Arbeitsaufwand und höherer Ausbeute führen.

- Aufbau langfristiger Partnerschaften mit Fertigungsteams, die zu Stakeholdern Ihres Projekterfolgs werden.

Ihre nächsten Schritte für den Erfolg bei der Leiterplattenfertigung

Laden Sie unsere DFM- und DFA-Handbücher herunter Sofort umsetzbare DFM/DFA-Checklisten, Fehlerbehebungsanleitungen und praktische Referenzen nach IPC-Standard – alle darauf ausgelegt, Risiken in Ihrem nächsten Leiterplattendesign zu minimieren.

Nutzen Sie branchenführende Tools und Arbeitsabläufe Wählen Sie eine Leiterplattendesign-Software (z. B. Altium Designer, OrCAD) mit integrierten DFM/DFA-Prüfungen und stellen Sie stets sicher, dass Ihre Ausgabedateien im vom Hersteller bevorzugten Format vorliegen.

Schaffen Sie offene Kommunikationskanäle Binden Sie Ihren Hersteller frühzeitig in die Konstruktionsphase ein. Regelmäßige Design-Reviews, Freigaben der Vorab-Stapelstrukturen und gemeinsame Dokumentationsplattformen verhindern unerwartete Probleme und sparen Zeit.

Entwickeln Sie eine kontinuierliche Verbesserungskultur Dokumentieren Sie Erkenntnisse aus jeder Fertigungsrunde. Aktualisieren Sie Ihre internen Checklisten, archivieren Sie Fertigungs- und Montagehinweise und schließen Sie Feedbackschleifen mit Ihren Partnern – unter Anwendung eines PDCA-(Plan-Do-Check-Act)-Ansatzes zur kontinuierlichen Steigerung von Ausschussrate und Effizienz.

Bereit für eine schnellere und zuverlässigere Leiterplattenfertigung?

Egal, ob Sie ein innovatives Startup oder ein erfahrener Industrieakteur sind: Die zentrale Berücksichtigung von DFM und DFA in Ihrem Prozess ist der effektivste Weg, um fehler zu reduzieren, die Montage zu beschleunigen und erfolgreich zu skalieren . Arbeiten Sie mit einem bewährten, technologieorientierten Hersteller wie Sierra Circuits oder ProtoExpress zusammen —und gehen Sie mit Sicherheit vom Design-Freeze bis zur Markteinführung.

Häufig gestellte Fragen: DFM, DFA und die Vermeidung von Verzögerungen in der Leiterplattenproduktion

1. Was ist der Unterschied zwischen DFM und DFA, und warum sind sie wichtig?

Dfm (Design for Manufacturing) konzentriert sich darauf, das Layout und die Dokumentation Ihrer Leiterplatte so zu optimieren, dass die Fertigung – Ätzen, Bohren, Beschichten, Fräsen – schnell, korrekt und im großen Maßstab erfolgen kann. DFA (Design for Assembly) stellt sicher, dass Ihre Platine reibungslos durch die Phasen Bestückung, Lötung, Inspektion und Test läuft, mit minimalem Risiko von Fehlern oder Nacharbeit während der Leiterplattenbestückung.

2. Welche klassischen DFM- und DFA-Fehler führen zu Verzögerungen oder Defekten?

- Unvollständige Stack-Up-Dokumentation (z. B. fehlende Kupfergewichte oder Plattierungsstärken).

- Verstoß gegen Spurbreiten- und Abstandsanforderungen, insbesondere bei Leistungs-/Hochgeschwindigkeitsleitungen.

- Verwendung mehrdeutiger oder inkonsistenter Gerber-Dateien und Fertigungshinweise.

- Schlechte Lötstopplackgestaltung (Lötlacköffnungen zu groß/klein, fehlendes Via-Tenting).

- Falsche oder nicht übereinstimmende Bauteileumrisse und Positionsbezeichnungen in den Bestückungsdateien.

- Fehlender Zugang zu Prüfpunkten, fehlende Netzlisten oder unvollständige Stücklisten.

3. Woher weiß ich, ob mein Leiterplattendesign DFM-konform ist?

- Überprüfen Sie alle Stack-Up-, Spur- und Via-Regeln anhand der IPC-Standards (IPC-2221, IPC-2152, IPC-4761 usw.).

- Stellen Sie sicher, dass Gerber-, NC-Bohr-, Stücklisten- und Bestückungsdateien aktuell, konsistent sind und herstellerfreundliche Benennungen verwenden.

- Führen Sie Ihr Design mit DFM-Werkzeugen in Ihrer CAD-Software aus, oder bitten Sie Ihren Leiterplattenhersteller um eine kostenlose DFM-Prüfung.

4. Welche Dokumente sollte ich immer mit meiner Leiterplattenbestellung einreichen?

|

Pflichtdatei

|

Zweck

|

|

Gerber RS-274X / ODB++

|

Bilddaten/Ebenendaten für die Fertigung

|

|

NC-Bohrdatei

|

Anzahl und Spezifikation von Bohrungen/Löchern und Vias

|

|

Schichtaufbaudarstellung

|

Referenz für Schichtmaterial und -dicke

|

|

Detaillierte Stückliste (BOM)

|

Korrekte Beschaffung und Lebenszyklusverfolgung

|

|

Pick-and-Place-Datei

|

Automatisierte Montagemaschinenführung

|

|

Netzliste (IPC-D-356A)

|

Elektrische Verbindungen testen und verifizieren

|

|

Fertigungsanmerkungen

|

Oberfläche, Toleranz und Prozessanforderungen

|

|

Mechanische/Courtyard-Ebenen

|

Fräs-, Schlitz- und Randabstandsangaben

|

5. Wie helfen DFM- und DFA-Maßnahmen dabei, meine Markteinführungszeit zu verkürzen?

Indem sie Mehrdeutigkeiten beseitigen und sicherstellen, dass Ihr Design von Anfang an herstellbar ist, vermeiden Sie kurzfristige Konstruktionsänderungen, wiederholte Rückfragen und unbeabsichtigte Verzögerungen sowohl in der Fertigung als auch in der Bestückung. Dies ermöglicht es schnellere Prototypenerstellung, zuverlässige Kurzläufe und die Fähigkeit, schnell umzusteigen, wenn sich Anforderungen ändern .

Top-Nachrichten

Top-Nachrichten