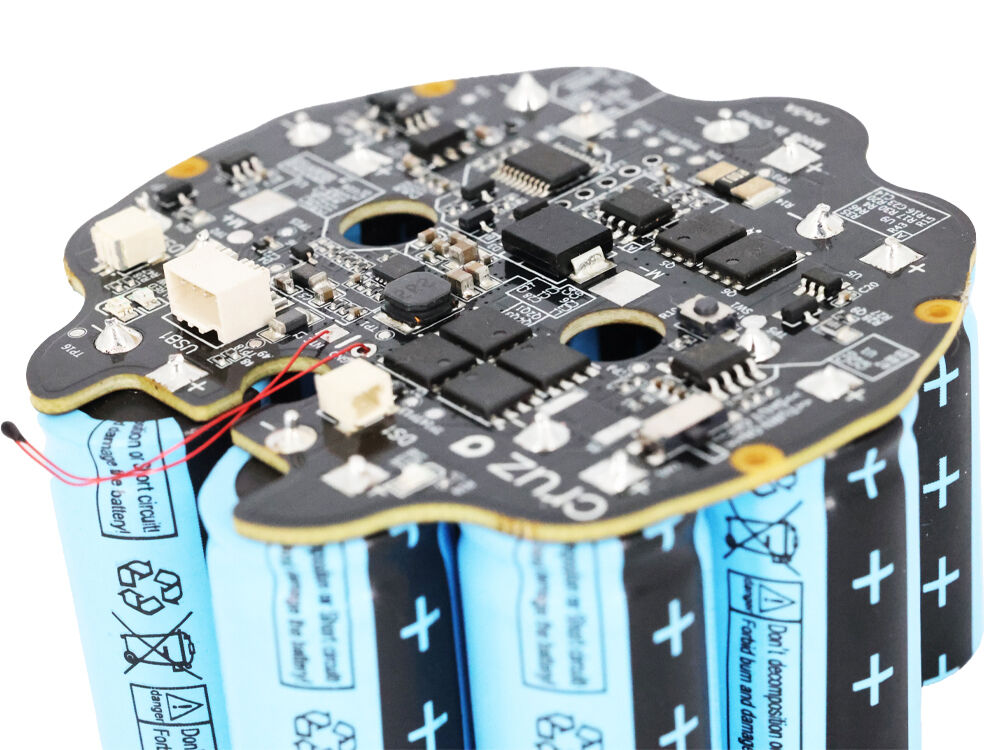

Papan litar bercetak (PCB) adalah jantung kepada elektronik moden—memberi kuasa kepada segala-galanya daripada peranti pengguna hingga peranti perubatan kritikal keselamatan dan kenderaan autonomi. Namun, walaupun begitu meluasnya penggunaan dan kecanggihan proses pembuatan PCB hari ini, Kelewatan pengeluaran PCB adalah halangan yang terlalu kerap berlaku. Kehilangan masa akibat kelewatan ini bukan sahaja memakan masa, malah boleh menggagalkan pelancaran produk, membazirkan bajet, dan juga merosakkan kebolehpercayaan keseluruhan produk.

Dalam pasaran teknologi yang sangat kompetitif, memastikan pembuatan dan pemasangan PCB yang pantas serta bebas daripada kecacatan adalah penting. Dan dalam hampir setiap analisis punca utama, masalah besar yang berlaku sebenarnya disebabkan oleh dua faktor utama: Kesilapan DFM (Reka Bentuk untuk Pembuatan) dan Kesilapan DFA (Reka Bentuk untuk Pemasangan) . Walaupun terdapat banyak sumber rujukan mengenai panduan rekabentuk PCB dan amalan terbaik, beberapa kesilapan berulang tetap menjejaskan walaupun jurutera yang berpengalaman. Kesilapan ini sering kelihatan ringkas di permukaan, tetapi impaknya sangat besar: menyebabkan percetakan semula, merisaukan hasil pengeluaran, dan mencipta kebuntuan yang memberi kesan kepada rantaian bekalan.

Artikel terperinci ini akan meneroka:

Sama ada anda merupakan permulaan perkakasan yang bertujuan untuk peralihan pantas dari prototaip ke pengeluaran atau pasukan kejuruteraan yang telah ditubuhkan yang ingin mengoptimumkan hasil perakitan anda, menguasai Rekabentuk untuk Pembuatan (DFM) dan Reka bentuk untuk perakitan (DFA) adalah jalan terpantas anda ke arah kecekapan.

Rekabentuk untuk Pembuatan (DFM) adalah tulang belakang pembuatan PCB yang boleh dipercayai dan berkos efisien. Namun, walaupun di fabrikasi kelas dunia sekalipun, kesilapan DFM yang berulang tetap menjadi sumber utama Kesilapan DFM adalah sumber utama Kelewatan pengeluaran PCB kesilapan rekabentuk ini mungkin kelihatan kecil pada skrin CAD, tetapi ia boleh menjadi punca kebuntuan mahal, sisa atau reka bentuk semula di lantai kilang. Pakar fabrikasi kami telah mengumpulkan perangkap yang paling kerap berlaku—dan lebih penting lagi, cara untuk mengelakkannya.

Susunan PCB yang tidak seimbang atau ditentukan dengan kurang baik adalah resepi kepada bencana, terutamanya dalam pembinaan berbilang lapisan. Isu seperti maklumat ketebalan dielektrik yang hilang , tidak ditentukan berat tembaga , susun atur tidak simetri , kekurangan kawalan impedans, dan seruan yang kabur untuk ketebalan pelapisan atau topeng solder sering membawa kepada:

Amalan Terbaik untuk Reka Bentuk Susunan PCB:

|

Anjakan |

Penerangan |

Rujukan |

|

Tentukan setiap lapisan |

Tentukan berat tembaga, ketebalan dielektrik, dan jenis bagi setiap lapisan |

IPC-2221, IPC-4101 |

|

Kekalkan kesimetrian |

Cerminkan susunan di atas/di bawah teras pusat—mengurangkan tekanan mekanikal |

|

|

Sertakan semua lapisan penyelesaian |

Ambil kira plating, topeng solder, dan lapisan permukaan dalam ketebalan keseluruhan |

IPC-4552 |

|

Dokumen lapisan impedans |

Gunakan nota eksplisit untuk rangkaian kawalan impedans |

IPC-2141, 2221 |

|

Arkibkan panggilan susunan lapisan |

Kekalkan revisi dan perubahan sejarah supaya mudah diakses |

|

Reka bentuk laluan kelihatan mudah, tetapi pelanggaran lebar laluan dan jarak antara kesilapan DFM yang paling kerap berlaku. Kesilapan biasa termasuk:

Senarai Semak Reka Bentuk Jejak:

Jadual: Kesilapan Lazim Pembumian Surutan dan Pencegahan

|

Ralat DFM |

Akibat |

Penyelesaian |

|

Jejak terlalu hampir dengan tepi |

Kuprum terdedah oleh peraut, risiko litar pintas |

>20 mil dari tepi papan (garis panduan pembuatan) |

|

Tiada titisan di via/pad |

Pembentukan retak, kehilangan hasil |

Tambahkan bentuk titisan untuk kebolehpercayaan |

|

Pasangan berbeza tidak konsisten |

Kegagalan SI (Integriti Isyarat) |

Nyatakan secara eksplisit jarak yang sepadan |

|

Jarak di bawah IPC-2152 |

Ukiran/perkongsian/hasil ujian rendah |

Tingkatkan jarak mengikut IPC-2152 |

Via adalah penting untuk PCB berbilang lapisan moden, tetapi pilihan reka bentuk yang tidak sesuai menyebabkan cabaran DFM yang kritikal:

Peraturan Reka Bentuk Via untuk Kebolehsahtaan Pengeluaran:

Lapisan topeng solder adalah punca klasik kelewatan pengeluaran saat akhir dan kesilapan pemasangan:

Meninggalkan siap permukaan tidak ditentukan, memilih pilihan yang tidak serasi, atau gagal menentukan urutan boleh menghentikan pengeluaran sepenuhnya. Begitu juga, kabur atau tiada ciri-ciri mekanikal dalam dokumen anda boleh menghalang pelaksanaan V-score, takik pemisah, atau alur mesin dengan betul.

Data produksi yang tidak lengkap atau tidak sepadan adalah agak biasa. Kesilapan DFM yang kerap termasuk:

Amalan Terbaik Nota Pemfabrikan PCB:

Salah satu punca yang sering diremehkan bagi kelewatan pengeluaran PCB adalah penghantaran fail pengeluaran yang tidak lengkap atau bercanggah . Walaupun dengan skematik dan stack-up yang sempurna, kelalaian kecil dalam dokumentasi boleh menyebabkan kesesakan yang menghentikan pesanan semasa kejuruteraan CAM. Isu seperti Ketidakpadanan Gerber dan drill , kekaburan dalam nota fabrikasi , rampasan revisi , dan ketiadaan format penting (contoh: senarai bersih IPC-D-356A, ODB++, atau IPC-2581) memaksa pengesahan semula yang mengambil masa serta kerja semula.

Kesalahan DFM Lazim dengan Fail Pengeluaran:

Amalan Terbaik untuk Dokumentasi Pengeluaran PCB:

|

Anjakan |

Tindakan |

Rujukan |

|

Semak silang semua eksport |

Buka Gerber, NC Drill, dan lukisan fab dalam penampil (GC-Prevue, Altium, dll.) |

QA Dalaman |

|

Gunakan penamaan yang konsisten & kawalan revisi |

Kumpulkan fail pengeluaran dalam folder piawai yang diberi tarikh |

Pengurusan versi automatik |

|

Sertakan semua format yang diperlukan |

Minimum: Gerber RS-274X, NC Drill, Lukisan Fabrikasi & Pemasangan, susunan lapisan, BOM, pick-and-place, netlist (IPC-D-356A atau ODB++/IPC-2581) |

Format yang mematuhi IPC |

|

Sediakan nota fabrikasi yang jelas |

Dokumen jenis siap, butiran impedans, kekangan mekanikal, dan keperluan ujian |

IPC-2221, IPC-D-356A, keupayaan pengilang |

|

Lampirkan sejarah revisi |

Masukkan log perubahan ringkas atau jadual revisi bersama dokumen |

Dokumentasi ISO 9001:2015 |

|

Sahkan data sepadan dengan maksud rekabentuk |

Sahkan output CAD papan litar bercetak (PCB) sebenar sepadan dengan rekabentuk asal—termasuk kutub dan orientasi |

Pengesahan tanda tangan pereka sebelum dikeluarkan |

Jadual: Senarai Semak Dokumentasi PCB Penting

|

Fail/Dokumen |

Wajib? |

Butiran Utama untuk Disahkan |

|

Gerber RS-274X |

Ya |

Sejajar dengan nota fabrikasi, boleh disimpan/disemak semula |

|

NC Drill |

Ya |

Saiz gerudi sepadan dengan pad/via stack-up |

|

BOM |

Ya |

Nombor bahagian terkini, pembekal, maklumat kitar hidup |

|

Ambil-dan-Letak |

Ya |

Koordinat penempatan, refdes, putaran |

|

Lukisan Fabrikasi |

Ya |

Nama net, susunan berlapis, dimensi, kemasan |

|

IPC-D-356A / ODB++ |

Sangat |

Untuk ujian elektrik dan semakan silang |

|

Lapisan Mekanikal |

Mengikut keperluan |

Alur, lubang potong, skor-V, ciri istimewa |

|

Lakaran Pemasangan |

Sangat |

Lokasi, label, semua orientasi komponen |

|

Sejarah Revisi |

Amalan Terbaik. |

Jejak penuh untuk perubahan |

DFM bukan sekadar semakan satu kali tetapi disiplin yang membina keberkesanan jangka panjang Kebolehpercayaan PCB dan kelebihan perniagaan. Sierra Circuits telah mendokumentasikan projek-projek di mana kesilapan DFM seperti pelanggaran gelang annular via atau dokumentasi susunan yang tidak betul mengurangkan masa pusingan prototaip kepada pengeluaran sebanyak 30% . Bagi pembuatan PCB pantas, penjimatan sedemikian boleh menjadi perbezaan antara penghantaran terpantas dalam kelasnya dan ketinggalan berbanding pesaing yang lebih cekap.

Sedia untuk meminimumkan kelewatan pengeluaran PCB anda dan memastikan setiap pesanan boleh dikeluarkan dengan betul pada percubaan pertama? Muat turun [Buku Panduan Reka Bentuk untuk Pengeluaran] percuma kami —dipenuhi senarai semak DFM terperinci, contoh dunia sebenar, dan panduan IPC terkini. Elakkan kesilapan DFM klasik dan berdayakan pasukan reka bentuk anda untuk membina dengan yakin!

Sementara Rekabentuk untuk Pembuatan (DFM) menangani cara papan litar anda dibina, Reka bentuk untuk perakitan (DFA) memberi tumpuan kepada sejauh mana papan PCB anda boleh dipasang dengan mudah, tepat, dan boleh dipercayai—sama ada dalam pusingan prototaip atau pengeluaran besar-besaran. Mengabaikan Kesilapan DFA menyebabkan kerja semula yang mahal, produk yang prestasinya rendah, dan masalah yang berterusan Kelewatan pengeluaran PCB . Berdasarkan pengalaman pembuatan sebenar di kemudahan terkemuka seperti Sierra Circuits dan ProtoExpress, berikut adalah kesilapan pemasangan yang paling kerap ditemui—dan cara memastikan papan anda melepasi perakitan PCB dengan jayanya pada percubaan pertama.

Walaupun dengan skematik dan susunan yang ideal, penempatan komponen yang salah atau kesilapan tapak komponen boleh melumpuhkan proses perakitan. Antara perangkap DFA yang biasa ialah:

Amalan Terbaik untuk DFA dalam Tapak Komponen dan Penempatan:

|

Ralat DFA |

Impak |

Penyelesaian / Piawaian |

|

Tapak kaki tidak sepadan |

Komponen tidak muat, kecacatan pematerian |

Tapak kaki mengikut IPC-7351; semakan BOM |

|

Komponen terlalu rapat |

Pengambilan dan peletakan tertangguh, lompatan pendek |

ulasan jarak ≥0.5mm |

|

Penunjuk reka bentuk tiada |

Risiko peletakan salah atau komponen yang salah |

Enakkan pada lapisan silkskrin |

|

Kutub terbalik |

Kegagalan pemasangan atau ujian secara besar-besaran |

Tandakan pada lakaran silkskrin/pemasangan |

|

Fiducial tiada |

Ralat penyelarasan mesin |

3 di setiap sisi, pad tembaga dengan pelindung |

Mengabaikan aspek terma profil pematrian semula pemasangan kegagalan mematuhi keperluan adalah antara punca utama kecacatan pematerian dan kehilangan hasil, terutamanya dengan pakej miniatur yang moden.

Garispanduan DFA untuk Profil Terma/Pemasangan:

|

Isu Termal |

Kesilapan DFA |

Penyelesaian |

|

Tombstoning |

Tapak kaki/pad solder tidak seimbang |

Saiz pad tengah, padanan geometri yang rapat |

|

Bayangan |

Jiran tinggi menghalang IR |

Kumpulkan komponen dengan ketinggian yang serupa |

|

Penurunan reflow |

Bahagian bawah berat |

Gunakan gam atau hadkan komponen besar ke bahagian atas |

Moden Penyambungan smt bergantung pada acuan pasta solder yang dikawal dengan tepat dan fluks yang sesuai. Namun, kami melihat banyak pakej rekabentuk:

Pembersihan selepas pemasangan dan salutan pelindung adalah penting untuk Kebolehpercayaan PCB —terutamanya untuk aplikasi automotif, aerospace, dan industri. Kesilapan DFA di sini termasuk:

Kelewatan pengeluaran PCB dan kegagalan tidak hanya berlaku di kilang. Ralat pembelian, komponen usang, dan kurangnya ketelusuran semua menyumbang kepada kerja semula dan kualiti rendah. Kesilapan DFA biasa termasuk:

|

Isu DFA |

Impak |

Penyahbungan |

|

Komponen EOL |

Pusingan semula pada minit akhir |

Kajian BOM suku tahunan, dasar jangka panjang |

|

Tiada ketelusuran |

Panggilan balik atau kegagalan audit QA |

Anotasi COC, pengekodan bar, ID bersiri |

Sebuah pengilang robot mengalami kegagalan berselang-seli semasa pelancaran tahunan kepada pelanggan. Siasatan oleh pemasang mendedahkan dua kesilapan DFA yang berkaitan:

Kerana tiada pengesanan atau arahan pemasangan terkoordinasi, papan yang rosak tidak dikesan sehingga berlaku kegagalan ujian peringkat sistem. Dengan menambah tapak kaki mengikut IPC-7351, tandaan Pin 1 yang kelihatan, dan semakan kitaran hidup BOM setiap suku tahun, keluaran berikutnya mencapai hasil lebih daripada 99.8% dan menghapuskan isu kritikal di medan.

Mahukan panduan praktikal yang lebih banyak untuk mengelakkan kesilapan DFA biasa, mengoptimumkan proses pemasangan anda, dan mempercepatkan masa ke pasaran? Muat turun [Buku Panduan Reka Bentuk untuk Pemasangan] yang komprehensif ini untuk senarai semak DFA terperinci, penyelesaian masalah dunia sebenar, dan pandangan pakar yang boleh anda gunakan daripada prototaip hingga pengeluaran besar-besaran.

Reka Bentuk untuk Kebolehan Pengeluaran (DFM) adalah falsafah kejuruteraan dan set panduan praktikal yang bertujuan memastikan rekabentuk papan litar bercetak (PCB) anda bergerak lancar daripada susun atur digital kepada pembuatan dan perakitan fizikal. Dalam elektronik moden, DFM bukan sekadar "elok jika ada"—ia penting untuk mengurangkan ralat pembuatan PCB, meminimumkan kelewatan pengeluaran, dan mempercepatkan proses prototaip kepada pengeluaran .

Mereka bentuk gambarajah skematik hanyalah separuh daripada pertempuran. Jika susun atur PCB anda mengabaikan proses Pengilangan —daripada ukiran jejak kuprum, susunan lapisan, dan pengeposan panel kepada pemilihan kemasan permukaan dan pematerian perakitan—kemungkinan kelewatan yang mahal melambung tinggi.

Senario Biasa:

|

PRINSIP |

Kesan terhadap Kebolehpercayaan dan Hasil PCB |

|

Kelengkapan Dokumentasi |

Memastikan pasukan fabrikasi/perakitan mempunyai semua yang diperlukan—tiada teka-teki. |

|

Penjajaran Proses Pengeluaran |

Mengurangkan risiko ciri di luar julat toleransi, meningkatkan hasil. |

|

Niat Reka Bentuk yang Jelas |

Mencegah salah tafsir, keperluan yang terlepas, atau kelewatan. |

|

Toleransi Realistik |

Menyesuaikan spesifikasi PCC anda dengan realiti proses pengukiran, pengeboran, penyaduran, dan perakitan. |

Kawasan Bebas Tepi Biarkan ruang yang mencukupi dari ciri-ciri tembaga ke perimeter PCC (biasanya ≥20 mil) untuk mengelakkan tembaga terdedah dan risiko litar pintas semasa proses penyahpanelan.

Perangkap Asid Elakkan geometri sudut tajam (<90°) pada bucu tuangan tembaga—ini boleh menyebabkan ketidakkonsistenan dalam proses etching dan risiko keterbukaan/litar pintas.

Penempatan Komponen dan Kerumitan Penyambungan Permudahkan penyambungan isyarat dan kuasa, meminimumkan lapisan yang bertindih dan jejak impedans terkawal. Rasionalisasikan panelisasi anda untuk hasil keluaran terbaik.

Lebar Jejak dan Jarak Pemisahan Gunakan IPC-2152 untuk memilih lebar jejak berdasarkan beban arus dan kenaikan suhu yang dijangkakan. Patuhi peraturan jarak pemisahan minimum untuk pembuatan dan penebatan voltan tinggi.

Lapisan Solder dan Silkskrin Tentukan bukaan lapisan solder dengan sekurang-kurangnya jarak bebas 4 mil di sekeliling pad. Elakkan dakwat silkskrin daripada terkena pad untuk memastikan kebolehpercayaan sambungan solder yang baik.

Rekabentuk Via Dokumen semua jenis via dengan jelas (melalui, buta, terbenam). Nyatakan keperluan via diisi atau ditutup pada papan HDI atau BGA. Rujuk IPC-4761 untuk kaedah perlindungan via.

Pemilihan Siaran Permukaan Selaraskan siaran anda (ENIG, HASL, OSP, dll.) dengan keperluan fungsian (contohnya, pengikatan dawai, pematuhan RoHS) dan keupayaan perakitan.

Penyediaan Fail Pengeluaran Gunakan penamaan piawaian, sertakan semua output yang diperlukan (Gerber, latihan NC, susunan berlapis, BOM, IPC-2581/ODB++, senarai rangkaian).

Tidak semua perisian rekabentuk PCB secara automatik menguatkuasakan semakan DFM, itulah sebabnya ramai Kesilapan DFM merembes masuk. Alat utama (seperti Altium Designer, OrCAD, Mentor Graphics PADS, dan KiCAD sumber terbuka) menawarkan:

Mengoptimumkan susun atur PCB anda untuk kebolehdihasiladilaun adalah penting bagi mencegah kesilapan DFM dan ralat DFA yang menyebabkan kelewatan pengeluaran PCB. Lima strategi susun atur berikut telah terbukti merampingkan proses pembuatan dan pemasangan, meningkatkan kebolehpercayaan, hasil pengeluaran, dan struktur kos jangka panjang papan PCB anda.

Penempatan komponen yang betul adalah asas kepada papan PCB yang boleh dibina. Mengumpulkan komponen terlalu rapat, gagal mematuhi peraturan jarak, atau menempatkan peranti sensitif di kawasan tekanan tinggi akan mencabar jentera penempat secara automatik (pick-and-place) dan juga operator manusia. Penempatan yang buruk juga boleh menyebabkan pemeriksaan optik automatik (AOI) tidak berkesan, kadar kecacatan yang lebih tinggi, dan peningkatan kerja semula semasa pemasangan PCB.

Jadual: Penempatan Ideal berbanding Bermasalah

|

Isu Penempatan |

Kesan |

Strategi Pencegahan |

|

Kawasan komponen yang sesak |

Titik buta AOI, risiko kerja semula |

Gunakan kawasan halaman dan peraturan DFM |

|

Komponen tinggi di tepi |

Solder tidak lengkap, patah depanel |

Letakkan komponen tinggi di bahagian tengah |

|

Tiada ruang untuk probe ujian |

Kelewatan dalam pengujian dan penyahpepijat |

Tetapkan pad ujian yang mudah diakses |

Pengaturcaraan trek bukan sekadar menyambung dari Titik A ke Titik B. Pengaturcaraan yang buruk—sudut tajam, lebar trek tidak betul, jarak tidak konsisten—menyebabkan isu integriti isyarat, masalah pematerian, dan penyahpepijatan yang rumit. Lebar dan jarak trek secara langsung mempengaruhi hasil etika, kawalan galangan, dan prestasi kelajuan tinggi.

Menggunakan tuangan kuasa dan bumi secara agihan mengurangkan kejatuhan voltan, meningkatkan prestasi haba, dan meminimumkan EMI, iaitu sumber masalah kerap Kebolehpercayaan PCB yang dikeluhkan pada papan reka bentuk yang kurang baik.

Panelisasi yang cekap meningkatkan ketelusan dalam proses pembuatan dan pemasangan, manakala amalan depanelisasi yang buruk (seperti skor-V agresif tanpa kelegaan tembaga) boleh merosakkan jejak tepi atau mendedahkan tuangan bumi.

Jadual Contoh: Panduan Panelisasi

|

Pertimbangan |

Nilai tipikal |

Peraturan/Standard |

|

Kuprum min. ke V-score |

15 mils |

IPC-2221 |

|

Celah papan min. |

100 mils |

Spesifikasi pengilang |

|

Tab bagi setiap tepi |

2+ |

Skala pengeluaran |

Tidak kira sebaik mana reka bentuk skematik atau susun atur anda, dokumentasi yang lemah dan BOM yang tidak sepadan adalah antara punca utama kekeliruan dalam pembuatan dan lampauan jadual. Fail yang jelas dan konsisten mengurangkan soalan, mencegah penahanan bahan, mempercepatkan perolehan, dan mengurangkan masa dalam proses pemasangan PCB .

Satu pasukan penyelidik universiti pernah menyelamatkan keseluruhan semester—berminggu-minggu masa eksperimen—dengan mengadopsi senarai semak DFM/DFA pengilang untuk susun atur, penghantaran, dan dokumentasi. Kelompok prototaip pertama mereka lulus ulasan DFM dan AOI tanpa sebarang soalan, menunjukkan penjimatan masa yang boleh diukur dengan mengikuti lima strategi susun atur asas ini.

Melaksanakan amalan terbaik DFM (Reka Bentuk untuk Pengeluaran) bukan sahaja untuk mengelakkan kesilapan mahal—ia merupakan senjata rahsia untuk mengoptimumkan kecekapan, meningkatkan kualiti produk, dan memastikan jadual pengeluaran PCB anda berada di landasan yang betul. Apabila garis panduan DFM diintegrasikan ke dalam proses rekabentuk anda, bukan sahaja hasilan anda meningkat, malah anda turut memperoleh manfaat daripada komunikasi yang lebih lancar, penyelesaian masalah yang lebih mudah, dan kawalan kos yang lebih baik—semuanya sambil memastikan perkakasan anda boleh dipercayai sejak dari pembinaan pertama.

DFM mengubah rekabentuk PCB teori kepada papan fizikal yang kukuh, boleh diulang, dan pantas dihasilkan. Begini caranya:

Pengurangan Re-Spins dan Kerja Semula

Meminimumkan Kelewatan Pengeluaran

Hasil dan Kebolehpercayaan yang Dipertingkat

Perolehan dan Pemasangan yang Dimudahkan

Penskalaan Mudah dari Prototaip ke Pengeluaran Isi Padu

|

Faedah DFM |

Hasil yang Boleh Diukur |

TAKELEMBANG PERINDUSTRIAN |

|

Reka bentuk semula yang kurang |

pengurangan 30–50% dalam ECO |

Kaji selidik IPC & Lembah Silikon |

|

Hasil lulus pertama yang lebih tinggi |

>99.5% pada papan kompleks (>8 lapisan) |

Data pengeluar cepat-pusingan |

|

Masa ke Pasaran yang Lebih Cepat |

Penjimatan masa kitaran sehingga 30% |

Kajian kes Sierra Circuits |

|

Kadar semula/buang yang lebih rendah |

<1% bahan buangan dalam pembinaan berkualiti tinggi |

Kilang automotif/aeroangkasa |

|

Penyerahan NPI yang lebih lancar |

80% kurang langkah pengesahan fail |

Audit proses NPI |

Apabila tiba masanya untuk membawa rekabentuk daripada skematik digital kepada papan yang dipasang secara fizikal, Cacat pemasangan PCB boleh merosakkan berbulan-bulan kejuruteraan yang teliti, menyebabkan kelewatan yang mahal, dan menggugat kebolehpercayaan keseluruhan produk anda. Kegagalan ini bukan secara rawak; hampir sentiasa mempunyai punca asas dalam susun atur, dokumentasi, atau jurang proses—yang kebanyakannya boleh diselesaikan melalui panduan DFM dan DFA yang kukuh Panduan DFM dan DFA yang disematkan pada peringkat awal reka bentuk anda.

|

Jenis Kekurangan |

Gejala/Pengesanan |

Punca Asas Biasa |

|

Cacat pematerian |

Sambungan sejuk, jambatan, timah pematerian tidak mencukupi |

Pemendapan pasta yang kurang baik, tapak yang salah, pad tidak sejajar |

|

Keselarasan komponen yang salah |

Tidak berpusat, condong, putaran salah |

Tapak kaki tidak betul, kehilangan kutub, ralat AOI/Gerber |

|

Tombstoning |

Satu hujung komponen pasif terangkat |

Ketidakseimbangan haba, saiz pad tidak sepadan, pemanasan tidak sekata |

|

Masalah Topeng Solder |

Litar pintas, dedahan terbuka, pad tanpa topeng |

Gerber tidak betul, pertindihan topeng/pad, jarak selamat hilang |

|

Jurang Pengujian Pemasangan |

Liputan ujian tidak lengkap, kecuaian |

Titik ujian hilang/diletakkan dengan buruk, tiada senarai bersih, dokumen tidak jelas |

|

Sambungan Terbuka/Tidak Lengkap |

Kesan “terbuka” secara visual, kegagalan ujian |

Resap via-dalam-pad, solder sejuk akibat kehilangan pad pelepasan |

Apabila kerumitan meningkat—seperti BGAs, QFP berjarak halus, atau papan dua sisi yang padat—pemeriksaan dan ujian automatik menjadi fokus utama:

Seorang pengilang peranti perubatan menolak satu kelompok setelah ujian mendapati 3% papan dengan sambungan solder "laten"—sempurna dalam AOI tetapi gagal selepas kitaran haba. Analisis pasca-kegagalan mengenal pasti ralat DFM: kelegaan topeng solder yang tidak mencukupi menyebabkan penyerapan berubah-ubah dan sambungan lemah di bawah beban haba. Dengan semakan DFM yang dikemas kini dan peraturan DFA yang lebih ketat, penghasilan masa depan mencapai sifar kegagalan selepas ujian kebolehpercayaan yang luas.

|

Kecacatan |

Garispanduan DFM/DFA |

Langkah kawalan kualiti |

|

Sambungan sejuk/tersambung |

Pad IPC-7351, lapisan pasta betul, semakan DFM |

AOI, pemeriksaan visual |

|

Komponen tersalah letak |

Penandaan refdes, penandaan kutub, ulasan susun atur DFA |

Pengesahan pengambilan-dan-pemasangan |

|

Tombstoning |

Pad seimbang, pelepasan haba, ulasan awal DFA |

Simulasi profil, AOI |

|

Ralat topeng solder |

Peraturan topeng IPC-2221, pemeriksaan Gerber DFM |

AOI, pemeriksaan fizikal |

|

Kelepasan ujian |

Titik ujian setiap jaring, senarai jaring disertakan |

Pengujian dalam litar/fungsian |

Satu faktor utama dalam meminimumkan Kelewatan pengeluaran PCB dan kecacatan pemasangan adalah penggunaan peralatan pengeluaran yang maju dan sangat berautomasi. Mesin yang tepat—dipadankan dengan kepakaran proses dan aliran kerja selaras DFM/DFA—memastikan setiap rekabentuk, sama ada untuk prototaip pantas atau pengeluaran pukal berkebolehpercayaan tinggi, dapat dibina mengikut piawaian tertinggi Kebolehpercayaan PCB dan kecekapan.

ibu pejabat kingfield menampilkan kemudahan seluas 70,000 kaki persegi yang terpadu sepenuhnya, 70,000-square-foot, kemudahan terkini , mencerminkan generasi seterusnya operasi fabrikasi dan pemasangan PCB. Inilah yang dimaksudkan untuk projek anda:

"Tidak kira betapa kukuhnya kejuruteraan anda, hasil terbaik dicapai apabila peralatan canggih dan rekabentuk yang mematuhi DFM bersatu. Hanya dengan cara inilah kesilapan yang boleh dicegah dapat dielakkan, hasil lulus pertama ditingkatkan, dan tempoh pasaran sentiasa dapat dikalahkan." — Pengarah Teknologi Pembuatan, Sierra Circuits

Keupayaan Giliran Pantas: Alat terkini pemasangan permukaan, AOI, dan pengautomatan proses membolehkan aliran prototaip ke pengeluaran penuh. Malah PCB berkompleksitas tinggi—seperti yang digunakan dalam aerospace, pertahanan, atau elektronik pengguna yang cepat berubah—boleh dikilangkan dan dipasang dengan tempoh penghantaran yang dikira dalam hari, bukan minggu.

|

Peralatan/Sistem |

Fungsi |

Faedah DFM/DFA |

|

Pendedahan LDI |

Imej jejak |

Mengurangkan ralat lebar/jeda jejak |

|

AOI (pembuatan/pemasangan) |

Pemeriksaan visual |

Pengesanan awal kecacatan, pematuhan DFM |

|

SMT Pick-and-Place |

Pemasangan |

Mengendalikan komponen jejakan halus/ketumpatan tinggi |

|

Kilang Reflow (berbilang zon) |

Penyolderan |

Sambungan dioptimumkan, bebas kecacatan (tanpa plumbum) |

|

Penyolderan Robotik |

Pemasangan/QC |

Sambungan konsisten, terutamanya THT/bahagian ganjil |

|

Pemeriksaan X-Ray |

Tidak merosakkan |

Mengesahkan BGAs, kecacatan tersembunyi/dalaman |

|

Pembersihan/Salutan |

Perlindungan akhir |

Memastikan kebolehpercayaan untuk penggunaan kasar |

|

Boleh dilacak/ERP |

Semua langkah |

COC penuh, akauntabiliti, pertanyaan pantas |

Dalam pasaran elektronik yang sangat kompetitif pada hari ini, kelajuan sama pentingnya dengan kualiti . Sama ada anda melancarkan peranti baharu, membuat penyempurnaan prototaip penting, atau bergerak ke pengeluaran volum, penghantaran yang pantas dan boleh dipercayai merupakan pembeza utama. Kelewatan pengeluaran PCB bukan sahaja menelan kos kewangan—malah boleh menyerahkan seluruh pasaran kepada pesaing yang lebih cepat.

PCB pusingan pantas —dengan masa pusingan secepat 1 hari untuk pembuatan dan serendah 5 hari untuk pemasangan turnkey penuh—kini menjadi piawaian baharu di Lembah Silikon dan seterusnya. Kelenturan ini hanya mungkin jika rekabentuk anda mengalir lancar menerusi saluran pengeluaran, dengan amalan DFM dan DFA yang memastikan tiada kesesakan.

|

Langkah Pengeluaran |

Masa Siap Piawai |

Masa pengedaran pantas |

|

Pembuatan PCB |

4–7 hari |

1 hari (dipercepat) |

|

Pemasangan (SMT/THT) |

7–10 hari |

2–5 hari |

|

Ujian Fungsional |

2–3 hari |

Hari yang sama/Hari berikutnya |

|

Penyelesaian Turnkey (Papan Penuh) |

2–3 minggu |

5–7 hari |

Syarikat teknologi pakai semula dari Lembah Silikon memerlukan prototaip berfungsi untuk persembahan kepada pelabur berisiko tinggi—dalam tempoh empat hari. Dengan memberikan fail DFM/DFA yang disahkan kepada rakan niaga tempatan berpusingan cepat, mereka menerima 10 papan siap terpasang, diuji oleh AOI, dan berfungsi tepat pada masanya. Pasukan pesaing dengan nota pembuatan yang tidak lengkap dan BOM yang hilang menghabiskan keseluruhan minggu dalam keadaan 'perubahan kejuruteraan' yang tidak pasti, kehilangan peluang kompetitif mereka.

Sama ada anda membuat prototaip atau meningkatkan pengeluaran, dapatkan harga secara serta merta dan anggaran masa pusingan masa sebenar daripada Sierra Circuits atau rakan pilihan anda. Muat naik fail DFM/DFA yang disahkan dan saksikan projek anda bergerak daripada CAD ke papan siap dalam rekod masa.

Pengeluaran papan litar bercetak (PCB) jauh dari proses satu saiz untuk semua. Kebutuhan prototaip untuk elektronik yang boleh dipakai adalah sangat berbeza daripada peranti perubatan kritikal misi atau papan kawalan aerospace berkeboleharapan tinggi. Garis panduan DFM dan DFA—bersama dengan kepakaran khusus industri pengilang—adalah asas utama dalam membina PCB yang bukan sahaja berfungsi, tetapi unggul dalam persekitaran unik masing-masing.

Mari lihat bagaimana pemimpin industri memanfaatkan DFM/DFA dan teknologi pengeluaran PCB terkini untuk keputusan terbaik dalam pelbagai sektor:

|

Industri |

Fokus Utama DFM/DFA |

Pematuhan/Piawaian |

|

Aeroangkasa/Pertahanan |

Kesimetrian susunan, penjejakan, COC, AOI lanjutan |

IPC Class 3, AS9100D, ITAR |

|

Automotif |

Sambungan kukuh, anti-getaran, ujian pantas |

ISO 26262, ISO/TS 16949 |

|

Pengguna/Boleh Dipakai |

Pengecilan, panelisasi, kecekapan kos |

IPC Class 2, RoHS |

|

Peranti Perubatan |

Pembersihan, akses titik ujian, keserasian biologi |

ISO 13485, FDA 21 CFR 820 |

|

Industri/IoT |

Perlindungan alam sekitar, jangka hayat panjang, boleh dikesan |

RoHS, REACH, UL |

|

Universiti/Penyelidikan |

Kelajuan prototaip, alat pembelajaran, templat dokumen |

IPC-2221, kajian DFM pantas |

Dalam dunia elektronik canggih yang sentiasa semakin pantas, Kelewatan pengeluaran PCB dan kecacatan pemasangan bukan sekadar halangan teknikal—ia adalah risiko perniagaan . Seperti yang telah terperinci dalam panduan ini, punca utama kelewatan, kerja semula, dan kehilangan hasil hampir sentiasa boleh dicegah Kesilapan DFM dan Kesilapan DFA . Setiap kesilapan—sama ada lapisan timbunan yang tidak sepadan, skrin sutera yang kabur, atau titik ujian yang hilang—boleh menelan kos berminggu-minggu, belanjawan, atau malah pelancaran produk.

Apa yang membezakan pasukan dan pengilang PCB terbaik dalam industri ialah komitmen tanpa kompromi terhadap Reka Bentuk untuk Pembuatan dan Reka Bentuk untuk Pemasangan —bukan sebagai fikiran tambahan, tetapi sebagai disiplin reka bentuk utama dan proaktif. Apabila anda mengintegrasikan garis panduan DFM dan DFA pada setiap peringkat, anda memberdayakan keseluruhan kitaran pembangunan anda untuk:

Muat turun Buku Panduan DFM dan DFA kami Senarai semak DFM/DFA yang segera boleh ditindakkan, panduan penyelesaian masalah, dan rujukan praktikal berdasarkan piawaian IPC—semuanya direka bentuk untuk mengurangkan risiko rekabentuk PCB seterusnya anda.

Gunakan alat dan aliran kerja terbaik industri Pilih perisian rekabentuk PCB (contohnya, Altium Designer, OrCAD) dengan semakan DFM/DFA terbina dalam dan sentiasa selaraskan output anda dengan format yang dipilih oleh pengilang.

Wujudkan saluran komunikasi terbuka Libatkan pengilang anda dalam perbincangan rekabentuk seawal mungkin. Ulasan rekabentuk berkala, kelulusan susunan pra-pengilangan, dan platform dokumen bersama dapat mengelakkan kejutan dan menjimatkan masa.

Mengamalkan sikap peningkatan berterusan Catatkan pengajaran daripada setiap proses pembinaan. Kemaskini senarai semak dalaman anda, arkibkan catatan fabrikasi dan pemasangan, serta tutup gelung maklum balas dengan rakan kongsi anda—dengan mengamalkan pendekatan PDCA (Rancang-Laksana-Semak-Tindakan) untuk peningkatan hasil dan kecekapan yang berterusan.

Sama ada anda syarikat mula-mula yang inovatif atau pakar lama dalam industri, meletakkan DFM dan DFA sebagai teras proses anda adalah cara paling berkesan untuk mengurangkan kecacatan, mempercepatkan pemasangan, dan melaksanakan penskalaan dengan jayanya . Bekerjasama dengan pengilang yang telah terbukti dan progresif dari segi teknologi seperti Sierra Circuits atau ProtoExpress —dan bergerak dengan yakin daripada peringkat siap rekabentuk hingga pelancaran pasaran.

Dfm (Reka Bentuk untuk Pembuatan) memberi tumpuan kepada pengoptimuman susun atur dan dokumentasi PCB anda supaya proses pembuatan—pengukiran, pengeboran, penyaduran, perutean—dapat dilakukan dengan cepat, betul, dan pada skala besar. DFA (Reka Bentuk untuk Pemasangan) memastikan papan anda akan bergerak lancar melalui fasa peletakan, pematerian, pemeriksaan, dan ujian dengan risiko minimum kesilapan atau kerja semula semasa pemasangan PCB.

|

Fail Yang Mesti Disertakan |

Tujuan |

|

Gerber RS-274X / ODB++ |

Data imej/layer untuk fabrikasi |

|

Fail NC Drill |

Kiraan dan spesifikasi lubang/via |

|

Lukisan Susunan Berlapis |

Rujukan bahan lapisan dan ketebalan |

|

BOM terperinci (Senarai Bahan) |

Pengurusan sumber yang betul, penjejakan kitar hayat |

|

Fail Pick-and-place |

Panduan mesin pemasangan automatik |

|

Senarai bersih (IPC-D-356A) |

Uji dan sahkan sambungan elektrik |

|

Nota Fabrikasi |

Siap akhir, had toleransi, dan keperluan proses |

|

Lapisan Mekanikal/Halaman |

Maklumat pengisaran, alur, dan kelegaan tepi |

Dengan menghapuskan kekaburan dan menjadikan rekabentuk anda boleh dibina sejak dari awal, anda dapat mengelakkan perubahan kejuruteraan last minute, perbincangan ulang-alik untuk penjelasan, dan kelewatan tidak disengajakan dalam kedua-dua perengkaan dan perakitan. Ini membolehkan penginian cepat, operasi pusingan pantas yang boleh dipercayai, dan keupayaan untuk berubah dengan cepat apabila keperluan berubah .

Berita Hangat

Berita Hangat2026-01-17

2026-01-16

2026-01-15

2026-01-14

2026-01-13

2026-01-12

2026-01-09

2026-01-08