Einführung

In der heutigen Welt der Elektronik mit hoher Dichte steigt die Nachfrage nach zuverlässigen, kompakten und elektrisch leistungsfähigen Leiterplatten weiter an. Die 4-Lagen-PCB, manchmal auch als vierlagige Leiterplatte bezeichnet, hat sich zu einer der am häufigsten verwendeten Lösungen für Anwendungen entwickelt, die von consumerseitigen IoT-Geräten über industrielle Steuersysteme bis hin zur Automobil-Elektronik reichen.

Während zweilagige PCBs für einfache Schaltungen ausreichen mögen, erfordern technologische Trends wie höhere Taktraten, Mixed-Signal-Designs und kompakte Gerätebauformen eine verbesserte Signalintegrität, geringere elektromagnetische Störungen (EMI) und eine bessere Stromversorgung – alles Vorteile, die durch 4-Lagen-PCB-Aufbauten erreicht werden.

Dieser umfassende Leitfaden von kingfield – Ihrem vertrauenswürdigen PCB-Hersteller aus Shenzhen und UL-, ISO9001-, ISO13485-zertifizierten Lieferanten – führt Sie durch:

- Den Aufbau und die Funktion einer 4-Lagen-PCB.

- Detaillierte, schrittweise Herstellungsprozesse für 4-Lagen-PCBs.

- Stack-up-Konzepte, Innenlagengravur und Laminierpraktiken.

- Bewährte Methoden für das Design (Signal-, Strom- und Masseebenenanordnung, kontrollierte Impedanz, Via-Management) und die nachgeschaltete Montage.

- Die Technologien hinter dem Bohren (CNC), dem Durchkontaktieren und Galvanisieren, der Auswahl und Aushärtung von Lötstopplack, sowie Oberflächenbeschichtungen wie ENIG, OSP und HASL.

- Wichtige Qualitätskontroll- und Prüfstandards wie AOI und In-Circuit-Test (ICT).

- Wie man Materialvorbereitung, Prozessablauf und Stack-up-Optimierung aufeinander abstimmst, um Qualität, Kosteneffizienz und Leistung zu erreichen.

Was ist eine 4-Lagen-PCB?

A 4-Lagen-PCB (vierlagige Leiterplatte) ist eine Art mehrschichtiger PCB, die vier übereinander angeordnete Kupferleiterlagen enthält, getrennt durch Isolierschichten aus Dielektrikum. Die Kernidee eines 4-Lagen-PCB-Stack-ups besteht darin, Konstrukteuren mehr Freiheit und Zuverlässigkeit bei der Verdrahtung komplexer Schaltungen zu bieten, kontrollierte Impedanz zu erreichen, die Stromversorgung zu verwalten und elektromagnetische Störungen (EMI) im Vergleich zu herkömmlichen 2-Lagen-PCBs zu minimieren.

Aufbau und typischer Schichtaufbau

Eine herkömmliche 4-Lagen-Leiterplatte wird durch das Laminieren abwechselnder Kupfer- und Dielektrikumschichten (auch als Prepreg und Core bekannt) hergestellt, um eine starre, flache Struktur zu erreichen. Die Schichten repräsentieren typischerweise folgende Funktionen:

|

Schicht

|

Funktionalität

|

|

Oberste Schicht (L1)

|

Signalverdrahtung, Bauteilepads (üblicherweise SMT/THT)

|

|

Innere Schicht 1 (L2)

|

Üblicherweise Masseebene (GND) für Signalintegrität und EMI

|

|

Innere Schicht 2 (L3)

|

Typischerweise Versorgungsebene (VCC, 3,3 V, 5 V usw.)

|

|

Unterste Schicht (L4)

|

Signalverdrahtung, SMT-Bauteile oder Steckverbinder

|

Diese Anordnung (Signal | Masse | Stromversorgung | Signal) ist der Industriestandard und bietet mehrere ingenieurtechnische Vorteile:

- Signale außen erleichtern Montage und Fehlerbehebung.

- Durchgehende Massefläche unter Hochgeschwindigkeitsspuren reduziert elektromagnetische Störungen (EMI) und Übersprechen.

- Dedizierte Stromversorgungsfläche führt zu einer stabilen Stromversorgung und optimaler Entkopplung.

4-Lagen-PCB im Vergleich zu anderen PCB-Typen

Vergleichen wir die wichtigsten Eigenschaften typischer PCB-Konfigurationen:

|

Funktion

|

2-Lagen-PCB

|

4-Lagen-PCB

|

6-Lagen-PCB

|

|

Anzahl der Kupferschichten

|

2

|

4

|

6

|

|

Routing-Dichte

|

Niedrig

|

Mäßig/Hoch

|

Sehr hoch

|

|

Signalintegrität

|

Begrenzt

|

Ausgezeichnet (bei guter Konstruktion)

|

Vorgesetzter

|

|

Energieversorgung

|

Grundlegend (keine Ebenen)

|

Stark (dedizierte Ebene)

|

Ausgezeichnet (mehrere Ebenen)

|

|

EMI-Reduzierung

|

Mindestwert

|

Gut

|

- Das Beste

|

|

PCB-Dicke

|

0,8 mm–2,4 mm

|

1,2 mm–2,5 mm (typisch)

|

1,6 mm+

|

|

Anwendungsbereich

|

Niedrige Dichte, einfach

|

Mittel bis hohe Komplexität

|

Hochfrequent, kritisch für SI

|

|

Kosten

|

Niedrig

|

Mittel (≈2× 2-Lagen)

|

Hoch

|

Wesentliche Vorteile von 4-Lagen-PCBs

1. Verbesserte Signalintegrität

Ein 4-Lagen-PCB-Design bietet präzise gesteuerte Leiterbahnimpedanzen und einen kurzen, induktionsarmen Signalrückführungsweg – dank interner Bezugsebenen. Dies ist besonders wichtig für Hochgeschwindigkeits- oder HF-Signale, wie sie beispielsweise bei USB 3.x, HDMI oder drahtlosen Kommunikationssystemen vorkommen. Die Verwendung einer durchgehenden Masseebene direkt unter den Signalschichten reduziert signifikant Rauschen, Übersprechen und die Gefahr von Signalverzerrungen.

2. EMI-Reduzierung

EMI stellt ein großes Problem in der modernen Elektronik dar. Das mehrschichtige Schichtaufbaudesign – mit eng beieinander liegenden Masse- und Versorgungsebenen – wirkt als integrierter Schirm gegen äußeres Rauschen und verhindert Abstrahlungen durch eigene hochfrequente Schaltungen auf der Platine. Entwickler können den Abstand zwischen den Ebenen (Prepreg/Kern-Dicke) optimieren, um beste EMC-Ergebnisse zu erzielen.

3. Überlegene Stromverteilung

Die internen Strom- und Masseebenen bilden ein natürliches Stromversorgungsnetzwerk (PDN) und bieten eine große Fläche für Entkopplungskondensatoren, wodurch Spannungsabfälle und Versorgungsgeräusche reduziert werden. Sie helfen, hohe Lastströme auszugleichen und Hotspots zu vermeiden, die empfindliche Bauteile beschädigen können.

4. Erhöhte Routing-Dichte

Mit zwei zusätzlichen Kupferschichten haben Schaltungsdesigner deutlich mehr Platz für Leiterbahnen – dies verringert die Abhängigkeit von Durchkontaktierungen, ermöglicht kleinere Leiterplattengrößen und die Verwendung komplexerer Bauelemente (wie LSI, FPGAs, CPUs und DDR-Speicher).

5. Geeignet für kleinere Geräte

4-schichtige PCB-Aufbauten sind ideal für kompakte oder tragbare Elektronik, einschließlich IoT-Sensoren, medizinischer Geräte und Automotive-Module, bei denen dichte Layouts entscheidend für das Produktformat sind.

6. Bessere mechanische Festigkeit

Die strukturelle Steifigkeit durch Mehrschicht-Laminierung gewährleistet, dass die Leiterplatte Montagebelastungen, Vibrationen und Biegebeanspruchungen in rauen Umgebungen standhalten kann.

Typische Anwendungsszenarien für 4-Lagen-PCBs

- Router, Hausautomatisierung und HF-Module (bessere EMV- und Signalqualität)

- Industrielle Steuerungen und Fahrzeug-ECUs (Belastbarkeit und Zuverlässigkeit)

- Medizinische Geräte (kompakte Bauform, störanfällige Signale)

- Smartwatches und Wearables (hohe Packungsdichte, kleines Format)

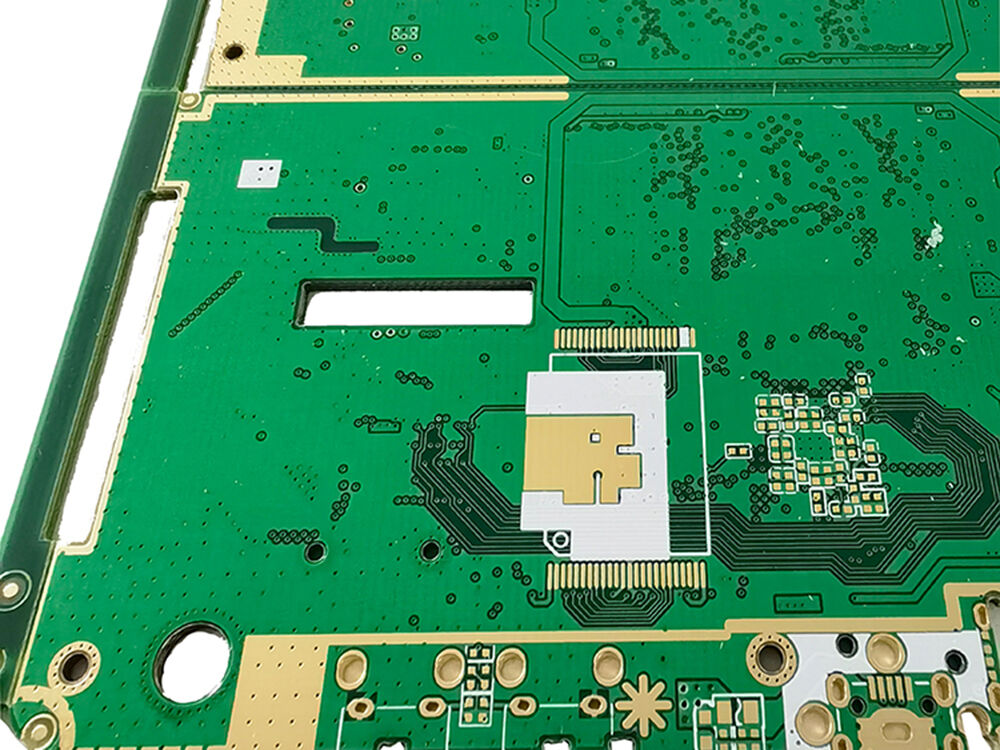

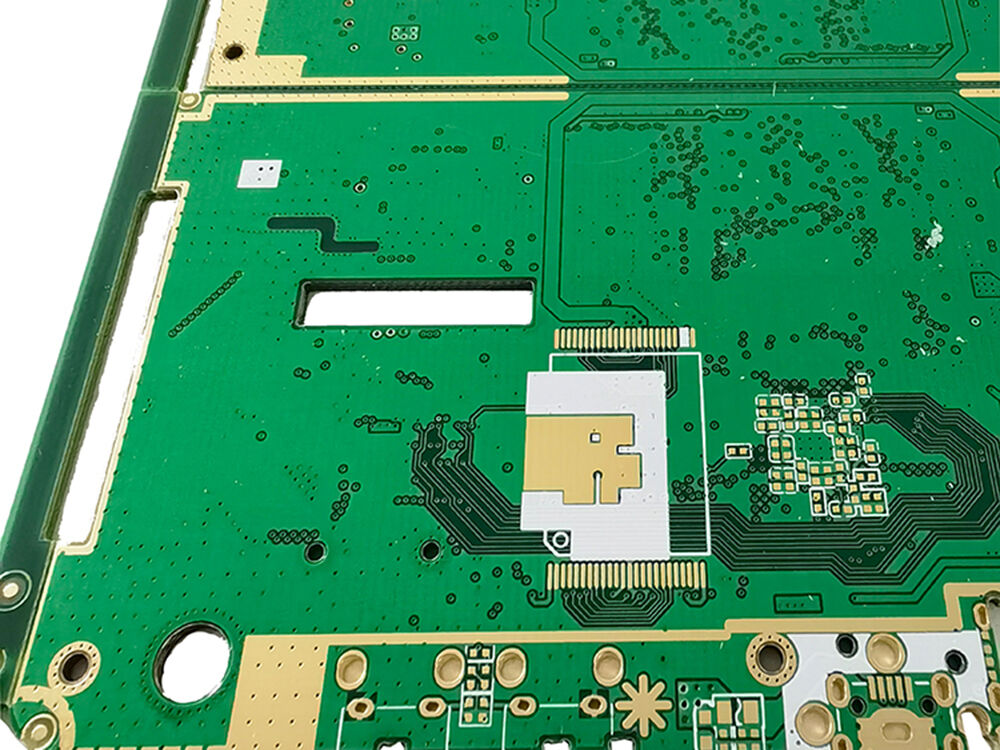

Wesentliche Schritte im Herstellungsprozess von 4-Lagen-PCBs

Die schritt-für-Schritt-Herstellungsprozess einer 4-Lagen-PCB ist entscheidend für alle Beteiligten in den Bereichen Leiterplattendesign, Beschaffung oder Qualitätssicherung. Im Kern ist die Herstellung von 4-Lagen-Leiterplatten ein präziser, mehrstufiger Prozess, bei dem kupferkaschierte Laminate, Prepregs und elektronische Designdateien in eine robuste, kompakte und baugruppentaugliche Mehrlagen-PCB umgewandelt werden.

Überblick: Wie werden die Hauptschritte bei der Herstellung von 4-Lagen-PCBs durchgeführt?

Im Folgenden finden Sie den groben Ablauf der Herstellung von 4-Lagen-PCBs, der sowohl für Einsteiger als auch für erfahrene Fachleute als Leitfaden dienen kann:

- PCB-Design und Schichtaufbau-Planung

- Materialvorbereitung (Prepreg, Kern, Kupferfolien-Auswahl)

- Innenlagenausbelichtung und Ätzen

- Lagenanpassung und Laminierung

- Bohren (CNC) und Entgraten der Bohrungen

- Vias Beschichten und Galvanisieren

- Außenlagen-Belichtung (Lackauftrag, Ätzen)

- Lackauftrag für Lötstopmaske und Aushärtung

- Oberflächenveredelung (ENIG, OSP, HASL, etc.)

- Screenprinting

- PCB-Umrisserstellung (Fräsen, Schneiden)

- Montage, Reinigung und Prüfung (AOI/ICT)

- Endgültige Qualitätskontrolle, Verpackung und Versand

Die folgende Schritt-für-Schritt-Anleitung vertieft sich in jeden Bereich und erläutert bewährte Verfahren, Fachbegriffe und besondere Merkmale des 4-Lagen-PCB-Herstellungsprozesses .

Schritt 1: Konstruktionsüberlegungen

Die Entwicklung einer vierlagigen Leiterplatte beginnt mit dem Engineering-Team, das die Anforderungen der Schaltung definiert. Diese werden in detaillierte Konstruktionsdateien umgesetzt – einschließlich der Schichtaufbau-Definition, der Lagenanordnung und der Fertigungsdaten.

Wesentliche Elemente der 4-Lagen-PCB-Konstruktion:

- Auswahl des Schichtaufbaus: Gängige Optionen wie Signal | Masse | Stromversorgung | Signal oder Signal | Stromversorgung | Masse | Signal. Die Wahl beeinflusst direkt die elektrische Leistungsfähigkeit und die Herstellbarkeit.

-

Materialauswahl:

- Kern: Üblicherweise FR-4, obwohl Hochfrequenz- und Hochzuverlässigkeitskonstruktionen Rogers-, Metallkern- oder Keramiksubstrate verwenden können.

- Prepreg: Dieses glasfaserverstärkte Harz ist entscheidend für die dielektrische Isolierung und mechanische Festigkeit.

- Kupferdicke: 1 Unze ist Standard; 2 Unzen und mehr bei Leistungsebenen oder speziellen thermischen Anwendungen.

- Geregelte Impedanzplanung: Für Schaltungen mit Hochgeschwindigkeits- oder Differenzialsignalen (USB, HDMI, Ethernet) müssen die Anforderungen an die geregelte Impedanz gemäß IPC-2141A-Richtlinien angegeben werden.

-

Via-Technologie:

- Durchkontaktierungen sind Standard bei den meisten vierlagigen Leiterplatten.

- Blind-/Geschlossene Vias, Back-Drilling und Harzfüllung sind Sonderoptionen für hochdichte oder hochfrequente Leiterplatten; sie können eine sequenzielle Laminierung erfordern.

-

Leiterplattendesign-Tools: Die meisten 4-Lagen-PCB-Projekte beginnen in professionellen CAD-Werkzeugen:

- Altium Designer

- KiCad

- Autodesk Eagle Diese Plattformen erzeugen Gerber-Dateien und Bohrdateien – die standardmäßigen digitalen Baupläne, die an den Hersteller gesendet werden.

- Design for Manufacturing (DFM)-Prüfung: DFM-Prüfungen werden durchgeführt, um sicherzustellen, dass alle Elemente herstellbar sind – die Überprüfung von Leiterbahnbreiten/Abständen, Durchkontaktierungs-Verhältnis, Ringringbreite, Lötstoplack, Beschriftung und mehr. Frühzeitiges DFM-Feedback verhindert kostspielige Neukonstruktionen oder Produktionsverzögerungen.

Beispieltabelle: Typische 4-Lagen-PCB-Aufbauoptionen

|

Aufbauoption

|

Schicht 1

|

Schicht 2

|

Schicht 3

|

Schicht 4

|

Bestes für

|

|

Standard (am gebräuchlichsten)

|

Signal

|

Erde

|

Leistung

|

Signal

|

Kontrollierte Impedanz, EMI-empfindlich

|

|

Alternative

|

Signal

|

Leistung

|

Erde

|

Signal

|

Rückleitpfad-Management

|

|

Hochfrequent

|

Signal

|

Erde

|

Erde

|

Signal

|

GHz+-Schaltungen, hervorragende Isolation

|

|

Brauch

|

Signal

|

Signal/Stromversorgung

|

Erde

|

Signal

|

Gemischte Schaltungen, fortschrittliche EMV-Anpassung

|

Der nächste Schritt

Die nächste Phase in der 4-Schicht-PCB-Herstellungsprozess iS Materialvorbereitung —einschließlich Kernmaterialauswahl, Prepreg-Verwaltung und Laminatreinigung.

Schritt 2: Materialvorbereitung

Kernmaterialauswahl und Handhabung von kupferkaschierten Laminaten

Jede hochwertige 4-Schicht-PCB beginnt mit der sorgfältigen Auswahl und Vorbereitung ihrer Kernelemente. Eine typische vierlagige PCB verwendet kupferkaschierte Laminate —isolierte Platten, beidseitig mit Kupferfolie kaschiert—als internes „Skelett“ der PCB.

Materialtypen umfassen:

- FR-4 : Bei weitem der häufigste Kern, bietet ein ausgewogenes Kosten-Leistungs-Verhältnis für die meisten Anwendungen.

- Hohe TG FR-4 : Wird für Leiterplatten verwendet, die eine höhere Temperaturbeständigkeit erfordern.

- Rogers, Teflon und Hochfrequenz-Laminate : Für HF- und Mikrowellen-Leiterplatten spezifiziert, bei denen geringe Verluste und stabile dielektrische Eigenschaften entscheidend sind.

- Metallkern (Aluminium, Kupfer) : Für Leistungselektronik oder hohe thermische Anforderungen.

- Keramik und CEM : Wird in Nischenanwendungen mit hohen Leistungsanforderungen eingesetzt.

Tatsache: Die Mehrheit der mehrschichtigen Leiterplatten in der Unterhaltungselektronik, Medizintechnik und Industrie nutzt Standard FR-4 kerne mit einer 1 Unze Kupferstärke als Ausgangspunkt, um Kosten, Herstellbarkeit und elektrische Zuverlässigkeit zu optimieren.

Zuschneiden der Laminate auf Platinengröße

Leiterplattenfertigungsanlagen verarbeiten Baugruppen in großen Paneelen, die nach der Schaltmusterung und Bestückung in einzelne Leiterplatten unterteilt werden. Das präzise Zuschneiden von kupferkaschierten Laminaten und Prepreg-Blättern gewährleistet Gleichmäßigkeit, maximiert den Materialertrag und passt sich den Panelisierungsverfahren zur optimalen Kosteneffizienz an.

Verwendung von Prepreg im Schichtaufbau

Prepreg (vorimprägnierte Verbundfasern) ist im Wesentlichen ein Glasfasergewebefolie, die mit teilweise gehärtetem Epoxidharz imprägniert ist. Während des Laminierprozesses werden Prepregs zwischen Kupferschichten und Kernen eingelegt und wirken sowohl als Dielektrikum (für die erforderliche Isolation) als auch als Klebstoff (durch Aufschmelzen und Verbinden der Schichten beim Erhitzen).

Wichtige technische Punkte:

- Kompatibilität der Dielektrikumdicke: Die Prepreg- und Kerndicke werden so angepasst, dass die gewünschte Leiterplattendicke erreicht wird – beispielsweise 1,6 mm für Standard-4-Lagen-PCB-Aufbauten.

- Dielektrizitätskonstante (Dk): Moderne Anwendungen (insbesondere HF/hochgeschwindigkeitsdigitale) benötigen gut charakterisierte Prepregs; Dk-Werte beeinflussen direkt die Impedanz der Leiterbahnen.

- Feuchtigkeitsbeständigkeit: Hochwertiges Prepreg minimiert die Wasseraufnahme, die andernfalls elektrische Eigenschaften und Zuverlässigkeit beeinträchtigen könnte.

Vorreinigung der Kupferoberfläche

Ein entscheidender, jedoch oft übersehener Schritt bei der Herstellung von Vierlagigen Leiterplatten ist die vorreinigung der Kupferoberflächen auf Kern- und Folienmaterialien:

- Bürsten und Mikroätzverfahren: Die Materialien werden mechanisch gebürstet und anschließend in eine schwache Säure oder ein chemisches Mikroätzmittel getaucht. Dadurch werden Oberflächenoxide, Harze und Mikroteilchen entfernt, wodurch sauberes Kupfer für die nachfolgende Belichtung freigelegt wird.

- Trocknen: Verbleibende Feuchtigkeit kann die Haftung schwächen oder Delamination verursachen, daher werden die Platinen sorgfältig getrocknet.

Material-Rückverfolgbarkeit und -kontrolle

An diesem Punkt professionell Hersteller von PCBs werden Chargennummern für jede Platine und Materialcharge vergeben. Rückverfolgbarkeit ist entscheidend, um Qualitätsstandards (ISO9001, UL, ISO13485) zu erfüllen und um im seltenen Fall nach Lieferung auftretender Probleme diese zurückverfolgen zu können.

Tabelle: Typische Materialien und Spezifikationen für eine Standard-4-Lagen-Leiterplatte

|

Material

|

Anwendung

|

Typische Spezifikationen

|

|

FR-4-Trägermaterial

|

Untergrund

|

0,5 – 1,2 mm, 1 Unze Cu

|

|

Prepreg

|

Dielektrische

|

0,1 – 0,2 mm, Dk = 4,2 – 4,5

|

|

Kupferfolie

|

Leitfähig

|

1 Unze (35 µm) Standard; 2 Unzen für Stromversorgungsschichten

|

|

Lötmaske

|

Schutz

|

Grün, 15–30 µm dick, LPI-Typ

|

|

Siebdruckfarbe

|

Markierungen

|

Weiß, <0,02 mm erhöht

|

Die richtige Materialvorbereitung bildet das Rückgrat einer zuverlässigen 4-Lagen-PCB. Als Nächstes gehen wir über zu einer kritischen technischen Phase: Belichtung und Ätzung der Innenlagen.

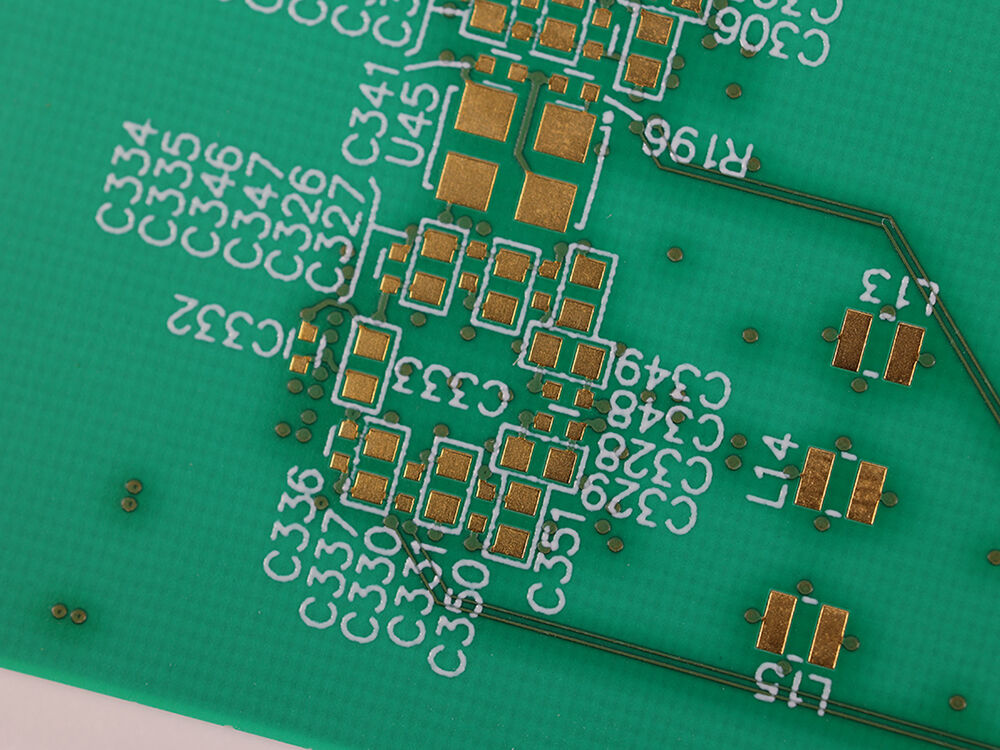

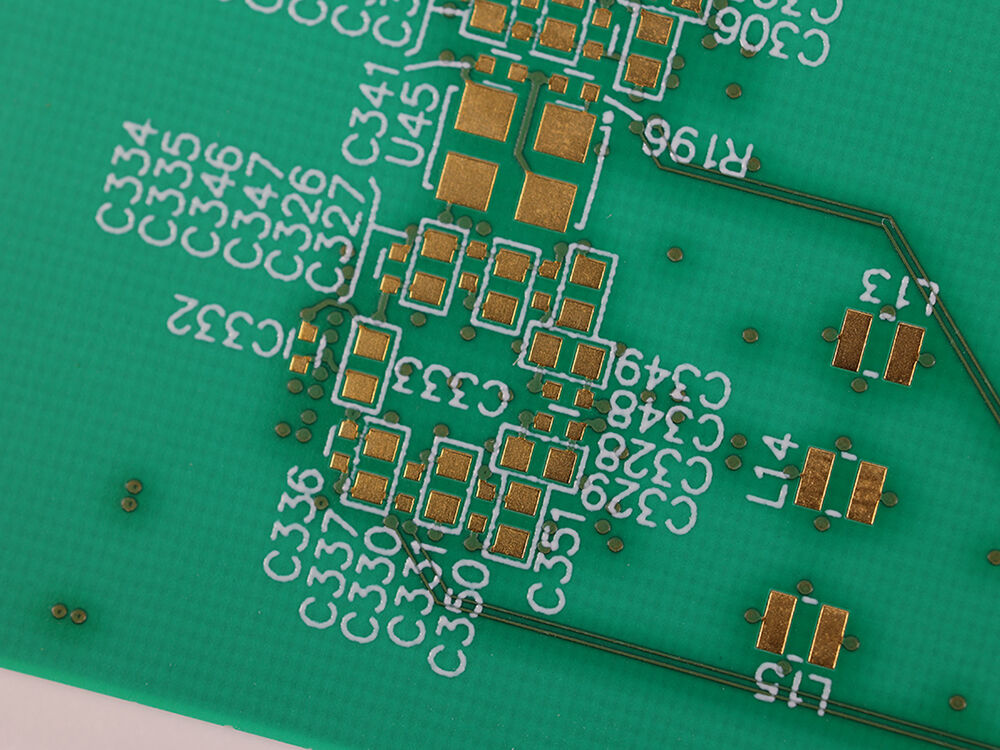

Schritt 3: Belichtung und Ätzung der Innenlagen

Die Schaltung der Innenlagen einer 4-Lagen-PCB – typischerweise Masse- und Versorgungsebenen oder zusätzliche Signallagen bei speziellen Schichtaufbauten – bildet das elektrische Rückgrat für die gesamte Signalweiterleitung und Stromversorgung. In diesem Schritt wird Ihr digitales PCB-Design mit submillimeternder Genauigkeit physisch auf echtem Kupfer realisiert.

1. Reinigung: Oberflächenvorbereitung

Vor der Belichtung durchlaufen die vorgereinigten Kupferkerne (aus dem vorherigen Schritt vorbereitet) eine letzte Spülung und einen Mikroätzprozess. Dieser chemische Mikroätzungsschritt entfernt letzte Oxidrückstände, erhöht die Oberflächenrauheit auf mikroskopischer Ebene und gewährleistet eine optimale Haftung des Photolacks. Verunreinigungen, selbst winzige, könnten zu Unterätzung, Unterbrechungen/Kurzschlüssen oder schlechter Druckauflösung führen.

2. Photolack-Auftrag

Die gereinigten kupferkaschierten Kerne werden anschließend beschichtet mit fotolack —einem lichtempfindlichen Polymerfilm, der eine genaue Leiterbahndefinition direkt ermöglicht. Die Aufbringung erfolgt typischerweise über einen trockenfilm-Laminierprozess , bei dem der Fotolack unter beheizten Walzen fest auf das Kupfer haftet.

-

Typen:

- Negativ-Fotolack ist der Industriestandard für mehrlagige Leiterplatten; belichtete Bereiche vernetzen sich und verbleiben nach der Entwicklung.

- Flüssiger Fotolack kann in einigen Verfahren zur feineren Steuerung verwendet werden, obwohl Trockenfilm bei der Herstellung der meisten vierlagigen Leiterplatten vorherrscht.

3. Belichtung (UV-Abbildung / Fotobelichtung)

Als Nächstes durchläuft der vorbereitete Kern einen automatisierte UV-Bildgebungsanlage , wo ein hochauflösender Laser oder eine CAD-generierte Fotomaske die Leiterbahnmuster über der kupferbeschichteten Platine ausrichtet. Ultraviolettes Licht scheint durch die transparenten Bereiche der Maske:

- Wo die Maske transparent ist : Der Lack wird belichtet und polymerisiert (verhärtet).

- Wo die Maske opak ist : Der Lack bleibt weich und unbearbeitet.

4. Entwicklung (Auswaschen des unbearbeiteten Lacks)

Die Platine wird entwickelt – in eine milde wässrige Lösung (Entwickler) eingetaucht. Der unbearbeitete, weiche Lack wird weggespült, wodurch das darunterliegende Kupfer freigelegt wird. Nur das Leiterbahnmuster (nun harter, belichteter Lack) bleibt erhalten und entspricht exakt dem in den Gerber-Dateien bereitgestellten Design.

5. Ätzen (Kupferentfernung)

Die Leiterplatte durchläuft nun innere Schichtätzung —ein kontrolliertes Ätzverfahren mit einer ammoniakalen oder Eisenchloridlösung:

- Das Ätzen entfernt das unerwünschte Kupfer aus Bereichen, die nicht durch den ausgehärteten Fotolack geschützt sind.

- Leiterbahnen, Kontakte, Flächen und andere konstruierte Kupferelemente verbleiben.

6. Lackentfernung

Sobald die gewünschten Kupferstrukturen freigelegt sind, wird der ausgehärteste Fotolack, der diese Bereiche schützt, mittels einer separaten chemischen Lösung abgewaschen. Freiliegende, glänzende Kupferbahnen bleiben zurück, die exakt dem Layout der Innenschicht entsprechen.

Qualitätskontrolle: Automatische optische Inspektion (AOI)

Jede Innenschicht wird mithilfe von Automatische optische Inspektion (AOI) gründlich auf Fehler überprüft. Hochauflösende Kameras scannen nach:

- Unterbrochene Leiterbahnen (durchtrennte Spuren)

- Unter- oder überätzte Strukturen

- Kurzschlüsse zwischen Leiterbahnen oder Lötflächen

- Ausrichtungs- oder Registerfehler

Warum das Ätzen der inneren Schicht für 4-Lagen-Leiterplatten entscheidend ist

- Signalintegrität: Sauber geätzte innere Ebenen gewährleisten eine konsistente Referenz für Hochgeschwindigkeitsleitungen und verhindern Störungen und elektromagnetische Störstrahlung (EMI).

- Energieverteilung: Breite Spannungsebenen minimieren Spannungsabfall und Leistungsverlust.

- Ebenenkontinuität: Die Aufrechterhaltung breiter, ununterbrochener Ebenen entspricht den IPC-2221/2222-Normen und reduziert Impedanzabweichungen.

"Die Genauigkeit dieses Schritts bestimmt die Leistung Ihrer Leiterplatte. Ein einziger Kurzschluss oder Unterbruch in einer internen Strom- oder Massebahn führt nach der Laminierung zum Totalausfall – und ist nicht reparierbar. Deshalb legen führende Leiterplattenhersteller besonderen Wert auf Bildkontrolle und inline AOI." — kINGFIELD

Schritt 4: Schichtenausrichtung und Laminierung

- Das ist richtig. ausrichtung und Laminierung sind bei der Herstellung von 4-Lagen-Leiterplatten entscheidend. Dieser Prozess verbindet die zuvor belichteten Kupferschichten (die nun die Leiterbahnen und Ebenen der Innenschichten enthalten) physikalisch mit Prepreg-Schichten und äußeren Kupferfolien, wodurch der vollständige Aufbau der Vierschichtplatine entsteht.

A. Stapelvorbereitung: Anordnung des Lagenaufbaus

Die Fertigungsanlage montiert nun den inneren Aufbau unter Verwendung von:

- Innere Kerne: Fertige (geätzte, gereinigte) Innenkerne – typischerweise Masse- und Versorgungsebenen.

- Prepreg: Sorgfältig bemessene dielektrische (isolierte) Schichten, die zwischen den Kupferkernen und den äußeren Kupferfolien platziert werden.

- Äußere Kupferfolien: Folien, die nach der Belichtung die oberen und unteren Leiterbahnebenen bilden.

B. Ausrichtung und Registrierung (Schichtenausrichtung)

Die Ausrichtung ist nicht nur eine mechanische Vorgabe – sie ist entscheidend für:

- Die Aufrechterhaltung der Pad-zu-Via-Registrierung, sodass gebohrte Löcher später nicht verfehlen, abschneiden oder mit benachbarten Strukturen kurzschließen.

- Die Sicherstellung, dass Referenzebenen direkt unterhalb kritischer Signalwege liegen, um die Signalintegrität und definierte Impedanz zu gewährleisten.

Wie die Ausrichtung erreicht wird:

- Ausrichtung mittels Stiften: Präzisionsstahlstifte und Passlöcher werden durch den Schichtverbund gestanzt, um alle Platten während des Aufbaus absolut exakt auszurichten.

- Optische Registrierung: Fortgeschrittene Leiterplattenwerke verwenden automatisierte optische Systeme, um die Schicht-zu-Schicht-Registrierung zu überprüfen und zu verbessern, wobei oftmals Toleranzen von ±25 μm (Mikrometer) erreicht werden.

C. Laminierung: Verbindung durch Hitze und Druck

Die gestapelte und fixierte Lage wird dann in einen warmpressen laminator:

- Vakuumstufe: Entfernt eingeschlossene Luft und flüchtige Rückstände, um Delamination oder Hohlräume zu verhindern.

- Hitze und Druck: Das Prepreg wird bei Temperaturen von 170–200 °C (338–392 °F) und Drücken von 1,5–2 MPa weich und fließt.

- Aushärten: Das aufgeweichte Harz im Prepreg füllt Mikrolücken aus und verbindet die Schichten miteinander, bevor es beim Abkühlen aushärtet (polymerisiert).

Das Ergebnis ist eine einzelne starre, verbundene Platte —mit vier deutlich getrennten, elektrisch isolierten Kupferschichten, die perfekt laminiert sind und für die weitere Bearbeitung bereitstehen.

Qualitätskontrolle: Inspektion und Prüfung nach der Laminierung

Nach der Laminierung wird die Platte abgekühlt und gereinigt. Wesentliche QC-Prüfungen umfassen:

- Dicke- und Verwölbungsmessungen: Stellt sicher, dass die Platine flach ist und die vorgegebenen Toleranzen einhält (typischerweise ±0,1 mm).

-

Zerstörende Querschnittsanalyse: Probeplatten werden zerschnitten und unter dem Mikroskop analysiert, um Folgendes zu überprüfen:

- Isolierung zwischen den Schichten (keine Entladung, Hohlräume oder Harzarmut).

- Schichtregistrierung (Genauigkeit von Schicht zu Schicht).

- Verbindungsgüte an den Prepreg-Kern-Grenzflächen.

- Sichtprüfung: Überprüfung auf Entladung, Verformung und Oberflächenverunreinigungen.

IPC-Standards und bewährte Verfahren

- IPC-6012: Legt Leistungs- und Prüfanforderungen für starre Leiterplatten fest, einschließlich der Mehrschichtenausrichtung und Laminierqualität.

- IPC-2221/2222: Empfiehlt durchgehende Flächen, minimale Aussparungen und strenge Passmaßtoleranzen für eine robuste Leistung.

- Materialien: Verwenden Sie Industrie-Prepreg, Kernmaterialien und Kupfer – vorzugsweise mit nachverfolgbaren Chargennummern für die Qualitätskontrolle und behördliche Berichterstattung.

Zusammenfassungstabelle: Vorteile einer präzisen Laminierung bei 4-Lagen-Leiterplatten

|

Leistung

|

Details

|

|

Herausragende Signalintegrität

|

Gewährleistet korrekte Beziehungen zwischen Masse-/Signalflächen

|

|

Zuverlässige elektrische Verbindungen

|

Stellt sicher, dass gebohrte Durchkontaktierungen alle erforderlichen Pads/Flächen treffen

|

|

Mechanische Haltbarkeit

|

Widersteht thermischen/mechanischen Belastungen während Montage und Einsatz

|

|

Reduzierte EMI

|

Minimiert Schichtverschiebungen und verhindert EMI-„Hotspots“

|

|

Fertigungsausbeute

|

Weniger Fehler, geringerer Ausschuss, bessere Kosteneffizienz

|

Schritt 5: Bohren und Beschichten

Die bohr- und Beschichtungsstufe der Vierlagigen-Leiterplatten-Herstellung ist der Punkt, an dem die physikalische und elektrische Verbindung der Platine wirklich entsteht. Eine präzise Via-Bildung und eine robuste Kupfergalvanik sind entscheidend für eine zuverlässige Signal- und Stromübertragung in mehrlagigen Aufbauten.

A. CNC-Bohren von Vias und Bauteilelöchern

Die moderne Herstellung von 4-lagigen Leiterplatten verwendet computergesteuerte (CNC) Bohrmaschinen, um pro Panel Hunderte oder sogar Tausende von Löchern zu erzeugen – mit Genauigkeit, Geschwindigkeit und Wiederholbarkeit, die für anspruchsvolle Anwendungen unerlässlich sind.

Arten von Bohrungen in 4-Lagen-Leiterplatten:

- Durchkontaktierungen: Reichen von der oberen Schicht bis zur unteren Schicht und verbinden alle Kupferebenen und Schichten. Sie bilden das Rückgrat für Signal- und Masseverbindungen.

- Bauteildurchbohrungen: Lötflächen für Durchsteckbauteile (THT), Steckverbinder und Pins.

-

Optional:

- Blindvias: Verbinden eine äußere Schicht mit einer (aber nicht beiden) inneren Schichten; seltener in 4-Schicht-Leiterplatten aufgrund der Kosten.

- Geschlossene Vias: Verbinden ausschließlich innere Schichten; werden in Projekten mit hoher Dichte oder bei starren-flexiblen Hybrid-Leiterplatten verwendet.

Hinweise zum Bohrprozess:

- Platinenstapelung: Mehrere Platten können gleichzeitig gebohrt werden, um den Durchsatz zu optimieren, wobei jede durch eine phenolische Eintritts-/Austrittsplatte gestützt wird, um Gratbildung oder Bohrversatz zu verhindern.

- Bohrerauswahl: Hartmetall- oder diamantbeschichtete Bohrer mit Durchmessern ab 0,2 mm (8 mils) aufwärts. Der Bohrerverschleiß wird genau überwacht und in strikten Intervallen ersetzt, um hohe Konsistenz sicherzustellen.

- Bohrpositionstoleranz: Typischerweise ±50 µm, entscheidend für die Ausrichtung von Via-Pads in hochdichten Layouts.

B. Entgraten und Entfernen von Smear

Nach dem Bohren entstehen mechanische Bearbeitungsrückstände wie scharfe Kanten (Grate) und Epoxidharz-Ablagerungen („Smear“) an der Via-Wand, insbesondere dort, wo Glasfasern und Harz freigelegt sind. Unbehandelt können diese die Beschichtung blockieren oder Zuverlässigkeitsprobleme verursachen.

- Entkantung: Mechanische Bürsten entfernen scharfe Kanten und Folienrückstände.

- Smear-Entfernung: Die Platten werden chemisch behandelt (mittels Kaliumpermanganat, Plasma oder permanganatfreier Verfahren), um Harzrückstände zu entfernen und Glasfaser sowie Kupfer vollständig für die anschließende Metallbindung freizulegen.

C. Via-Ausbildung und Kupferelektrolyse

Der wohl kritischste Schritt – das Beschichten der Vias – schafft die entscheidenden elektrischen Verbindungen zwischen den Schichten der 4-Lagen-PCB.

Der Prozess umfasst:

- Bohrlochwandreinigung: Die Platten durchlaufen eine Vorbehandlung (Säurereinigung, Mikroätzen), um makellose Oberflächen zu gewährleisten.

- Stromloses Kupferabscheiden: Eine dünne Kupferschicht (~0,3–0,5 µm) wird chemisch auf die Bohrlochwände abgeschieden, wodurch die Vias für die anschließende Elektrolyse vorbereitet („geimpft“) werden.

- Elektroplattierung: Die Leiterplatten werden in Kupferbäder gelegt. Gleichstrom (DC) wird angelegt; Kupferionen lagern sich auf allen freiliegenden Metallflächen ab – einschließlich der Via-Wände und Durchkontaktierungen – und bilden so in jedem Loch ein gleichmäßiges, leitfähiges Kupferrohr aus.

- Standard-Kupferdicke: Fertiggestellte Durchkontaktierungen werden typischerweise mit mindestens 20–25 µm (0,8–1 mil) beschichtet, gemäß IPC-6012 Klasse 2/3 oder Kundenspezifikationen.

- Gleichmäßigkeitprüfungen: Fortgeschrittene Dickenüberwachung und Querschnittsanalysen werden eingesetzt, um sicherzustellen, dass keine dünnen Stellen oder Hohlräume vorhanden sind, die zu Unterbrechungen oder intermittierenden Feldausfällen führen könnten.

Qualitätskontrolle:

- Querschnittanalyse: Stichprobenartig werden Löcher ausgeschnitten und hinsichtlich Wanddicke, Haftung und Gleichmäßigkeit gemessen.

- Durchgangsprüfungen: Elektrische Prüfungen stellen sicher, dass jede Durchkontaktierung eine solide Verbindung von Pad zu Pad, Schicht zu Schicht herstellt.

D. Warum Bohren und Beschichten bei 4-Schicht-PCBs wichtig sind

- Hohe Zuverlässigkeit: Gleichmäßige, fehlerfreie Beschichtung der Durchkontaktierungen verhindert Unterbrechungen/Kurzschlüsse und katastrophale Ausfälle im Feld. - Signalintegrität: Eine ordnungsgemäße Via-Bildung unterstützt schnelle Signalübergänge, niederohmige Rückleitungen und eine zuverlässige Stromversorgung. - Erweiterter Konstruktionssupport: Ermöglicht feinere Strukturen, dichtere Packungsdichten und Kompatibilität mit Technologien wie HDI oder starre-flexible PCB-Hybride.

Tabelle: Bohr- und Plattierparameter für Standard-4-Lagen-PCBs

|

Parameter

|

Typischer Wert

|

Hinweis

|

|

Min. fertige Lochgröße

|

0,25–0,30 mm (10–12 mil)

|

Kleiner für HDI/fortgeschrittene Verfahren

|

|

Kupferdicke in der Lochwand

|

≥ 20 µm (0,8 mil, IPC-6012)

|

Bis zu 25–30 µm bei Spezifikationen für hohe Zuverlässigkeit

|

|

Über Verhältnis der Seitenlängen

|

Bis zu 8:1 (Platinenstärke : Loch)

|

Höhere Verhältnisse erfordern sorgfältige DFM-Überlegungen

|

|

Beschichtungsgleichmäßigkeit

|

±10 % über die gesamte Platine

|

Überwacht durch Prüflingen/Röntgen

|

Schritt 6: Strukturierung der Außenschichten (Leiterbahnerzeugung auf Schicht 1 und 4)

Die außenschichten ihrer 4-Schicht-Leiterplatte—Schicht 1 (oben) und Schicht 4 (unten)—enthalten die Lötflächen, Leiterbahnen und Kupferstrukturen, die direkt mit Bauteilen oder Steckverbindern während der Bestückung interagieren. Dieser Schritt ähnelt im Grunde dem Verfahren bei den Innenschichten, jedoch sind die Anforderungen hier höher: Diese Schichten unterliegen starken thermischen Belastungen durch Lötvorgänge, Reinigungsschritten und mechanischer Abnutzung und müssen daher den strengsten optischen und dimensionellen Anforderungen genügen.

A. Auftragung des Fotolacks auf den Außenschichten

Wie bei den Innenlagen werden auch die äußeren Kupferfolien zunächst gereinigt und mikrogeätzt, um eine makellose Oberfläche zu gewährleisten. Eine Schicht fotolack (typischerweise Trockenfilm) wird dann mithilfe beheizter Walzen auf jeder Oberseite laminiert, um eine gute Haftung sicherzustellen.

- Tatsache: Hochwertige Leiterplattenhersteller kontrollieren sorgfältig sowohl die Filmdicke als auch den Laminierdruck, um eine gleichmäßige Bilderzeugung und eine Minimierung von Kantenverzerrungen zu gewährleisten.

B. Belichtung (Foto-Belichtung/UV-Laser-Direktbelichtung)

- Foto-Belichtung: Bei den meisten Serienanfertigungen werden Fotomasken, die die Muster der Kupferbahnen und -pads für Ober- und Unterseite enthalten, optisch zu den gebohrten Löchern ausgerichtet.

- Laserdirektabbildung (LDI): Bei hochpräzisen oder Expressprojekten „beschreibt“ ein computergesteuerter Laser die gemäß Gerber definierten Leiterbahnen und Pads direkt auf das Panel mit Genauigkeit im Mikrometerbereich.

- Ultraviolettes (UV-)Licht härtet den belichteten Fotolack aus und fixiert so die genaue Außenstruktur an ihrem Platz.

C. Entwicklung und Ätzen

- Entwicklung: Der nicht belichtete Fotolack wird mit einem milden alkalischen Entwickler abgewaschen, wodurch das Kupfer freigelegt wird, das anschließend weggeätzt wird.

- Säureätzung: Freiliegendes Kupfer wird durch Hochgeschwindigkeits-Förderätzgeräte entfernt, wodurch nur die Leiterbahnen, Kontakte und freiliegenden Schaltungen erhalten bleiben, die durch den ausgehärteten Fotolack geschützt sind.

- Entfernen: Der verbleibende Fotolack wird abgewaschen, wodurch die frischen, glänzenden äußeren Kupferstrukturen freigelegt werden, die die lötbarer Flächen und stromführenden Leiterbahnen für Ihre Platine bilden.

Tabelle: Wichtige Abmessungen für die Außenstrukturierung von 4-Lagen-PCBs

|

Funktion

|

Standardwert

|

Hinweis

|

|

Spurenbreite

|

0,15–0,25 mm (6–10 mil)

|

Für die meisten digitalen, Leistungs- und Mixed-Signal-Designs

|

|

Raum

|

0,15–0,20 mm (6–8 mil)

|

Geregelt gemäß IPC Class 2/3

|

|

Durchlaufring

|

≥0,1 mm (4 mil)

|

Von der Fertigungsgerechten Konstruktion (DFM) abhängig, gewährleistet zuverlässige Lötverbindungen

|

|

Toleranz von Pad zu Pad

|

±0,05 mm (2 mil)

|

Für hochdichte LSI/SMT

|

D. Inspektion und Qualitätsprüfungen

Die neu geätzten Platten werden visuell und über AOI (Automated Optical Inspection) für:

- Über- oder unterätzte Leiterbahnen und Kontakte

- Brücken oder Kurzschlüsse

- Unterbrechungen oder fehlende Strukturen

- Registrierung/Ausrichtung mit vorgebohrten Durchkontaktierungen

Warum die Musterung der äußeren Schicht bei 4-Schicht-PCBs wichtig ist

- Bestückungszuverlässigkeit: Lötfähigkeit, Pad-Größe und Spurbeständigkeit sind hier alle definiert.

- Signalintegrität: Hochgeschwindigkeitssignale, differentielle Paare und Netze mit gesteuerter Impedanz enden auf diesen Schichten, wodurch eine präzise Leiterbahndefinition entscheidend wird.

- Leistungsübertragung: Es verbleibt ausreichend Kupfer für alle Routing- und Wärmeableitungsanforderungen.

Schritt 7: Lötmaske, Oberflächenbeschichtung und Beschriftung

Nachdem die Kupferstrukturierung der äußeren Schichten Ihrer 4-Schicht-Leiterplatte abgeschlossen ist, gilt es nun Haltbarkeit, Lötbarkeit sowie Klarheit für Montage und Wartung im Feld sicherzustellen. Dieser mehrteilige Schritt zeichnet professionelle Mehrschicht-Leiterplattenfertigung aus, indem er die Schaltung schützt, zuverlässiges Löten gewährleistet und eine einfache visuelle Identifizierung sicherstellt.

A. Aufbringung der Lötmaske

Die lötmaske ist eine schützende Polymerbeschichtung – typischerweise grün, aber auch blau, rot, schwarz und weiß sind beliebt –, die auf die Ober- und Unterseite der Leiterplatte aufgebracht wird:

-

Zweck:

- Verhindert Lötbrücken zwischen eng beieinander liegenden Pads und Leiterbahnen.

- Schützt externe Schaltkreise vor Oxidation, chemischen Angriffen und mechanischer Abnutzung.

- Verbessert die elektrische Isolation zwischen Leiterbahnen, wodurch die Signalintegrität erhöht und die elektromagnetische Störstrahlung (EMI) reduziert wird.

Anwendungsvorgang:

- Beschichtung: Die Platine ist mit einer flüssigen, photobildbaren Lötmaske (LPI) beschichtet, die alles außer den Kupferpads abdeckt, die später verlötet werden.

- Abbildung und Belichtung: UV-Licht wird zusammen mit einer Belichtungsmaske verwendet, um Öffnungen (für Pads, Prüfpunkte, Durchkontaktierungen) zu definieren.

- Entwicklung: Nicht belichtete Lötmaske wird ausgewaschen, während die belichtete aushärtet und so die Schaltkreise schützt.

- Einhärten: Die Platinen werden gebacken oder mittels UV-Licht ausgehärtet, um die Lötmaske vollständig zu verfestigen.

B. Oberflächenbeschichtungsoptionen

Um sicherzustellen, dass alle freiliegenden Pads Lagerung überstehen, oxidationsbeständig sind und während der Bestückung einwandfreie Lötbarkeit bieten, wird eine oberflächenbearbeitung aufgebracht. Es gibt verschiedene Beschichtungsarten, die je nach Anwendung, Kosten und Fertigungsanforderungen geeignet sind:

|

Oberflächenbearbeitung

|

Akronym

|

Hauptvorteile

|

Typische Anwendungsfälle

|

|

Nickel-Beschichtung durch Immersion mit Goldauflage

|

ENIG

|

Flach, oxidationsgeschützt, geeignet für Feinraster/BGA; hervorragende Lötbarkeit, RoHS-konform

|

Hochzuverlässig, HDI, Consumer, HF

|

|

Organischer Lötbarkeitsschutz

|

Ausrüstung

|

Sauber, bleifrei, kostengünstig; schützt blankes Kupfer und eignet sich gut für Reflow-Löten

|

Massenmarkt, einfache SMT

|

|

Immersionszinn

|

—

|

Planar, gut geeignet für Press-Fit- oder Hochgeschwindigkeits-Steckverbinder

|

Kontrollierte Impedanz, Press-Fit-Platinen

|

|

Tauchsilber

|

—

|

Ausgezeichnet für Hochfrequenz/Signalintegrität

|

HF, Hochgeschwindigkeitsdigital

|

|

Heißluft-Lötebenen / bleifreies HASL

|

HASL

|

Weit verbreitet, kostengünstig, robust; geschmolzene Lötbeschichtung

|

Allgemeine Elektronik, THT/SMT gemischt

|

- ENIG ist Industriestandard für die meisten 4-lagigen Prototypen- und Serienplatinen, insbesondere dort, wo Oberflächenflachheit und hohe Dichte (BGA, LGA, QFN) wichtig sind.

- Ausrüstung ist am besten für bleifreie Consumer-Elektronik geeignet, die Kosteneffizienz und gute Lötverbindungsgüte erfordert.

Unterschiede zwischen ENIG und HASL:

- ENIG bietet eine glattere und ebenere Oberfläche, die für ultrakleine Abstände und BGAs erforderlich ist.

- HASL erzeugt ungleichmäßige „Kuppeln“, die sich möglicherweise nicht für moderne hochdichte Leiterplattenmontage eignen.

- ENIG ist teurer, bietet aber bessere Langzeitlagerfähigkeit und Kompatibilität für Drahtbondverbindungen.

C. Siebdruck

Mit Lötstopplack und Oberflächenbeschichtung ist die letzte Schicht die seidenfett —verwendet zur Kennzeichnung von:

- Bauteile-Umrissen und Beschriftungen (R1, C4, U2)

- Polaritätsmarkierungen

- Bezugskennzeichen

- Pin-1-Kennzeichnungen, Logos, Revisionscodes und Barcodes

Qualitätskontrolle: Endgültige AOI- und Sichtprüfung

- Automatische optische Inspektion (AOI): Stellt sicher, dass die Größe/Platzierung der Öffnungen im Lötstopplack korrekt ist, kein unerwünschter Lötstopplack vorhanden ist und die richtigen Pads freigelegt sind.

- Sichtprüfung: Bestätigt die Klarheit des Siebdrucks, das Fehlen von fehlender Tinte, dass kein Lötstopplack über wichtigen Merkmalen liegt, und überprüft die Integrität der Oberflächenbeschichtung.

Warum dieser Schritt bei 4-Lagen-Leiterplatten wichtig ist

- Lötfähigkeit: Nur die freiliegenden Pads/Berührungspunkte sind zum Löten zugänglich; das Abdecken des Rests verhindert versehentliche Kurzschlüsse – besonders wichtig bei dichten Layouts.

- Korrosions- und Kontaminationsbeständigkeit: Die Lebensdauer und Zuverlässigkeit der Leiterplatte werden deutlich verbessert, da Kupferflächen vor Luft, Feuchtigkeit und Fingerabdrücken geschützt werden.

- Fehlerreduzierung: Starke, genaue Kennzeichnungen reduzieren Montagefehler, Nacharbeit oder Wartungszeiten vor Ort.

Schritt 8: PCB-Bearbeitung, Bestückung und Reinigung

Nachdem alle Schaltkreisebenen festgelegt, die Durchkontaktierungen beschichtet und die Lötmaske sowie Oberflächenbeschichtung aufgebracht wurden, liegt der Fokus nun auf Formgebung, Bestückung und Reinigung der 4-Lagen-PCB . In dieser Phase wird Ihre mehrschichtige Platine von einem präzise gefertigten, aber nicht individualisierten Block zu einem formfaktorspezifischen, vollständig bestückten Funktionsträger.

A. PCB-Bearbeitung (Schneiden und Fräsen)

An diesem Punkt befinden sich mehrere PCB-Ausführungen auf einer größeren Produktionsplatine. Profilieren bedeutet, jede vierlagige Leiterplatte auf ihre erforderliche Kontur zu trennen, einschließlich Ausschnitte, Schlitze oder V-Nuten.

Wichtige Verfahren:

- CNC-Fräser : Hochgeschwindigkeits-Hartmetallfräswerkzeuge folgen präzise dem äußeren Rand der Platine und erfüllen Toleranzvorgaben bis hin zu ±0,1 mm.

- V-Scoring : Flache Rillen ermöglichen ein einfaches Ablösen der Platinen durch Abknicken entlang der Ritzlinien.

- Stanzen : Wird bei Serienfertigung und standardmäßigen Formen eingesetzt, um den Durchsatz zu optimieren.

B. Leiterplattenbestückung (SMT & THT-Bauteilplatzierung)

Die meisten vierlagigen Leiterplatten verwenden heute eine Mischtechnologie-Bestückung unter Nutzung beider Technologien Surface Mount Technology (SMT) für hochdichte, automatisierte Bestückung, sowie Through-Hole Technology (THT) für hochfeste Steckverbinder, Leistungskomponenten oder ältere Bauteile.

1. SMT-Bestückung

- Schablonendruck : Lötpaste wird mithilfe von laserbeschnittenen Schablonen präzise dosiert auf die Kontaktflächen aufgedruckt.

- Bestückung : Automatisierte Maschinen setzen bis zu mehrere zehntausend Bauteile pro Stunde mit mikrometergenauer Präzision auf – auch für 0201-Passive, QFNs, BGAs oder LSI-Bauteile.

- Wiedererwärmungslöten : Bestückte Leiterplatten durchlaufen einen sorgfältig profilierten Heißluftofen, in dem das Lot schmilzt und anschließend kontrolliert abkühlt. Dadurch entstehen feste Lötverbindungen für alle SMT-Bauteile.

2. THT-Bestückung

- Manuelle oder automatische Einfügung : Bauteile mit langen Anschlüssen, wie Steckverbinder oder große Elektrolytkondensatoren, werden durch metallisierte Durchkontaktierungen gesteckt.

- Wellensolder : Die Leiterplatten bewegen sich über eine Welle aus flüssigem Lot, wodurch alle eingesteckten Anschlüsse gleichzeitig verlötet werden – eine bewährte Methode für hohe mechanische Festigkeit.

SMT im Vergleich zu THT:

- SMT ermöglicht hochdichte, leichte und kompakte Baugruppen. Ideal für moderne mehrlagige Leiterplatten.

- Die wird weiterhin bevorzugt für Steckverbinder und Leistungskomponenten, die zusätzliche Verankerung benötigen.

C. Reinigung (Isopropylalkohol und spezielle PCB-Reiniger)

Nach dem Löten können Rückstände wie Flussmittel, Lötperlen und Staub die Zuverlässigkeit beeinträchtigen, insbesondere auf den eng beieinander liegenden Leiterbahnen und Durchkontaktierungen von vierlagigen Leiterplatten.

Prozessschritte:

- Reinigung mit Isopropylalkohol (IPA) : Wird häufig beim Prototyping und bei Kleinserien angewendet, um ionische Rückstände und sichtbares Flussmittel manuell zu entfernen.

- In-Line-PCB-Reiniger : Industrielle Reiniger verwenden entionisiertes Wasser, Saponifikationsmittel oder spezielle Lösungsmittel, um mehrere Leiterplatten gleichzeitig zu reinigen – entscheidend in medizinischen, militärischen und automobilen Anwendungen.

Warum Reinigung wichtig ist:

- Verhindert Korrosion und dendritisches Wachstum zwischen Leiterbahnstrukturen.

- Verringert das Risiko elektrischer Leckströme, besonders bei Hochimpedanz- oder Hochspannungsschaltungen.

Tabelle: Übersicht über Montage- und Reinigungsprozess

|

Bühne

|

Technik

|

Vorteile

|

Typische Anwendungen

|

|

Profilieren

|

CNC-Fräsen, V-Berstung

|

Präzision, spannungsfreie Kanten

|

Alle Platinentypen

|

|

SMT-Montage

|

Schablone/Lötpaste-Auftrag

|

Hohe Dichte, Geschwindigkeit, Genauigkeit

|

Massenmarkt, hohe Dichte

|

|

THT-Montage

|

Wellensolder

|

Robuste Verbindungen, handhabt sperrige Teile

|

Stromversorgung, Steckverbinder

|

|

Reinigung

|

IPA oder In-Line-Reiniger

|

Entfernt Rückstände, gewährleistet Zuverlässigkeit

|

Alle, besonders kritisch

|

Schritt 9: Endprüfung, Qualitätskontrolle (QC) und Verpackung

A 4-Lagen-PCB ist nur so gut wie die Strenge seiner Prüf- und Qualitätskontrollverfahren. Selbst wenn es optisch makellos erscheint, können unsichtbare Fehler – Kurzschlüsse, Unterbrechungen, Fehlausrichtungen oder unzureichende Beschichtung – zu fehlerhaftem Verhalten, vorzeitigen Ausfällen oder Sicherheitsrisiken führen. Deshalb setzen erstklassige Leiterplattenhersteller eine umfassende Palette elektrischer, visueller und dokumentationsbasierter Inspektionen ein, die auf international anerkannten IPC-Standards basieren.

A. Automatische optische Inspektion (AOI)

Automatische optische Inspektion (AOI) wird mehrfach während der Mehrschicht-Leiterplattenfertigung durchgeführt, wobei der wichtigste Durchlauf nach der endgültigen Montage und dem Löten erfolgt.

- Wie es funktioniert: Hochauflösende Kameras scannen beide Seiten jeder Leiterplatte und vergleichen jede Leiterbahn, jeden Lötanschluss und jedes Lotfeld mit den digitalen Gerber-Dateien.

-

Was die AOI erkennt:

- Unterbrechungen (unterbrochene Leiterbahnen)

- Kurzschlüsse (Lötbrücken)

- Fehlende oder verschobene Bauteile

- Lötstellen mit unzureichendem oder übermäßigem Lot

- Tombstoning oder Bauteilverriegelung

B. In-Circuit-Prüfung (ICT)

In-Circuit-Test (ICT) ist der Goldstandard zur Überprüfung der Funktionalität von bestückten 4-Lagen-Leiterplatten:

- Kontaktierungsproben: Bed-of-Nails- oder Flying-Probe-Tester stellen Kontakt mit dedizierten Prüfpunkten oder Bauteilepins her.

- Testskripte: Leiten Signale durch die Schaltung und messen die Reaktionen an wichtigen Knotenpunkten.

-

Geprüfte Parameter:

- Durchgangsprüfung zwischen allen Signal- und Stromversorgungspunkten

- Widerstand/Kapazität von Schlüsselnetzen

- Integrität von Durchkontaktierungen und metallisierten Bohrungen

- Vorhandensein/Abwesenheit und Ausrichtung der Hauptkomponenten

ICT ermöglicht:

- Unmittelbare, baugruppenebene Diagnose (genaue Lokalisierung fehlerhafter Lötstellen, Unterbrechungen oder falsch platzierte Bauteile)

- Statistiken auf Chargenebene zur Prozessüberwachung

C. Elektrische Prüfung

Jedes fertige vierlagige Leiterplatte unterzieht sich einem vollständigen elektrischen Durchgangs- und Kurzschlusstest. In diesem Schritt:

- Elektrische Prüfung (ET): Eine Hochspannung wird über alle Leiterbahnen und Verbindungen angelegt.

- Ziel: Erkennen Sie versteckte Unterbrechungen („Opens“) oder Kurzschlüsse („Shorts“, unbeabsichtigte Brücken), unabhängig vom optischen Erscheinungsbild.

Für impedanzgesteuerte Designs:

- Impedanz-Teststrukturen: Testleiterbahnen, die aus dem gleichen Schichtaufbau und Herstellprozess wie die Serienleitungen bestehen, ermöglichen die Messung und Validierung der charakteristischen Impedanz (z. B. 50 Ω single-ended, 90 Ω differentiell).

D. Dokumentation und Rückverfolgbarkeit

- Gerber-, Bohr- und Testdateien: Der Hersteller stellt alle kritischen Daten zusammen und archiviert sie, um die Rückverfolgbarkeit von der Materialcharge bis zur fertigen Platine sicherzustellen.

- Bestückungspläne und Qualitätsprüfungszertifikate: Werden bei hochzuverlässigen Lieferungen mitgeliefert, um die Einhaltung von ISO9001/ISO13485-, Medizin- oder Automobilstandards zu gewährleisten.

- Barcode: Seriennummern und Barcodes werden auf jede Platine oder jedes Panel gedruckt, um die Verfolgung, Fehlersuche und die Referenzierung mittels „digitaler Zwilling“ zu ermöglichen.

E. Endgültige visuelle Inspektion und Verpackung

Ausbildete Prüfer führen eine letzte Überprüfung mithilfe von Vergrößerung und Hochleistungsbeleuchtung durch, um kritische Merkmale zu untersuchen:

- Sauberkeit von Lötflächen und Durchkontaktierungen (keine Lötperlen oder Rückstände)

- Klarheit von Beschriftungen und Kennzeichnungen, Ausrichtung sowie Genauigkeit des Revisionscodes

- Qualität der Kanten und Konturierung (keine Delamination, Absplitterungen oder Beschädigungen)

Verpackung:

- Vakuumverpackte antistatische Beutel schützen vor elektrostatischer Entladung (ESD) und Feuchtigkeitseintritt

- Luftpolsterfolie, Schaumstoff oder maßgeschneiderte Einsätze verhindern mechanische Erschütterungen während des Transports

- Jede Charge wird gemäß Kundenanweisungen verpackt, einschließlich Trockenmittelpackungen oder Feuchtigkeitsindikatoren für Märkte mit hohen Zuverlässigkeitsanforderungen

Tabelle: Prüf- und Qualitätskontrollstandards für 4-Lagen-Platinen

|

Test/Inspektion

|

Standard/Referenz

|

Was es sichert

|

|

AOI

|

IPC-610, ISO9001

|

Sichtbar fehlerfreier Aufbau

|

|

Elektrische Prüfung (ET)

|

IPC-9252

|

Keine Kurzschlüsse/Unterbrechungen

|

|

ICT/Flying Probe

|

Kundenspezifisch/IPC-2222

|

Funktionalität, pin-spezifischer Test

|

|

Impedanzprüfung

|

IPC-2141A, Teststrukturen

|

Einhaltung von Übertragungsleitungsanforderungen

|

|

Sichtprüfung

|

IPC-A-610, ISO13485

|

Optische und mechanische Qualität

|

So erstellen Sie einen 4-Lagen-Aufbau in Altium Designer

Kontrolle Ihrer 4-Schicht-PCB-Aufbau ist entscheidend, um die richtige Balance zwischen elektrischer Leistung, Herstellbarkeit und Kosten zu erreichen. Moderne PCB-Design-Tools wie Altium Designer bieten intuitive, leistungsstarke Schnittstellen, um alle Details festzulegen – und später zu exportieren –, die Hersteller für die qualitativ hochwertige und zuverlässige Fertigung mehrlagiger Leiterplatten benötigen.

Schritt-für-Schritt: Definition Ihres 4-Schicht-PCB-Aufbaus

1. Starten Sie Ihr Projekt in Altium

- Öffnen Sie Altium Designer und erstellen Sie ein neues PCB-Projekt.

- Importieren oder zeichnen Sie Ihre Schaltpläne und stellen Sie sicher, dass alle Komponenten, Leiterbahnen und Vorgaben definiert sind.

2. Zugriff auf den Layer-Stapel-Manager

- Gehen Sie zu Design → Layer-Stapel-Manager.

- Der Layer-Stapel-Manager ermöglicht es Ihnen, alle leitfähigen und dielektrischen Schichten, Dicken und Materialien zu konfigurieren.

3. Fügen Sie vier Kupferschichten hinzu

- Standardmäßig sehen Sie die Oberste Schicht und die Unterste Schicht.

- Hinzufügen zwei innere Schichten (typischerweise MidLayer1 und MidLayer2) für Ihren Aufbau mit vier Schichten.

4. Definieren Sie die Funktionen der Schichten

Weisen Sie jeder Schicht typische Funktionen wie folgt zu:

|

Schicht

|

Typische Funktion

|

Schichtaufbau-Beispiel

|

|

OBEN

|

Signal + Bauteile

|

L1 (Signal)

|

|

MidLayer1

|

Erdungsebene

|

L2 (Boden)

|

|

MidLayer2

|

Spannungsebene (VCC etc)

|

L3 (Spannungsversorgung)

|

|

Unteres Ende

|

Signal / Komponenten

|

L4 (Signal)

|

5. Dielektrikum-/Prepreg- und Kerndicken konfigurieren

- Klicken Sie zwischen den Schichten, um die Dielektrikumdicke (Prepreg, Kern) mithilfe von herstellerspezifischen Werten festzulegen .

- Typische Gesamtdicke für eine 4-lagige Leiterplatte: 1,6 mm (kann jedoch je nach Bedarf dünner/dicker sein).

- Geben Sie die Dielektrizitätskonstante (Dk) und den Verlustfaktor an, insbesondere bei impedanzgesteuerten Designs.

6. Kupfergewicht festlegen

- Geben Sie die Kupferdicke für jede Lage an: üblicherweise 1 oz/ft² (~35 μm) ist Standard für Signallagen; 2 Oz oder mehr für stromstarke Leistungen.

- Diese Werte beeinflussen die Spurbreitenberechnungen und die mechanische Belastbarkeit.

7. Impedanzberechnungen aktivieren

- Verwenden Sie den eingebauten Impedanzrechner (oder Link zu dem Tool Ihres Herstellers), um Einzel- und Differentialpaar-Impedanzen basierend auf Ihren Angaben zu Material, Dicke und Breite/Abstand zu berechnen.

- Typische Ziele: 50 Ω einzeln , 90–100 Ω differentiell .

- Passen Sie die Dielektrikumdicke, Leiterbahnbreite und Kupfergewicht nach Bedarf an, um diese Ziele zu erreichen.

8. Erstellen der Schichtaufbau-Zeichnung

- Exportieren Sie eine schichtaufbau-Zeichnung (DXF, PDF usw.) für Ihre Fertigungshinweise. Dies hilft, Kommunikationsfehler zu vermeiden und beschleunigt die DFM-Prüfung.

9. Erstellen und Exportieren von Gerber- und Bohrdateien

- Richten Sie die endgültige Schichtaufbau-Bestätigung für den Leiterplatten-Umriss, die Reihenfolge der Schichten und die Anmerkungen ein.

- Alle exportieren Gerber-Dateien, Bohrdateien und Schichtaufbau-Diagramme mit präziser Benennung (einschließlich Schichtnamen, die mit Ihrem Schichtaufbau-Manager übereinstimmen).

Fallstudie: Optimierung eines 4-Schicht-PCB-Schichtaufbaus für Hochgeschwindigkeitssignale

Szenario: Ein Telekommunikations-Startup entwickelte einen neuen Router mithilfe von Altium Designer. Die größte Herausforderung bestand darin, Signalübersprechen zu reduzieren und USB/Ethernet-Signale innerhalb enger Impedanztoleranzen zu halten.

Lösung:

- Verwendete den Layer Stack Manager von Altium, um [Signal | Masse | Stromversorgung | Signal] mit einem 0,2-mm-Prepreg zwischen äußeren und internen Ebenen zu erstellen.

- Kupfergewichte einstellen auf 1 Oz für alle Schichten.

- Verwendung des Impedanzrechners von Altium und Abstimmung der Materialien mit dem Hersteller, schnelles Iterieren, bis die Messungen 50Ω- und 90Ω-Ziele innerhalb von ±5 % .

- Ergebnis: Die erste Charge bestand die EMC- und Hochgeschwindigkeits-Signalintegritätsprüfungen – wodurch die Zertifizierung beschleunigt und Entwicklungszeit eingespart wurde.

Warum das Schichtaufbau-Design in Altium für 4-Lagen-PCBs wichtig ist

- Verhindert kostspielige Neukonstruktionen: Frühzeitige Planung des Schichtaufbaus unter Einbeziehung des Herstellers verhindert Verzögerungen und gewährleistet einen reibungslosen Übergang vom Prototypen zur Produktion.

- Ermöglicht DFM-Prüfungen: Gut dokumentierte Schichtaufbauten helfen, DRC-/DFM-Unstimmigkeiten zu erkennen, bevor die Leiterplatten gefertigt werden.

- Unterstützt erweiterte Funktionen: Eine genaue Schichtaufbaukontrolle ist erforderlich für Technologien wie Via-in-Pad, blinde/vergrabene Vias und Routing mit gesteuerter Impedanz.

Best Practices für 4-Lagen-PCB-Schichtaufbau und Layout

Ein robuster 4-Schicht-PCB-Aufbau ist nur die halbe Gleichung – echte Leistung, Zuverlässigkeit und Ausbeute ergeben sich aus der konsequenten Anwendung bewährter Methoden im Layout und Design. Wenn Sie Schichtaufbau, Routing, Entkopplung und thermische Pfade gezielt optimieren, führt Ihr Fertigungsprozess für Vierlagige Leiterplatten zu Platinen, die in Signalintegrität, EMV, Herstellbarkeit und Lebensdauer hervorragend abschneiden.

1. Überlegungen zur Signal- und Stromversorgungsintegrität

Gesteuerte Signalrückführwege und saubere Stromverteilung sind die Grundlage beim Mehrschicht-PCB-Design. So machen Sie es richtig:

- Leiten Sie Signale auf den äußeren Lagen (L1, L4) und verwenden Sie die inneren Lagen (L2, L3) als durchgehende Masse- (GND) und Versorgungsebenen (VCC).

- Niemals unterbrechen Sie innere Ebenen nicht durch große Ausschnitte oder Schlitze – halten Sie die Ebenen stattdessen durchgängig. Gemäß IPC-2221/2222 , können Unstetigkeiten dazu führen, dass die definierte Impedanz um 5–15 % abweicht, was zu Signalverschlechterung oder intermittierenden Ausfällen führen kann.

- Kurze Signalrückführwege: Hochgeschwindigkeits- und störempfindliche Signale sollten immer direkt darunter eine durchgängige Bezugsebene „sehen“. Dies verringert die Schleifenfläche und unterdrückt abgestrahlte elektromagnetische Störungen (EMI).

Tabelle: Typische Verwendung von 4-Schicht-Leiterplatten-Aufbauten

|

Option

|

L1

|

L2

|

L3

|

L4

|

Bestes für

|

|

Standard

|

Signal

|

Erde

|

Leistung

|

Signal

|

Allgemein, definierte Impedanz, EMV

|

|

Alternierend

|

Signal

|

Leistung

|

Erde

|

Signal

|

Verbesserte Entkopplung von Strom- und Masseebene

|

|

Brauch

|

Signal/Stromversorgung

|

Erde

|

Erde

|

Signal/Stromversorgung

|

HF, GHz, ultrastille digitale Schaltungen

|

2. Bauteilplatzierung und Entkopplung

- Gruppieren Sie Hochgeschwindigkeits-ICs nahe Steckverbindern oder Quellen/Lasten, um Leiterbahnlängen und Via-Anzahl zu minimieren.

- Platzieren Sie Entkopplungskondensatoren möglichst nahe (vorzugsweise direkt über Vias zur Versorgungsebene), um eine stabile lokale VCC sicherzustellen.

- Wichtige Leitungen zuerst: Leiten Sie Hochfrequenz-, Takt- und empfindliche analoge Leitungen vor weniger kritischen Signalen.

Best Practice: Verwenden Sie die „Fanout“-Technik: Führen Sie Signale von BGAs und feinrasterigen Gehäusen mit kurzen Leiterbahnen und direkten Vias ab – minimiert Übersprechen und Stub-Effekte.

3. Leiterbahnenführung für gesteuerte Impedanz

- Leiterbahnbreite und -abstand: Berechnen und in den Designregeln festlegen für 50 Ω Single-Ended und 90–100 Ω Differentialpaare unter Verwendung der korrekten Stackup-Einstellungen (Dielektrikumdicke, Dk, Kupfergewicht).

- Stub-Länge minimieren: Vermeiden Sie unnötige Umschichtungen zwischen Lagen und verwenden Sie Back-Drilling für kritische Signale, um nicht genutzte Via-Anteile zu entfernen.

- Übergänge zwischen Schichten: Platzieren Sie differentielle Paare nach Möglichkeit auf derselben Schicht und vermeiden Sie unnötige Übergänge.

4. Via-Strategie und Vernähen

- Verwenden Sie Via-Stitching auf durchgängigen Massebenen —umgeben Sie Hochgeschwindigkeitssignale, Taktleitungen und HF-Bereiche mit eng beabstandeten Masse-Vias (normalerweise alle 1–2 cm).

- Optimieren Sie die Via-Größe und das Aspektverhältnis: IPC-6012 empfiehlt, dass die Aspektverhältnisse (Platinenstärke zu Endlochgröße) im Allgemeinen 8:1 für hohe Zuverlässigkeit nicht überschreiten sollten.

- Back-drilled Vias: Verwenden Sie bei extrem hohen Geschwindigkeiten Back-Drilling, um Via-Stümpfe zu entfernen und Signalreflexionen weiter zu reduzieren.

5. Thermisches Management und Kupferausgleich

- Thermische Durchkontaktierungen: Platzieren Sie Arrays von thermischen Durchkontaktierungen unter stark wärmenden ICs/LDOs, um die Wärme an die Masseebene weiterzuleiten und abzuleiten.

- Kupferfüllung: Verwenden Sie eine ausgewogene Kupferverteilung auf beiden Außenschichten, um Verziehen oder Verwinden bei größeren oder leistungsstarken Leiterplatten zu verhindern.

- Gesteuerte Kupferfläche: Vermeiden Sie große, nicht verbundene Kupferinseln, die Spannungskopplung oder elektromagnetische Störungen (EMI) verursachen können.

6. EMV-Abschirmung und Vermeidung von Übersprechen

- Senkrechte Signalverlegung: Verlegen Sie Signale auf L1 und L4 im rechten Winkel zueinander (z. B. L1 in Ost-West-Richtung, L4 in Nord-Süd-Richtung) – dies reduziert kapazitive Kopplung und Übersprechen durch die Ebenen.

- Halten Sie Hochgeschwindigkeitssignale von den Platinecken fern , und vermeiden Sie paralleles Verlegen zur Kante, da dies mehr elektromagnetische Störungen (EMI) abstrahlen kann.

7. Überprüfung durch Simulation und Rückmeldung des Herstellers

- Führen Sie Signalintegritäts-Simulationen vor und nach dem Layout durch für kritische Leiterbahnen oder Schnittstellen.

- Prüfen Sie den Schichtenaufbau und Routing-Vorgaben mit Ihrem gewählten 4-Lagen-PCB-Hersteller —unter Nutzung ihrer Erfahrung, um Herstellbarkeits- und Zuverlässigkeitsrisiken früh im Prozess auszuschließen.

Zitat von Ross Feng: „Bei Viasion haben wir festgestellt, dass disziplinierte Best Practices auf der Entwurfsebene – solide Masseflächen, disziplinierte Via-Nutzung, durchdachte Beziehung von Leiterbahnen und Flächen – zu zuverlässigeren 4-Lagen-Platinen, geringeren EMI und kürzeren Debugging-Phasen für unsere Kunden führen.“

Zusammenfassungstabelle: Empfehlungen und Warnhinweise für das Layout von 4-Lagen-PCBs

|

Empfehlungen

|

Nichts

|

|

Verwenden Sie durchgehende Masse- und Stromebenen

|

Gebrochene innere Ebenen vermeiden; Schlitze vermeiden

|

|

Entkopplungskondensatoren nahe den Stromdurchkontaktierungen platzieren

|

Hochgeschwindigkeitssignale ohne Referenzebene führen

|

|

Geregelte Impedanz berechnen und sicherstellen

|

Herstellerangaben zur Schichtaufbau ignorieren

|

|

Aspektverhältnis und Abstand von Durchkontaktierungen optimieren

|

Stummel/Wechsel der Ebenen unnötig überstrapazieren

|

|

Kupferausgleich verwenden, um Verzug zu vermindern

|

Große, nicht verbundene Kupferflächen belassen

|

Faktoren, die die Kosten von 4-Lagen-PCBs beeinflussen

Kostenkontrolle ist ein zentrales Anliegen für jeden technischen Leiter, Konstrukteur und Einkaufsspezialisten, der mit 4-Lagen-PCBs arbeitet. Das Verständnis der Variablen, die die Preisgestaltung bei der Mehrschicht-Fertigung beeinflussen, ermöglicht fundierte, kosteneffiziente Entscheidungen – ohne Abstriche bei Signalqualität, Zuverlässigkeit oder Produktfunktionen.

1. Materialauswahl

-

Typen von Kernmaterialien und Prepreg:

- Standard-FR-4: Am kostengünstigsten, geeignet für die meisten kommerziellen und industriellen Anwendungen.

- High-TG-, Low-Loss- oder HF-Materialien: Rogers, Teflon und andere Spezialsubstrate sind für Hochfrequenz-, Hochzuverlässigkeits- oder thermisch kritische Konstruktionen unerlässlich, können jedoch die Materialkosten um das 2- bis 4-fache erhöhen.

-

Kupferdicke:

- 1 oz (35µm) ist der Standard; die Aufrüstung auf 2 oz oder mehr für Leistungsebenen oder thermisches Management erhöht sowohl Material- als auch Verarbeitungskosten.

-

Oberflächenfinish:

- ENIG (Chemisches Nickel-Immersionsgold): Höhere Kosten, aber erforderlich für feine Raster, hohe Zuverlässigkeit oder Drahtbondverbindungen.

- OSP, HASL, Immersions-Silber/Zinn: Günstiger, kann jedoch Einschränkungen hinsichtlich Haltbarkeit oder Flachheit aufweisen.

2. Plattendicke und Abmessungen

- Standarddicke (1,6 mm) ist am kostengünstigsten, da sie die Ausnutzung der Platte optimiert und spezielle Bearbeitungsschritte minimiert.

- Sonderdicken, sehr dünne (<1,0 mm) oder dicke (>2,5 mm) platinen erfordern besondere Handhabung und können die Auswahl an Herstellern einschränken.

Tabelle: Beispielhafte Platattendicken und typische Anwendungen

|

Dicke

|

Anwendungen

|

Kostenauswirkung

|

|

1,0 mm

|

Wearables, tragbare Geräte mit hoher Dichte

|

Neutral

|

|

1,6 mm

|

Allgemeine Anwendung, Industriestandard

|

Tiefster Punkt

|

|

2,0+ mm

|

Leistung, Steckverbinder, mechanische Belastung

|

10–20 % höher

|

3. Komplexität des Entwurfs

- Leiterbahnbreiten: <=4 mil erhöhen die Kosten aufgrund einer höheren Ausschussrate und langsameren Ausbeute.

- Minimale Via-Größe: Mikroviass, blinde/geladene Vias oder Via-in-Pad erhöhen den Fertigungsaufwand erheblich.

- Anzahl der Lagen: Die vierlagige Leiterplatte ist der „Kern“ von multilagigen Massenprodukten; das Hinzufügen weiterer Lagen (6, 8, 12 usw.) oder nicht standardmäßiger Schichtaufbauten erhöht den Preis proportional.

4. Panelisierung und Ausnutzung

- Große Paneele (mehrere Leiterplatten pro Panel) maximieren Durchsatz und Materialausnutzung und halten die Kosten pro Leiterplatte niedrig.

- Unregelmäßig geformte oder große Leiterplatten (die mehr Abfall oder spezielle Werkzeuge erfordern) verringern die Paneldichte und Kosteneffizienz.

5. Besondere Bearbeitungsanforderungen

- Geregelte Impedanz: Erfordert engere Toleranzen bei Spurweite, Abstand und Dielektrikumdicke – kann zusätzliche QA-/Prüfschritte erfordern.

- Goldkontakte, Aussparungen, Rillen, Kantenvergoldung: Jeder nicht standardmäßige mechanische oder Oberflächenprozess erhöht die NRE-Kosten (nicht wiederkehrende Engineeringkosten) und die Kosten pro Bauteil.

- Sequentielle Lamination, Hinterbohren: Unverzichtbar für Blinde-/Vergrabene Vias oder Hochgeschwindigkeitsdesigns, fügt jedoch zusätzliche Schritte, Zeit und Komplexität hinzu.

6. Menge und Lieferzeit

- Prototypen und Kleinserien: Typischerweise 10–50 USD/Platine, abhängig von den Funktionen, da die Rüstkosten auf weniger Einheiten verteilt werden.

- Mittlere bis hohe Mengen: Die Stückkosten sinken stark – besonders wenn Ihr Design plattenoptimiert ist und gängige Spezifikationen verwendet.

- Schnelllieferung: Beschleunigte Fertigung/Lieferung (sogar innerhalb von 24–48 Stunden) verursacht Zuschläge – planen Sie nach Möglichkeit im Voraus.

7. Zertifizierungen und Qualitätsmanagement

- UL, ISO9001, ISO13485, Umweltkonformität: Zertifizierte Anlagen und Dokumentation sind teurer, aber erforderlich für Automobil-, Medizin- und anspruchsvolle kommerzielle Projekte.

Kostenvergleichstabelle: Beispielangebote für 4-Lagen-PCB

|

Funktion

|

Einfaches FR-4, OSP

|

ENIG, High-TG, Impedanzsteuerung

|

|

1,6 mm, 1 Unze, minimale Bohrung 0,3 mm, Standardoberfläche

|

15–25 $ pro Platine (Menge 10)

|

30–60 $ pro Platine (Menge 10)

|

|

2,0 mm, 2 Unzen, ENIG, 4 mil/4 mil, gesteuerte Impedanz

|

30–45 $ pro Platine (Menge 10)

|

45–70 $ pro Platine (Menge 10)

|

|

Starre-flexible Hybridbauweise (gleiche Abmessungen)

|

$60–$100+

|

Nicht üblich

|

So erhalten Sie den besten Wert aus der Fertigung von 4-Lagen-PCBs

- Stellen Sie vollständige Schichtaufbau- und mechanische Zeichnungen von Anfang an bereit

- Reagieren Sie schnell auf DFM-Rückmeldungen und überarbeiten Sie für die Fertigungsgerechtheit

- Wählen Sie bewährte, zertifizierte Lieferanten aus Shenzhen oder globalen Quellen

- Optimieren Sie das Array-/Plattendesign für die Serienproduktion

- Arbeiten Sie mit Lieferanten wie Viasion Technology zusammen, die eine interne Kostenoptimierung und kostenlose DFM-Dateiprüfungen anbieten

Den richtigen Hersteller für 4-Lagen-PCBs wählen

Die Entscheidung dafür, wo wo sie haben Ihr 4-Lagen-PCB hergestellt wird, kann erhebliche Auswirkungen auf die Kosten Ihres Projekts, die elektrische Leistung, die Produktionsdurchlaufzeit und die langfristige Zuverlässigkeit des Geräts haben. Obwohl die Herstellung von 4-Lagen-PCBs ein etablierter Prozess ist, liefern nur einige wenige Lieferanten konsequent die Genauigkeit, Wiederholbarkeit und Dokumentation, die Märkte wie Automobil, Industrie, Medizintechnik und Unterhaltungselektronik verlangen.

1. Zertifizierungen und Konformität

Achten Sie auf Hersteller, die zertifiziert sind nach:

- UL (Unterwriters Laboratories): Gewährleistet die Einhaltung der Entflammbarkeitsanforderungen und sichere Betriebseigenschaften.

- ISO 9001 (Qualitätssysteme): Signalisiert eine solide Prozesssteuerung und Dokumentation von der Konzeption bis zum Versand.

- ISO 13485 (Medizinisch): Erforderlich für medizinische Leiterplattenbaugruppen und -geräte.

- Umwelt (RoHS, REACH): Zeigt die Kontrolle über gefährliche Stoffe und die Konformität mit globalen Marktanforderungen an.

2. Technische Fähigkeiten und Erfahrung

Ein erstklassiger Hersteller von 4-Lagen-Leiterplatten sollte folgende Leistungen anbieten:

- Präzise Schichtaufbaukontrolle: In der Lage, enge Toleranzen bei Dielektrikumdicke, Kupfergewichten und Via-Geometrien einzuhalten.

- Fortgeschrittene Via-Technologien: Durchkontaktierungen, blinde/vergrabene Vias, Via-in-Pad und Back-Drilling für Hochgeschwindigkeits-, Hochdichte- und kundenspezifische Schichtaufbauten.

- Geregelte Impedanzfertigung: Impedanztest-Coupons vor Ort, abgestimmte Prüfplätze und Fachkompetenz in Einzelstrang/Differential-Leitungen.

- Flexible Platinenpanelisierung: Effiziente Materialausnutzung für verschiedene Leiterplattengrößen und -formen mit internem Beratungsservice zur Senkung Ihrer Kosten pro Leiterplatte.

- Dienstleistungen von A bis Z: Einschließlich schneller Prototypenerstellung, Serienfertigung und zusätzlicher Services wie funktioneller Montage, Konformbeschichtung und Gehäusebau.

3. Kommunikation und Support

Reaktionsfähigkeit und kompetente technische Unterstützung zeichnen gute Leiterplattenlieferanten aus:

- Frühzeitige DFM- und Stackup-Prüfungen: Vor Bezug der Fertigung proaktiv auf DFM- oder Impedanzprobleme hinweisen.

- Englischsprachige Ingenieurteams: Für internationale Kunden gewährleistet dies, dass nichts in der Übersetzung verloren geht.

- Online-Angebotserstellung und -verfolgung: Echtzeit-Angebotswerkzeuge und Bestellstatusverfolgung erhöhen die Transparenz und Genauigkeit der Projektplanung.

4. Dienstleistungen mit Mehrwert

- PCB-Design- und Layoutunterstützung: Einige Lieferanten können Layouts hinsichtlich optimaler Herstellbarkeit oder Signalintegrität prüfen oder gemeinsam entwerfen.

- Beschaffung von Bauteilen und Montage: Komplettmontage verkürzt deutlich die Durchlaufzeiten und Logistik für Prototypen oder Erstserien.

- Vom Prototyp bis zur Massenproduktion: Wählen Sie einen Shop, der mit Ihren Stückzahlen skaliert und eine gleichbleibende Prozesskontrolle von der ersten Platine bis zur millionsten Einheit bietet.

5. Standort und Logistik

- Shenzhen/Guangdong-Region: Weltweites Zentrum für hochwertige, schnelle Mehrschicht-PCB-Fertigung mit ausgereiften Lieferketten, umfangreichen Materialbeständen und leistungsstarker Exportinfrastruktur.

- Optionen in Westen: Amerika oder Europa bieten UL/ISO-zertifizierte Fertigung mit höheren Arbeitskosten – ideal für geringe bis mittlere Stückzahlen, die kurze Lieferzeiten oder besondere gesetzliche Vorgaben erfordern.

So wählen Sie Ihren 4-Lagen-PCB-Hersteller aus

|

Auswahl-Schritt

|

Was prüfen bzw. fragen

|

|

ZERTIFIZIERUNGEN

|

Anfrage und Ansicht von UL-, ISO9001-, ISO13485-, RoHS-Dokumenten

|

|

Musterberichte

|

Prüfung von Querschnitten, Impedanztests, AOI-Bildern

|

|

Reaktionszeiten des technischen Supports

|

Stellen Sie eine Frage zur Schichtenstruktur per E-Mail – sind die Antworten fachlich fundiert und schnell?

|

|

Panelisierung und DFM-Unterstützung

|

Erstellen sie eine Panelisierung Ihrer Gerber-Dateien zur Optimierung?

|

|

Volumenflexibilität

|

Können sie von 5 Prototypen auf über 10.000 Leiterplatten hochskalieren?

|

|

After-Sales-Service

|

Garantie, RMA oder Ursachenanalyse bei Problemen

|

Anwendungen von 4-Lagen-PCBs in der modernen Elektronik

Die Vielseitigkeit, Zuverlässigkeit und Leistungsvorteile von 4-Lagen-PCBs haben sie zur bevorzugten Wahl für ein breites Spektrum moderner elektronischer Anwendungen gemacht. Ihre optimale Kombination aus Signalintegrität, EMI-Reduzierung, Routing-Dichte und Stromversorgung macht die vierlagige Leiterplatte zu einer grundlegenden Technologie in nahezu jedem Marktsegment, in dem Komplexität, Größe oder elektrische Leistung eine Rolle spielen.

1. Unterhaltungselektronik

- Tragbare Geräte und Smart Devices Kompakte Fitness-Tracker, Smartwatches und tragbare Gesundheitsmonitore setzen auf 4-Lagen-PCB-Aufbauten, um fortschrittliche Mikrocontroller, Funkmodule und Sensoren in winzigen Gehäusen unterzubringen.

- Router und Zugangspunkte Hochgeschwindigkeits-Netzwerkgeräte nutzen 4-Lagen-PCB-Fertigungsverfahren mit präziser Impedanzsteuerung, um die Signalqualität für USB 3.x, Wi-Fi und Ethernet-Schnittstellen sicherzustellen.

- Spielekonsolen und Heim-Hubs Dichte PC-Motherboards, Controller und Hochgeschwindigkeits-Datengeräte profitieren von mehrschichtigen Stackups, um Störungen zu reduzieren, das thermische Management zu verbessern und leistungsstarke CPUs sowie diskrete Grafikchips zu unterstützen.

2. Automobil-Elektronik

- Elektronische Steuerungen (ecus) Moderne Fahrzeuge verwenden Dutzende von Steuergeräten, die alle robuste, störfeste mehrschichtige Leiterplatten benötigen, um Antriebsstränge, Airbags, Bremsen und Infotainmentsysteme zu steuern.

- Fortgeschrittene Fahrerassistenzsysteme (ADAS) vierschichtige Leiterplatten-Designs bilden die Grundlage für Radar-, LIDAR- und Hochgeschwindigkeits-Kamerainterfaces, bei denen eine konsistente Signalübertragung und thermische Leistung entscheidend sind.

- Batteriemanagement und Leistungssteuerung Bei Elektrofahrzeugen und Hybriden übernehmen Vierschicht-Stackups die Verteilung von Hochstrom, die Fehlerisolierung und eine zuverlässige Kommunikation zwischen Batteriemodulen.

3. Industrie & Automatisierung

- Gateways und Kommunikationsmodule Industrielle Steuerungsnetzwerke (Ethernet, Profibus, Modbus) verwenden vierlagige Leiterplatten für robuste Schnittstellen und zuverlässige Stromversorgung.

- SPS- und Robotersteuerungen Dichte Layouts, Mixed-Signal-Design und Leistungsisolierung werden effizient mit mehrschichtigen Stackups realisiert, wodurch die Maschinenlaufzeit verbessert und Störgeräusche reduziert werden.

- Prüf- & Messtechnische Instrumente Präzise Analog- und Hochgeschwindigkeits-Digital-Schaltungen erfordern Routing mit kontrollierter Impedanz, Übersprechdämpfung und sorgfältiges PDN-Engineering – alles Stärken der Vierschicht-Leiterplatte.

4. Medizintechnik

- Tragbare Diagnosegeräte und Monitore Von Pulsoximetern bis hin zu mobilen EKGs ermöglicht die Fertigung von 4-Lagen-Leiterplatten Miniaturisierung, Mixed-Signal-Design und zuverlässigen Betrieb in sicherheitskritischen medizinischen Produkten.

- Implantierbare und körpernahe Instrumente Strenge Biokompatibilität, Zuverlässigkeit und geringe elektromagnetische Interferenzen werden durch gut gestaltete Stackups erreicht, zertifiziert nach ISO13485 und IPC-A-610 Klasse 3.

5. IoT, Telekommunikation und Dateninfrastruktur

- Gateways, Sensoren und Edge-Geräte Stromsparende, aber hochdichte IoT-Produkte erreichen Zuverlässigkeit und Leistung durch moderne mehrschichtige Stackups, die häufig drahtlose Technologien, Analog- und Hochgeschwindigkeits-Digital-Schaltungen auf einer kompakten Platine integrieren.

- Hochgeschwindigkeits-Backplanes und -Module Router, Switches und Server nutzen 4-schichtige und komplexere Leiterplatten für schnelle, störfeste Signalübertragung und eine robuste Spannungsversorgungsarchitektur.

Tabelle: Beispielanwendungen und Vorteile des Schichtaufbaus

|

Anwendungstyp

|

vorteile von 4-Schicht-PCBs

|

Typische Schlüsselanforderungen

|

|

Wearables/Konsumenten

|

Kompakt, geringe EMI, hohe Dichte

|

Gesteuerte Impedanz, Miniaturisierung

|

|

Automotive ECU/ADAS

|

Zuverlässigkeit, Störfestigkeit gegen EMI

|

ISO/Fahrzeugstandards, robuste Leistung, SI, EMC

|

|

Industrieroboter

|

Signalintegrität, Haltbarkeit

|

Strom/Masseebenen, erhöhter Routingplatz

|

|

Medizintechnik

|

Geräuschminderung, lange Lebensdauer

|

ISO13485, sauberer Masse/Strom, geringe EMI

|

|

IoT-Gateways

|

RF/Digital-Integration, geringe Größe

|

Sauberer Stackup, flexibler Pinout, Zuverlässigkeit

|

Frequently Asked Questions (FAQ)

1. Wie verbessert eine 4-Lagen-PCB die EMI-Leistung?

A 4-Lagen-PCB ermöglicht eine durchgehende Masseebene direkt unter den Signalschichten, wodurch äußerst effektive Rückführwege für Hochgeschwindigkeitsströme entstehen. Dadurch wird die Schleifenfläche minimiert, EMI-Emissionen stark reduziert und empfindliche Signale vor Störungen abgeschirmt. Im Gegensatz zu 2-Lagen-Platinen absorbieren und leiten die internen Ebenen bei 4-Lagen-Aufbauten abgestrahlte Störungen ab, wodurch Geräte bereits beim ersten Versuch die EMC-Zulassung bestehen können.

2. Wann sollte ich von einer 2-Lagen- auf eine 4-Lagen-PCB upgraden?

Aufwärtssteigen auf 4-Lagen-PCB wenn:

- Sie müssen Hochgeschwindigkeits-Digitalbusse (USB, HDMI, PCIe, DDR usw.) betreiben.