Giới thiệu

Trong thế giới điện tử mật độ cao ngày nay, nhu cầu về các bo mạch đáng tin cậy, nhỏ gọn và có độ bền điện tốt đang không ngừng gia tăng. Mạch in 4 lớp, đôi khi được gọi là bo mạch in bốn lớp, đã trở thành một trong những giải pháp được áp dụng rộng rãi nhất cho các ứng dụng từ thiết bị IoT tiêu dùng đến hệ thống điều khiển công nghiệp và điện tử ô tô.

Mặc dù mạch in hai lớp có thể đủ dùng cho các mạch đơn giản, nhưng các xu hướng công nghệ như tốc độ xung nhịp cao hơn, thiết kế tín hiệu hỗn hợp và kích thước thiết bị nhỏ gọn đòi hỏi độ toàn vẹn tín hiệu tốt hơn, giảm nhiễu điện từ (EMI) và phân phối nguồn tốt hơn — tất cả những lợi ích này đều đạt được nhờ cấu trúc mạch in 4 lớp.

Hướng dẫn toàn diện này từ kingfield — nhà sản xuất mạch in tại Thâm Quyến uy tín và là nhà cung cấp được chứng nhận UL, ISO9001, ISO13485 — sẽ hướng dẫn bạn từng bước cụ thể:

- Cấu tạo và chức năng của mạch in 4 lớp.

- Quy trình sản xuất mạch in 4 lớp chi tiết theo từng bước.

- Các khái niệm về sắp xếp lớp, quy trình ăn mòn và ép lớp trong mạch in nhiều lớp.

- Các phương pháp tốt nhất cho thiết kế (bố trí tín hiệu, nguồn và mặt đất, trở kháng điều khiển, quản lý lỗ via) và lắp ráp hậu kỳ.

- Các công nghệ liên quan đến khoan (CNC), mạ lỗ via và mạ điện, lựa chọn và đóng rắn lớp phủ chống hàn, cũng như các lớp hoàn thiện bề mặt như ENIG, OSP và HASL.

- Các tiêu chuẩn kiểm soát chất lượng và thử nghiệm chính như AOI và thử nghiệm mạch tích hợp (ICT).

- Cách phối hợp chuẩn bị vật liệu, dòng quy trình và tối ưu hóa cấu trúc lớp để đảm bảo chất lượng, hiệu quả chi phí và hiệu suất.

Mạch in 4 lớp là gì?

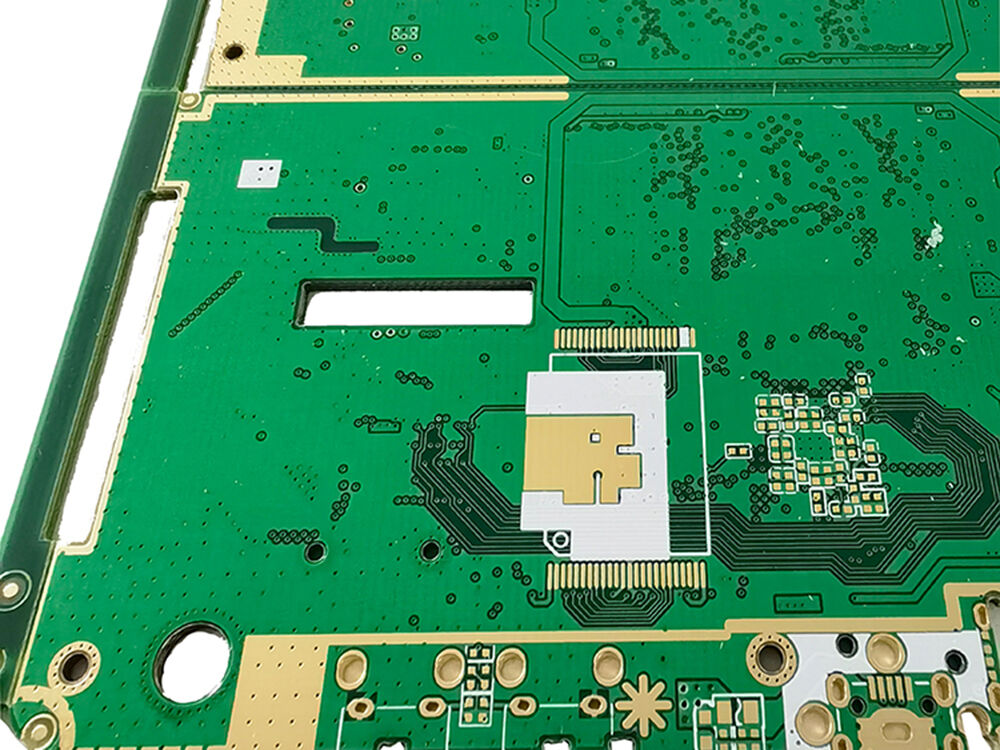

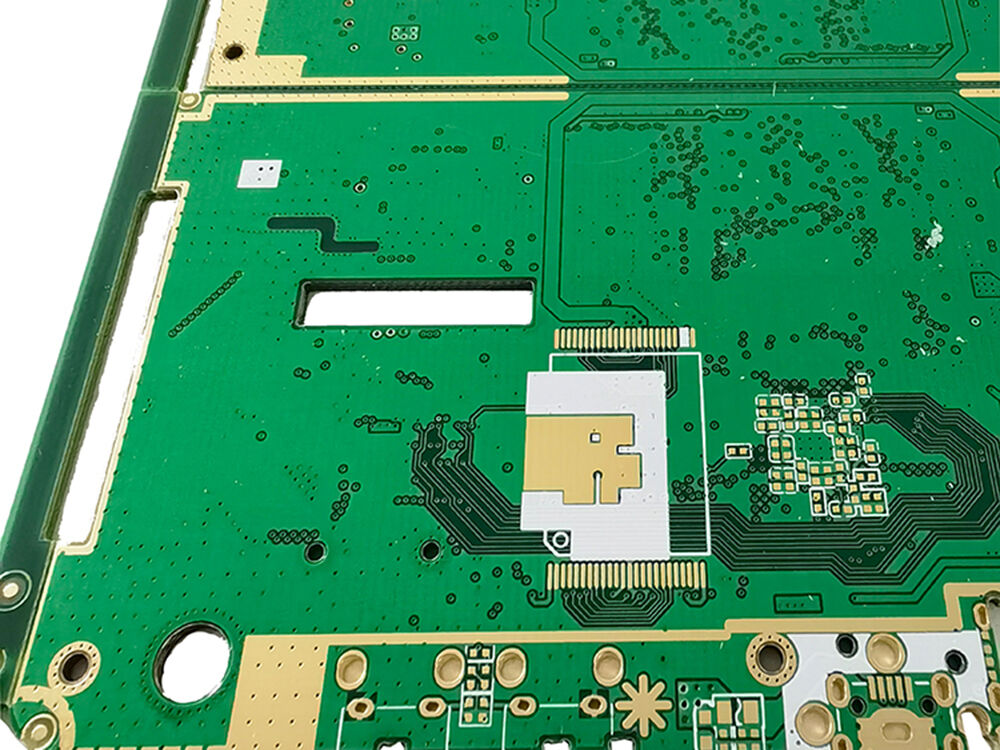

A pCB 4 lớp (mạch in có bốn lớp) là một loại mạch in nhiều lớp bao gồm bốn lớp dẫn điện bằng đồng được xếp chồng lên nhau, phân tách bởi các lớp vật liệu cách điện. Ý tưởng cốt lõi đằng sau cấu trúc mạch in 4 lớp là mang lại cho các nhà thiết kế sự linh hoạt và độ tin cậy cao hơn trong việc đi dây các mạch phức tạp, đạt được trở kháng điều khiển, quản lý phân phối nguồn và giảm thiểu nhiễu điện từ EMI so với các mạch in 2 lớp truyền thống.

Cấu tạo và Cấu trúc lớp điển hình

Một mạch in 4 lớp thông thường được chế tạo bằng cách ép nhiệt xen kẽ các lớp đồng và điện môi (còn được gọi là prepreg và lõi) để đạt được cấu trúc cứng, phẳng. Các lớp này thường đại diện cho các chức năng sau:

|

Lớp

|

Chức năng

|

|

Lớp trên (L1)

|

Dẫn tín hiệu, chân linh kiện (thông thường là SMT/THT)

|

|

Lớp trong 1 (L2)

|

Thường là mặt nối đất (GND) nhằm đảm bảo độ toàn vẹn tín hiệu và chống nhiễu EMI

|

|

Lớp trong 2 (L3)

|

Thông thường là mặt nguồn (VCC, 3.3V, 5V, v.v.)

|

|

Lớp dưới (L4)

|

Dẫn tín hiệu, linh kiện SMT hoặc đầu nối

|

Bố trí này (Tín hiệu | Nối đất | Nguồn | Tín hiệu) là tiêu chuẩn công nghiệp và mang lại một số lợi ích kỹ thuật:

- Tín hiệu ở bên ngoài giúp việc lắp ráp và xử lý sự cố dễ dàng hơn.

- Mặt nối đất đặc dưới các đường truyền tốc độ cao giúp giảm EMI và nhiễu xuyên âm.

- Mặt nguồn chuyên dụng đem lại khả năng cung cấp nguồn ổn định và tối ưu việc bỏ qua.

pCB 4 lớp so với các loại PCB khác

Hãy so sánh các thuộc tính chính giữa các cấu hình PCB điển hình:

|

Tính năng

|

pCB 2 lớp

|

pCB 4 lớp

|

pCB 6 lớp

|

|

Số lượng lớp đồng

|

2

|

4

|

6

|

|

Mật độ bố trí mạch

|

Thấp

|

Vừa phải/Cao

|

Rất cao

|

|

Độ nguyên vẹn của tín hiệu

|

LIMITED

|

Xuất sắc (nếu thiết kế tốt)

|

Đứng trên

|

|

Cung cấp nguồn điện

|

Cơ bản (không có mặt phẳng)

|

Mạnh (mặt phẳng chuyên dụng)

|

Xuất sắc (nhiều mặt phẳng)

|

|

Giảm EMI

|

Tối thiểu

|

Tốt

|

Tốt nhất

|

|

Độ dày PCB

|

0,8mm–2,4mm

|

1,2mm–2,5mm (thông thường)

|

1.6mm+

|

|

Phạm vi ứng dụng

|

Mật độ thấp, Đơn giản

|

Độ phức tạp trung bình-cao

|

Tần số cao, SI quan trọng

|

|

Chi phí

|

Thấp

|

Trung bình (≈2× 2 lớp)

|

Cao

|

Lợi thế chính của mạch in 4 lớp

1. Cải thiện tính toàn vẹn tín hiệu

Thiết kế mạch in 4 lớp mang lại trở kháng dây dẫn được kiểm soát chặt chẽ và đường hồi tín hiệu ngắn, có độ cảm ứng thấp—nhờ các mặt phẳng tham chiếu bên trong. Điều này đặc biệt quan trọng đối với các tín hiệu tốc độ cao hoặc tín hiệu RF, như trong USB 3.x, HDMI hoặc truyền thông không dây. Việc sử dụng mặt nối đất liên tục ngay dưới các lớp tín hiệu giúp giảm đáng kể nhiễu, crosstalk và nguy cơ méo tín hiệu.

2. Giảm EMI

EMI là một vấn đề lớn trong điện tử hiện đại. Cấu trúc xếp nhiều lớp—bao gồm các mặt nối đất và mặt nguồn đặt gần nhau—đóng vai trò như một lớp chắn tích hợp chống lại nhiễu bên ngoài và ngăn chặn bức xạ từ các mạch tốc độ cao trên bản mạch. Kỹ sư có thể điều chỉnh khoảng cách giữa các mặt (độ dày prepreg/lõi) để đạt kết quả EMC tốt nhất.

3. Phân phối Công suất Vượt trội

Các mặt phẳng nguồn và nối đất bên trong tạo thành một mạng phân phối điện (PDN) tự nhiên và cung cấp diện tích lớn cho các tụ phân tầng, giảm sụt áp và nhiễu nguồn. Chúng giúp cân bằng dòng tải nặng và ngăn ngừa các điểm nóng có thể làm hỏng các linh kiện nhạy cảm.

4. Mật độ Tuyến mạch Tăng cao

Với hai lớp đồng bổ sung, các kỹ sư thiết kế mạch có nhiều không gian hơn để đi tuyến tín hiệu—giảm sự phụ thuộc vào via, thu nhỏ kích thước mạch in và cho phép xử lý các thiết bị phức tạp hơn (như LSI, FPGA, CPU và bộ nhớ DDR).

5. Phù hợp với Thiết bị Nhỏ hơn

cấu trúc PCB 4 lớp rất lý tưởng cho các thiết bị nhỏ gọn hoặc di động, bao gồm cảm biến IoT, thiết bị y tế và các mô-đun ô tô, nơi bố trí mạch chặt chẽ là yếu tố then chốt đối với hình dáng sản phẩm.

6. Độ Bền Cơ học Tốt hơn

Độ cứng cơ học được cung cấp bởi quá trình ép nhiều lớp đảm bảo rằng mạch in có thể chịu được ứng suất lắp ráp, rung động và uốn cong trong môi trường khắc nghiệt.

Các kịch bản sử dụng PCB 4 lớp điển hình

- Bộ định tuyến, tự động hóa gia đình và các mô-đun RF (hiệu suất EMC và tín hiệu tốt hơn)

- Bộ điều khiển công nghiệp và ECU ô tô (khả năng chịu đựng và độ tin cậy)

- Thiết bị y tế (kích thước nhỏ gọn, tín hiệu nhạy cảm với nhiễu)

- Đồng hồ thông minh và thiết bị đeo (mật độ cao, yếu tố dạng nhỏ)

Các bước chính trong quy trình sản xuất PCB 4 lớp

Hiểu được quy trình sản xuất PCB 4 lớp từng bước rất quan trọng đối với bất kỳ ai tham gia vào thiết kế, mua sắm hoặc đảm bảo chất lượng PCB. Về cơ bản, việc sản xuất PCB 4 lớp là một quá trình đa giai đoạn đòi hỏi độ chính xác cao, biến đổi các tấm laminate phủ đồng thô, prepreg và tệp thiết kế điện tử thành một bo mạch in nhiều lớp chắc chắn, nhỏ gọn, sẵn sàng để lắp ráp.

Tổng quan: Các bước chính trong sản xuất PCB 4 lớp được thực hiện như thế nào?

Dưới đây là sơ đồ quy trình tổng thể cho sản xuất PCB 4 lớp, có thể làm kim chỉ nam cho cả người mới bắt đầu lẫn những chuyên gia lâu năm:

- Thiết kế PCB & Lập kế hoạch sắp xếp lớp

- Chuẩn bị vật liệu (Chọn Prepreg, Core, Lá đồng)

- Tạo ảnh & Ăn mòn lớp trong

- Căn chỉnh & Ép lớp

- Khoan (CNC) & Làm sạch ba via

- Mạ lỗ thông & Mạ điện

- Tạo hoa văn lớp ngoài (Quang trở, Ăn mòn)

- Phủ lớp cách điện & Xử lý đóng rắn

- Xử lý bề mặt (ENIG, OSP, HASL, v.v.)

- In lụa

- Gia công biên dạng PCB (Phay định hình, Cắt)

- Lắp ráp, Làm sạch và Kiểm tra (AOI/ICT)

- Kiểm soát Chất lượng Cuối cùng, Đóng gói và Giao hàng

Hướng dẫn từng bước dưới đây đi sâu vào từng khu vực, giải thích chi tiết về các phương pháp tốt nhất, thuật ngữ và các đặc điểm độc đáo của quy trình sản xuất mạch in 4 lớp .

Bước 1: Các Xem xét trong Thiết kế

Hành trình của một mạch in 4 lớp bắt đầu với đội kỹ thuật xác định các yêu cầu của mạch, sau đó được chuyển đổi thành các tệp thiết kế chi tiết—bao gồm định nghĩa cấu trúc lớp, bố trí các lớp và các đầu ra sản xuất.

Các Yếu tố Chính trong Thiết kế Mạch in 4 Lớp:

- Lựa chọn Cấu trúc Lớp: Các tùy chọn phổ biến như Tín hiệu | Nối đất | Nguồn | Tín hiệu hoặc Tín hiệu | Nguồn | Nối đất | Tín hiệu. Việc lựa chọn này ảnh hưởng trực tiếp đến hiệu suất điện và khả năng sản xuất.

-

Lựa chọn vật liệu:

- Lõi: Thông thường là FR-4, mặc dù các thiết kế cao tần, độ tin cậy cao có thể sử dụng vật liệu Rogers, lõi kim loại hoặc chất nền gốm.

- Prepreg: Nhựa gia cố sợi thủy tinh này rất quan trọng để cách điện và đảm bảo độ bền cơ học.

- Độ dày lớp đồng: 1 oz là tiêu chuẩn; 2 oz trở lên dành cho các mặt nguồn hoặc ứng dụng đặc biệt về nhiệt.

- Thiết kế Trở kháng Kiểm soát: Đối với các thiết kế truyền tín hiệu tốc độ cao hoặc tín hiệu vi sai (USB, HDMI, Ethernet), yêu cầu về trở kháng kiểm soát phải được xác định theo hướng dẫn IPC-2141A.

-

Công nghệ Via:

- Lỗ thông mạch xuyên tâm là tiêu chuẩn đối với hầu hết các mạch in bốn lớp.

- Via mù/via chôn, khoan ngược và đổ đầy keo là các tùy chọn tùy chỉnh dành cho mạch mật độ cao hoặc tần số cao; chúng có thể yêu cầu ép lớp tuần tự.

-

Công cụ Thiết kế Mạch in: Hầu hết các dự án PCB 4 lớp bắt đầu bằng các công cụ CAD chuyên nghiệp:

- Altium Designer

- KiCad

- Autodesk Eagle Các nền tảng này tạo ra các tệp Gerber và tệp khoan — những bản thiết kế kỹ thuật số tiêu chuẩn được gửi đến nhà sản xuất.

- Đánh giá Thiết kế cho Sản xuất (DFM): Các kiểm tra DFM được thực hiện để đảm bảo tất cả các thành phần đều có thể sản xuất được — xác minh khoảng cách dây dẫn/khe hở, tỷ lệ khía cạnh lỗ thông, chiều rộng vòng tròn kim loại xung quanh lỗ, lớp phủ hàn, lớp ký hiệu, và hơn thế nữa. Phản hồi DFM sớm giúp tránh phải thiết kế lại tốn kém hoặc chậm trễ trong sản xuất.

Bảng ví dụ: Các tùy chọn cấu trúc PCB 4 lớp điển hình

|

Tùy chọn cấu trúc lớp

|

Lớp 1

|

Lớp 2

|

Lớp 3

|

Lớp 4

|

Tốt nhất cho

|

|

Tiêu chuẩn (Phổ biến nhất)

|

Tín hiệu

|

Đất

|

Sức mạnh

|

Tín hiệu

|

Trở kháng điều khiển, nhạy cảm với EMI

|

|

Thay thế

|

Tín hiệu

|

Sức mạnh

|

Đất

|

Tín hiệu

|

Quản lý đường dẫn trả về

|

|

Tần số cao

|

Tín hiệu

|

Đất

|

Đất

|

Tín hiệu

|

Mạch GHz+, cách ly vượt trội

|

|

Phong tục

|

Tín hiệu

|

Tín hiệu/Nguồn

|

Đất

|

Tín hiệu

|

Mạch hỗn hợp, tùy chỉnh EMC tiên tiến

|

Bước tiếp theo

Giai đoạn tiếp theo trong quy trình sản xuất bảng mạch in 4 lớp đã Chuẩn bị vật liệu —bao gồm lựa chọn lõi, quản lý lớp prepreg và làm sạch tấm laminate.

Bước 2: Chuẩn bị vật liệu

Lựa chọn lõi và xử lý tấm laminate phủ đồng

Mọi bảng mạch in 4 lớp chất lượng cao đều bắt đầu với việc lựa chọn và chuẩn bị cẩn thận các vật liệu lõi. Một bảng mạch in bốn lớp điển hình sử dụng tấm laminate phủ đồng —các tấm cách điện được ép lớp hai mặt bằng lá đồng—làm khung 'xương sống' bên trong của bảng mạch in.

Các loại vật liệu bao gồm:

- FR-4 : Lõi phổ biến nhất hiện nay, mang lại tỷ lệ cân bằng giữa chi phí và hiệu suất cho hầu hết các ứng dụng.

- FR-4 nhiệt độ nóng chảy cao : Dùng cho các mạch yêu cầu khả năng chịu nhiệt lớn hơn.

- Rogers, Teflon và các tấm laminate tần số cao : Được chỉ định cho các mạch in RF và vi sóng nơi yêu cầu tổn thất thấp và tính chất điện môi ổn định là yếu tố then chốt.

- Lõi kim loại (Nhôm, Đồng) : Dành cho điện tử công suất hoặc các ứng dụng đòi hỏi tản nhiệt cao.

- Gốm và CEM : Được sử dụng trong các ứng dụng chuyên biệt, hiệu suất cao.

Thông tin: Phần lớn các mạch in nhiều lớp trong thiết bị điện tử tiêu dùng, y tế và công nghiệp sử dụng các lõi tiêu chuẩn FR-4 với trọng lượng đồng 1 oz làm điểm khởi đầu, nhằm tối ưu hóa chi phí, khả năng sản xuất và độ tin cậy về điện.

Cắt Tấm Lớp Ép theo Kích thước Bảng mạch

Các dây chuyền sản xuất mạch in xử lý các bảng mạch ở dạng lớn, sau đó được chia nhỏ thành từng mạch in riêng lẻ sau khi hoàn tất tạo hình mạch và lắp ráp. Việc cắt chính xác các tấm lớp ép phủ đồng và các tấm prepreg đảm bảo tính đồng đều, tối đa hóa tỷ lệ sử dụng vật liệu và phù hợp với phương pháp bố trí bảng mạch để đạt hiệu quả chi phí tốt nhất.

Việc Sử dụng Prepreg trong Cấu trúc Xếp Lớp

Prepreg (sợi composite tẩm trước) về cơ bản là một tấm vải thủy tinh được tẩm keo epoxy ở trạng thái bán đóng rắn. Trong quá trình ép nhiệt, các lớp prepreg được đặt xen kẽ giữa các lớp đồng và lõi, vừa đóng vai trò cách điện (cung cấp lớp cách ly cần thiết) vừa làm chất kết dính (nóng chảy và liên kết các lớp lại với nhau khi gia nhiệt).

Các điểm kỹ thuật chính:

- Tương thích Độ dày Cách điện: Độ dày lớp prepreg và lớp lõi được điều chỉnh để đạt độ dày bảng mục tiêu — ví dụ: 1,6 mm đối với cấu hình PCB 4 lớp tiêu chuẩn.

- Hằng số điện môi (Dk): Các ứng dụng hiện đại (đặc biệt là RF/mã hóa kỹ thuật số tốc độ cao) cần lớp prepreg được đặc trưng rõ ràng; giá trị Dk ảnh hưởng trực tiếp đến trở kháng của các đường dẫn.

- Khả năng chống ẩm: Lớp prepreg chất lượng cao làm giảm tối đa khả năng hấp thụ nước, điều này nếu không sẽ ảnh hưởng đến tính chất điện và độ tin cậy.

Làm sạch bề mặt đồng trước

Một bước quan trọng nhưng thường bị bỏ qua trong quá trình chế tạo PCB bốn lớp là việc làm sạch bề mặt đồng trên cả vật liệu lõi và lá đồng:

- Chải và ăn mòn vi mô: Vật liệu được xử lý chải cơ học, sau đó nhúng vào dung dịch axit loãng hoặc chất ăn mòn vi hóa học. Quy trình này loại bỏ các oxit bề mặt, nhựa và các hạt vi mô, làm lộ lớp đồng nguyên chất để thực hiện giai đoạn in hình tiếp theo.

- Làm khô: Bất kỳ độ ẩm còn sót lại nào cũng có thể làm yếu độ bám dính hoặc gây tách lớp, do đó các bảng mạch được sấy khô cẩn thận.

Truy xuất nguồn gốc và kiểm soát vật liệu

Tại thời điểm này, chuyên nghiệp Nhà sản xuất PCB gán số lô cho từng bảng mạch và từng lô vật liệu. Khả năng truy xuất là yếu tố thiết yếu để đáp ứng các tiêu chuẩn chất lượng (ISO9001, UL, ISO13485) và để truy vết sự cố trong trường hợp hiếm khi xảy ra vấn đề sau khi giao hàng.

Bảng: Các loại vật liệu và thông số kỹ thuật điển hình cho một bảng mạch PCB 4 lớp tiêu chuẩn

|

Vật liệu

|

Cách sử dụng

|

Thông số kỹ thuật điển hình

|

|

Lõi FR-4

|

Bề mặt

|

0,5 – 1,2 mm, Cu 1 oz

|

|

Tiền thụ thai

|

Đèn điện đệm

|

0,1 – 0,2 mm, Dk = 4,2 – 4,5

|

|

Tấm đồng

|

Chất dẫn

|

tiêu chuẩn 1 oz (35 µm); 2 oz đối với các lớp nguồn

|

|

Mặt nạ hàn

|

Bảo vệ

|

Màu xanh lá cây, dày 15–30 µm, loại LPI

|

|

Mực in lưới

|

Vạch

|

Màu trắng, độ nổi <0,02 mm

|

Chuẩn bị vật liệu đúng cách tạo thành nền tảng cho một mạch in 4 lớp đáng tin cậy. Tiếp theo, chúng ta chuyển sang giai đoạn kỹ thuật quan trọng: Tạo ảnh và ăn mòn lớp trong.

Bước 3: Tạo ảnh & Ăn mòn lớp trong

Mạch lớp trong của một mạch in 4 lớp—thường là các mặt phẳng nối đất và cấp nguồn, hoặc các lớp tín hiệu bổ sung trong cấu hình xếp chồng chuyên biệt—tạo thành xương sống điện học cho mọi việc định tuyến tín hiệu và phân phối điện năng. Đây là bước mà thiết kế mạch in kỹ thuật số của bạn được hiện thực hóa về mặt vật lý với độ chính xác dưới mức milimét trên lớp đồng thật sự.

1. Làm sạch: Chuẩn bị bề mặt

Trước khi tạo ảnh, các lõi đồng đã được làm sạch sơ bộ (chuẩn bị ở bước trước) sẽ trải qua quá trình tráng rửa cuối cùng và xử lý vi ăn mòn. Quá trình vi ăn mòn hóa học này loại bỏ mọi vết oxy hóa còn sót lại, tăng độ nhám bề mặt ở cấp độ vi mô và đảm bảo độ bám dính tối ưu cho lớp keo cảm quang. Bất kỳ tạp chất nào còn sót lại—ngay cả những hạt rất nhỏ—cũng có thể gây ra hiện tượng ăn mòn không đủ, đứt mạch/chập mạch, hoặc độ phân giải in kém.

2. Ứng dụng chất cảm quang

Các lõi phủ đồng đã được làm sạch sau đó được phủ bằng keo ảnh —một lớp phim polymer nhạy sáng cho phép xác định mạch chính xác. Việc phủ thường được thực hiện thông qua quá trình ép màng khô , trong đó chất cảm quang bám chặt vào bề mặt đồng dưới các con lăn nóng.

-

Loại:

- Chất cảm quang âm là tiêu chuẩn công nghiệp đối với các bảng mạch nhiều lớp; các vùng bị chiếu sáng sẽ liên kết chéo và vẫn còn lại sau quá trình phát triển.

- Chất cảm quang dạng lỏng có thể được sử dụng trong một số quy trình để kiểm soát chính xác hơn, mặc dù màng khô vẫn phổ biến hơn trong phần lớn sản xuất bảng mạch in 4 lớp.

3. Chiếu sáng (Ghi hình UV / Tạo khuôn ảnh)

Tiếp theo, lõi đã chuẩn bị đi qua một máy chụp ảnh UV tự động , nơi một tia laser độ phân giải cao hoặc mặt nạ quang học được tạo từ CAD sẽ căn chỉnh các họa tiết mạch lên tấm panel có lớp đồng phủ. Ánh sáng tử ngoại chiếu qua các phần trong suốt của mặt nạ:

- Tại những vị trí mặt nạ trong suốt : Lớp keo cảm quang bị phơi sáng và trở nên trùng hợp (cứng lại).

- Tại những vị trí mặt nạ không trong suốt : Lớp keo cảm quang vẫn mềm và chưa được phơi sáng.

4. Phát triển (Rửa lớp keo chưa phơi sáng)

Tấm panel được phát triển—ngâm trong dung dịch nước nhẹ (chất phát triển). Lớp keo cảm quang chưa phơi sáng, mềm, bị rửa trôi, làm lộ lớp đồng bên dưới. Chỉ còn lại họa tiết mạch (lớp keo đã cứng do được phơi sáng) tồn tại, chính xác khớp với thiết kế cung cấp trong các tập tin Gerber.

5. Ăn mòn (Loại bỏ đồng)

Bây giờ PCB trải qua quá trình ăn mòn lớp bên trong —một quá trình ăn mòn bằng axit được kiểm soát, thường sử dụng dung dịch amoniacal hoặc ferric chloride:

- Ăn mòn loại bỏ đồng không mong muốn khỏi những khu vực không được bảo vệ bởi lớp keo ảnh đã hóa cứng.

- Các vạch mạch, miếng hàn, mặt phẳng và các chi tiết đồng được thiết kế khác vẫn được giữ lại.

6. Tẩy keo ảnh

Sau khi các mẫu đồng theo yêu cầu đã hiện rõ, lớp keo ảnh đã hóa cứng bảo vệ các khu vực này sẽ được tẩy sạch bằng một dung dịch hóa chất riêng biệt. Các vạch đồng sáng bóng, trần trụi còn lại chính xác khớp với bản vẽ thiết kế của lớp bên trong.

Kiểm soát chất lượng: Kiểm tra quang học tự động (AOI)

Mỗi lớp bên trong đều được kiểm tra nghiêm ngặt để phát hiện lỗi bằng cách sử dụng Kiểm tra quang học tự động (AOI) . Các camera độ phân giải cao quét để phát hiện:

- Mạch hở (các đường mạch bị đứt)

- Các chi tiết bị ăn mòn quá mức hoặc không đủ

- Nối tắt giữa các đường mạch hoặc các pad

- Lỗi căn chỉnh hoặc đăng ký lớp

Tại sao quá trình ăn mòn lớp trong lại quan trọng đối với PCB 4 lớp

- Độ Nguyên Vẹn Của Tín Hiệu: Các mặt lớp trong được ăn mòn sạch và tốt sẽ đảm bảo mặt phẳng tham chiếu ổn định cho các mạng tốc độ cao, ngăn ngừa nhiễu và EMI.

- Phân phối năng lượng: Các mặt nguồn rộng giúp giảm thiểu sụt áp và tiêu tán công suất.

- Liên tục mặt phẳng: Duy trì các mặt phẳng rộng và liền mạch tuân thủ IPC-2221/2222 và giảm độ lệch trở kháng.

độ chính xác ở giai đoạn này quyết định hiệu suất của bảng mạch. Một lỗi nối tắt hoặc hở mạch đơn lẻ trong lớp nguồn hoặc lớp tiếp đất nội bộ sẽ dẫn đến hỏng hoàn toàn sau khi ép lớp—không thể sửa chữa. Đó là lý do tại sao các nhà sản xuất PCB hàng đầu luôn ưu tiên kiểm soát quá trình tạo ảnh và kiểm tra AOI trực tuyến. — kINGFIELD

Bước 4: Căn chỉnh và Ép lớp

Thích hợp căn chỉnh và ép lớp là yếu tố thiết yếu trong sản xuất PCB 4 lớp. Quy trình này liên kết vật lý các lớp đồng đã được in hình trước đó (giờ chứa các mạch và mặt phẳng bên trong) với các tấm prepreg và các lá đồng ngoài—tạo thành cấu trúc bốn lớp hoàn chỉnh.

A. Chuẩn bị chồng lớp: Sắp xếp cấu hình

Dây chuyền sản xuất hiện tại lắp ráp cấu trúc bên trong, sử dụng:

- Lõi lớp trong: Các lõi trong đã hoàn thiện (được ăn mòn, làm sạch)—thường là các lớp mặt phẳng tiếp đất và nguồn.

- Prepreg: Các lớp điện môi (cách điện) được đo đạc cẩn thận, đặt giữa các lõi đồng và các lá đồng ngoài.

- Các lá đồng ngoài: Các tấm sẽ trở thành các lớp định tuyến trên cùng và dưới cùng sau khi in mạch.

B. Ghim và Định vị (Căn chỉnh lớp)

Việc căn chỉnh không chỉ là yêu cầu cơ khí—mà còn rất quan trọng để:

- Duy trì sự đăng ký giữa pad và via, để các lỗ khoan sau này sẽ không bị lệch, cắt xén hoặc nối tắt sang các thành phần liền kề.

- Giữ các mặt phẳng tham chiếu ngay bên dưới các tuyến tín hiệu quan trọng nhằm duy trì tính toàn vẹn tín hiệu và trở kháng điều khiển được.

Cách thức đạt được sự căn chỉnh:

- Ghim: Các chốt thép chính xác và lỗ định vị được đục xuyên qua chồng tấm để giữ tất cả các tấm ở vị trí căn chỉnh tuyệt đối trong suốt quá trình lắp ráp.

- Định vị quang học: Các nhà máy sản xuất PCB tiên tiến sử dụng hệ thống quang học tự động để kiểm tra và cải thiện độ chính xác căn chỉnh giữa các lớp, thường đạt dung sai ±25 μm (micron).

C. Lớp hóa: Kết hợp bằng nhiệt và áp suất

Lớp xếp chồng và đã được cố định sau đó được đưa vào một nén nóng máy ép lớp:

- Giai đoạn chân không: Loại bỏ không khí bị mắc kẹt và các chất dễ bay hơi, ngăn ngừa hiện tượng tách lớp hoặc xuất hiện khoảng rỗng.

- Nhiệt và áp suất: Vật liệu tiền ngâm (prepreg) mềm ra và chảy dưới nhiệt độ 170–200°C (338–392°F) và áp suất 1,5–2 MPa.

- Đóng rắn: Nhựa mềm ra sẽ lấp đầy các khoảng rỗng vi mô và kết dính các lớp lại với nhau, sau đó đông cứng (trùng hợp) khi nguội đi.

Kết quả là một tấm đơn cứng chắc, được liên kết chặt chẽ —với bốn lớp đồng riêng biệt, cách điện hoàn toàn, được ép lớp chính xác và sẵn sàng cho các bước xử lý tiếp theo.

Kiểm soát Chất lượng: Kiểm tra và Thử nghiệm sau khi Ép lớp

Sau khi ép lớp, tấm mạch được làm nguội và làm sạch. Các bước kiểm tra chất lượng thiết yếu bao gồm:

- Đo độ Dày và Độ Vênh: Đảm bảo mạch phẳng và đáp ứng dung sai đã quy định (thông thường là ±0,1 mm).

-

Phân tích Mặt cắt Hủy phá: Các mẫu mạch được cắt nhỏ và phân tích dưới kính hiển vi để xác minh:

- Cách điện giữa các lớp (không có hiện tượng tách lớp, bọt khí hay thiếu nhựa).

- Độ chính xác căn chỉnh lớp (độ trùng khít giữa các lớp).

- Chất lượng liên kết tại các bề mặt nối giữa lớp prepreg và lớp lõi.

- Kiểm tra trực quan: Kiểm tra hiện tượng tách lớp, biến dạng và nhiễm bẩn bề mặt.

Tiêu chuẩn và Thực hành Tốt nhất của IPC

- IPC-6012: Quy định các yêu cầu về hiệu suất và kiểm tra đối với mạch in cứng, bao gồm độ căn chỉnh nhiều lớp và chất lượng ép lớp.

- IPC-2221/2222: Khuyến nghị sử dụng các mặt phẳng liên tục, khe hở tối thiểu và dung sai định vị nghiêm ngặt để đảm bảo hiệu suất ổn định.

- Nguyên liệu: Sử dụng vật liệu bán thành phẩm, lõi và đồng đạt tiêu chuẩn công nghiệp—ưu tiên loại có số lô truy xuất được để kiểm soát chất lượng và báo cáo quy định.

Bảng Tóm tắt: Lợi ích của quá trình ép lớp chính xác trong mạch in 4 lớp

|

Lợi ích

|

Chi tiết

|

|

Tính Toàn Vẹn Tín Hiệu Xuất Sắc

|

Duy trì mối quan hệ đúng giữa mặt đất/mặt tín hiệu

|

|

Kết nối đáng tin cậy

|

Đảm bảo các lỗ khoan xuyên qua sẽ chạm tới tất cả các pad/mặt phẳng cần thiết

|

|

Độ bền cơ học

|

Chịu được các ứng suất nhiệt và cơ trong quá trình lắp ráp và sử dụng

|

|

Giảm em

|

Tối thiểu lệch lớp, ngăn ngừa các điểm nóng EMI

|

|

Hiệu suất sản xuất

|

Ít lỗi hơn, giảm phế phẩm, hiệu quả chi phí tốt hơn

|

Bước 5: Khoan và Mạ

The giai đoạn khoan và mạ của quy trình chế tạo mạch in bốn lớp là nơi kết nối vật lý và điện của bảng mạch thực sự được hình thành. Việc tạo lỗ via chính xác và lớp mạ đồng chắc chắn là yếu tố thiết yếu để truyền tín hiệu và nguồn ổn định trong cấu trúc nhiều lớp.

A. Khoan CNC các lỗ Via và Lỗ Linh kiện

Các dây chuyền sản xuất mạch in 4 lớp hiện đại sử dụng máy khoan điều khiển bằng máy tính (CNC) để tạo ra hàng trăm hoặc thậm chí hàng ngàn lỗ trên mỗi tấm—đảm bảo độ chính xác, tốc độ và khả năng lặp lại cao, vốn rất quan trọng đối với các ứng dụng tiên tiến.

Các loại lỗ trên PCB 4 lớp:

- Lỗ vias xuyên suốt: Kéo dài từ lớp trên cùng đến lớp dưới cùng, kết nối mọi mặt phẳng đồng và các lớp. Những lỗ này tạo thành xương sống cho cả kết nối tín hiệu và nối đất.

- Lỗ linh kiện: Các pad dành cho linh kiện cắm xuyên lỗ (THT), đầu nối và chân cắm.

-

Không bắt buộc:

- Lỗ vias mù: Kết nối một lớp ngoài với một lớp bên trong (nhưng không phải cả hai); ít phổ biến trên mạch 4 lớp do chi phí cao.

- Lỗ vias chôn: Chỉ kết nối giữa các lớp bên trong; được sử dụng trong các dự án mật độ cao hoặc PCB lai cứng-mềm.

Các điểm nổi bật của quá trình khoan:

- Xếp chồng tấm: Nhiều tấm có thể được khoan đồng thời để tối ưu hóa năng suất, mỗi tấm được hỗ trợ bởi một tấm nền phenolic ở lối vào/lối ra nhằm ngăn ngừa hiện tượng vênh hay lệch mũi khoan.

- Lựa chọn mũi khoan: Mũi khoan bằng carbide hoặc phủ kim cương với kích thước từ 0,2 mm (8 mils) trở lên. Mức độ mài mòn mũi khoan được theo dõi sát sao và thay thế định kỳ nghiêm ngặt để đảm bảo độ chính xác cao.

- Dung sai vị trí lỗ khoan: Thông thường là ±50 µm, điều này rất quan trọng để căn chỉnh đúng vị trí pad via trong các thiết kế mật độ cao.

B. Làm sạch ba via và loại bỏ vết cháy

Sau khi hoàn thành quá trình khoan, xử lý cơ học sẽ để lại các cạnh thô ráp (ba via) và lớp tráng epoxy 'dính bẩn' trên thành via, đặc biệt tại những vị trí sợi thủy tinh và nhựa bị lộ ra. Nếu không được xử lý, những hiện tượng này có thể gây tắc mạ hoặc dẫn đến các vấn đề về độ tin cậy.

- Loại bỏ ba via: Các bàn chải cơ học loại bỏ các cạnh sắc và vụn foil.

- Loại bỏ vết cháy: Các tấm được xử lý hóa học (sử dụng kali permanganat, plasma hoặc các phương pháp không dùng permanganat) để loại bỏ các dư lượng nhựa và hoàn toàn lộ ra sợi thủy tinh và đồng nhằm tạo điều kiện liên kết kim loại ở bước tiếp theo.

C. Tạo lỗ thông và mạ đồng điện phân

Có thể nói đây là bước quan trọng nhất— mạ lỗ thông —tạo nên các kênh dẫn điện quan trọng giữa các lớp của mạch in 4 lớp.

Quy trình bao gồm:

- Làm sạch thành lỗ: Các tấm trải qua quá trình tiền xử lý (làm sạch bằng axit, ăn mòn vi mô) để đảm bảo bề mặt hoàn toàn sạch sẽ.

- Phủ đồng không điện phân: Một lớp đồng mỏng (~0,3–0,5 µm) được phủ hóa học lên thành lỗ, 'gieo hạt' cho lỗ thông để thực hiện thêm bước mạ điện ở sau.

- Mạ điện: Các tấm PCB được đặt vào bồn đồng. Dòng điện một chiều (DC) được áp dụng; các ion đồng bám phủ lên tất cả các bề mặt kim loại để hở — bao gồm thành lỗ via và lỗ xuyên — tạo thành ống đồng dẫn điện đồng đều trong mỗi lỗ.

- Độ dày đồng tiêu chuẩn: Thành lỗ via hoàn thiện thường được mạ tối thiểu 20–25 µm (0,8–1 mil), phù hợp với tiêu chuẩn IPC-6012 Class 2/3 hoặc theo yêu cầu của khách hàng.

- Kiểm tra độ đồng đều: Sử dụng hệ thống giám sát độ dày và cắt mẫu kiểm tra để đảm bảo không có điểm mỏng hay khoảng trống, có thể gây ra mạch hở hoặc lỗi gián đoạn khi vận hành thực tế.

Kiểm soát chất lượng:

- Phân tích cắt ngang: Các lỗ được chọn mẫu sẽ được cắt và đo đạc về độ dày thành, độ bám dính và độ đồng đều.

- Kiểm tra liên tục: Các kiểm tra điện đảm bảo rằng mọi lỗ via đều tạo được kết nối chắc chắn từ pad này sang pad khác, từ lớp này sang lớp khác.

D. Tại sao Khoan và Mạ quan trọng đối với PCB 4 lớp

- Độ tin cậy cao: Mạ đồng đều, không khuyết tật qua lỗ via ngăn ngừa lỗi hở mạch/ngắn mạch và sự cố nghiêm trọng ngoài thực tế. - Tính toàn vẹn tín hiệu: Tạo hình lỗ via đúng cách hỗ trợ chuyển tiếp tín hiệu nhanh, đường nối đất có điện trở thấp và cung cấp nguồn đáng tin cậy. - Hỗ trợ thiết kế tiên tiến: Cho phép kích thước chi tiết nhỏ hơn, đóng gói mật độ cao và tương thích với các công nghệ như HDI hoặc mạch in lai cứng-uốn (rigid-flex PCB).

Bảng: Thông số khoan và mạ cho mạch in 4 lớp tiêu chuẩn

|

Thông số kỹ thuật

|

Giá trị điển hình

|

Ghi chú

|

|

Kích thước lỗ hoàn thiện tối thiểu

|

0,25–0,30 mm (10–12 mil)

|

Nhỏ hơn đối với quy trình HDI/tiên tiến

|

|

Độ dày lớp đồng thành lỗ

|

≥ 20 µm (0.8 mil, IPC-6012)

|

Lên đến 25–30 µm trong các thông số kỹ thuật độ tin cậy cao

|

|

Tỷ lệ khía Via

|

Lên đến 8:1 (độ dày bảng : lỗ)

|

Các tỷ lệ cao hơn đòi hỏi thiết kế thân thiện với sản xuất (DFM) cẩn thận

|

|

Độ đồng đều mạ

|

±10% trên toàn bộ tấm

|

Theo dõi bằng phiếu kiểm tra/tia X

|

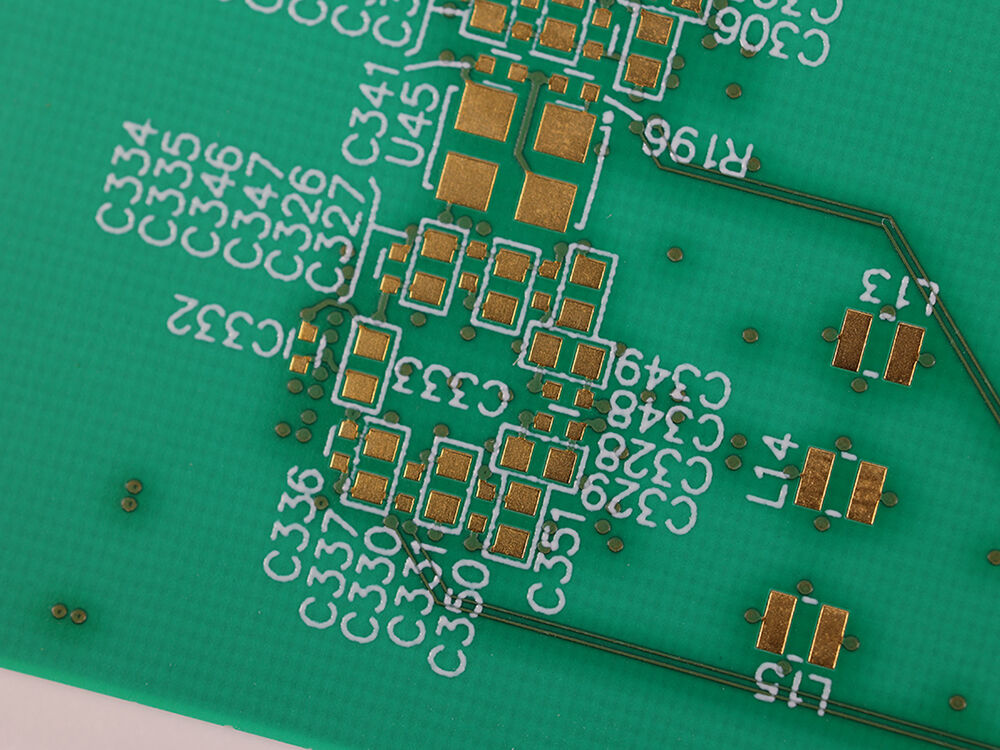

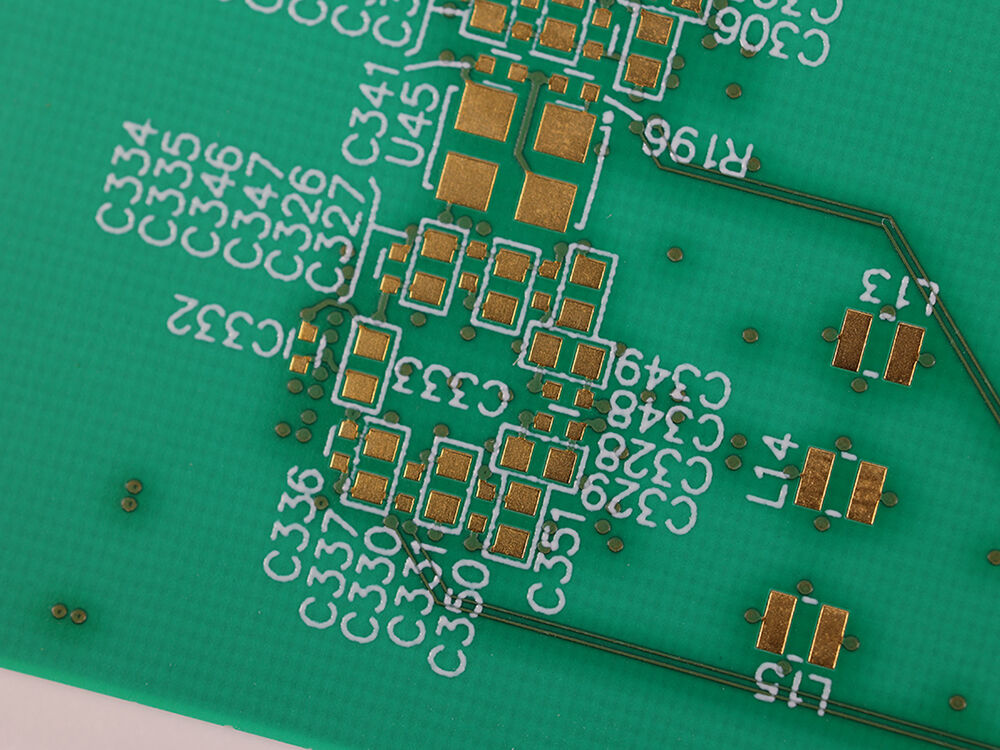

Bước 6: Tạo mẫu lớp ngoài (Tạo mạch trên các lớp 1 & 4)

The các lớp ngoài các lớp ngoài của bảng mạch in 4 lớp—Lớp 1 (trên) và Lớp 4 (dưới)—chứa các miếng hàn, đường dẫn và các chi tiết bằng đồng sẽ tương tác trực tiếp với các linh kiện hoặc đầu nối trong quá trình lắp ráp. Giai đoạn này về cơ bản tương tự như xử lý lớp bên trong, nhưng mức độ nghiêm ngặt cao hơn: các lớp này phải trải qua quá trình hàn, làm sạch và chịu mài mòn đáng kể, đồng thời phải đáp ứng các tiêu chuẩn khắt khe nhất về mặt thẩm mỹ và kích thước.

A. Phủ lớp quang khắc cho lớp ngoài

Giống như các lớp bên trong, các lớp đồng ngoài trước tiên được làm sạch và ăn mòn vi mô để tạo bề mặt hoàn hảo. Sau đó, một lớp keo ảnh (thường là màng khô) được ép phủ lên toàn bộ bề mặt bằng con lăn gia nhiệt nhằm đảm bảo độ bám dính.

- Thông tin: Các nhà sản xuất bảng mạch in chất lượng cao kiểm soát cẩn thận cả độ dày màng lẫn áp lực ép phủ, nhằm đảm bảo quá trình phát triển hình ảnh đồng đều và giảm thiểu biến dạng ở các cạnh.

B. Tạo ảnh (Dụng cụ chụp ảnh/Ghi ảnh trực tiếp bằng tia UV laser)

- Dụng cụ chụp ảnh: Đối với hầu hết các lô sản xuất hàng loạt, các mặt nạ quang học chứa các mẫu đường dẫn và miếng đệm bằng đồng cho cả hai lớp trên và dưới sẽ được căn chỉnh quang học với các lỗ khoan.

- Hình ảnh Trực tiếp bằng Tia laser (LDI): Trong các dự án độ chính xác cao hoặc nhanh chóng, một tia laser điều khiển bằng máy tính sẽ 'ghi' các đường dẫn và miếng đệm được định nghĩa bởi Gerber trực tiếp lên tấm với độ chính xác ở mức micron.

- Tia cực tím (UV) làm đông cứng lớp keo ảnh đã qua xử lý, cố định chính xác mạch ngoài vào vị trí.

C. Phát triển và Ăn mòn

- Phát triển: Lớp keo ảnh chưa được phơi sáng sẽ bị rửa trôi bằng chất phát triển kiềm nhẹ, lộ ra phần đồng để tiến hành ăn mòn.

- Ăn mòn bằng axit: Phần đồng đã qua xử lý phơi sáng sẽ bị loại bỏ bởi các thiết bị ăn mòn băng tải tốc độ cao, chỉ giữ lại các đường dẫn, miếng đệm và mạch được bảo vệ bởi lớp keo ảnh đã hóa cứng.

- Loại bỏ: Lớp keo ảnh còn sót lại sẽ được tẩy sạch, lộ ra các cấu trúc đồng bên ngoài mới, sáng bóng tạo thành các bề mặt hàn được và các đường dẫn truyền dòng điện cho bo mạch của bạn.

Bảng: Các kích thước chính cho việc tạo mẫu lớp ngoài PCB 4 lớp

|

Tính năng

|

Giá trị tiêu chuẩn

|

Ghi chú

|

|

Chiều rộng dấu vết

|

0,15–0,25 mm (6–10 mil)

|

Đối với hầu hết các thiết kế số, nguồn và hỗn hợp tín hiệu

|

|

Không gian

|

0,15–0,20 mm (6–8 mil)

|

Được kiểm soát theo IPC Class 2/3

|

|

Vòng tròn

|

≥0,1 mm (4 mil)

|

Phụ thuộc DFM, đảm bảo mối hàn đáng tin cậy

|

|

Dung sai từ pad đến pad

|

±0,05 mm (2 mil)

|

Đối với LSI/SMT mật độ cao

|

D. Kiểm tra và kiểm soát chất lượng

Các tấm mới được ăn mòn được kiểm tra bằng mắt thường và thông qua AOI (Kiểm tra Quang học Tự động) dành cho:

- Các đường mạch và pad bị ăn mòn quá mức hoặc không đủ

- Các cầu nối hoặc nối tắt

- Các mối hở hoặc thành phần bị thiếu

- Đăng ký/căn chỉnh với các lỗ khoan sẵn

Tại Sao Việc Tạo Mẫu Lớp Ngoài Lại Quan Trọng Đối Với PCB 4 Lớp

- Độ tin cậy trong lắp ráp: Khả năng hàn, kích thước pad và độ bền của đường mạch đều được xác định tại đây.

- Độ Nguyên Vẹn Của Tín Hiệu: Các tín hiệu tốc độ cao, cặp vi sai và các mạng trở kháng điều khiển kết thúc tại các lớp này, do đó việc xác định chính xác các đường mạch là rất quan trọng.

- Khả năng Xử lý Công suất: Đủ đồng được giữ lại để đáp ứng mọi nhu cầu đi dây và tản nhiệt.

Bước 7: Lớp phủ chống hàn, hoàn thiện bề mặt và in ký hiệu

Sau khi hoàn tất tạo mẫu đồng cho các lớp ngoài của PCB 4 lớp, đã đến lúc tăng cường độ bền, khả năng hàn và tính rõ ràng cho cả quá trình lắp ráp lẫn bảo trì sau này. Bước gồm nhiều phần này làm nổi bật quy trình sản xuất PCB nhiều lớp chuyên nghiệp bằng cách bảo vệ mạch, đảm bảo quá trình hàn đáng tin cậy và giúp nhận diện trực quan dễ dàng.

A. Ứng dụng lớp phủ chống hàn

The mặt nạ hàn là một lớp phủ polymer bảo vệ—thường có màu xanh lục, mặc dù các màu xanh dương, đỏ, đen và trắng cũng phổ biến—được phủ lên cả hai mặt trên và dưới của mạch in (PCB):

-

Mục đích:

- Ngăn ngừa hiện tượng cầu hàn giữa các pad và đường mạch được bố trí gần nhau.

- Bảo vệ mạch bên ngoài khỏi hiện tượng oxy hóa, tác động hóa học và mài mòn cơ học.

- Cải thiện khả năng cách điện giữa các đường mạch, từ đó tăng cường độ ổn định tín hiệu và giảm nhiễu điện từ (EMI).

Quy trình sử dụng:

- Lớp phủ: Tấm mạch được phủ lớp sơn chống hàn dạng lỏng có thể tạo ảnh bằng ánh sáng (LPI), bao phủ toàn bộ trừ các pad đồng sẽ được hàn về sau.

- Tạo ảnh và Phơi sáng: Ánh sáng UV được sử dụng cùng với mặt nạ họa tiết để xác định các vùng mở (cho pad, điểm kiểm tra, via).

- Phát triển: Lớp phủ chống hàn không bị chiếu sáng sẽ bị rửa trôi, trong khi phần đã được chiếu sáng sẽ đóng rắn, bảo vệ các mạch điện.

- Giai đoạn Đông Kết: Các tấm mạch được nướng hoặc đóng rắn bằng UV để làm cứng hoàn toàn lớp phủ.

B. Tùy chọn hoàn thiện bề mặt

Để đảm bảo tất cả các pad tiếp xúc có thể chịu được quá trình lưu trữ, chống oxy hóa và có khả năng hàn hoàn hảo trong quá trình lắp ráp, một hoàn thiện bề mặt được phủ lên. Có một số loại lớp hoàn thiện phù hợp với ứng dụng, chi phí và yêu cầu lắp ráp:

|

Hoàn thiện bề mặt

|

Viết tắt

|

Những lợi thế chính

|

Các trường hợp sử dụng điển hình

|

|

Mạ Nickel không điện tử - Mạ vàng chìm

|

ENIG

|

Bề mặt phẳng, chống oxy hóa, phù hợp cho chân khoảng cách nhỏ/BGA; khả năng hàn tuyệt vời, đáp ứng tiêu chuẩn RoHS

|

Ứng dụng độ tin cậy cao, HDI, thiết bị tiêu dùng, RF

|

|

Chất bảo vệ khả năng hàn hữu cơ

|

OSP

|

Sạch, không chì, tiết kiệm chi phí; bảo vệ lớp đồng trần và dễ dàng hàn hồi lưu

|

Thị trường đại chúng, SMT đơn giản

|

|

Thiếc ngâm

|

—

|

Phẳng, phù hợp cho các đầu nối lắp ép hoặc tốc độ cao

|

Tầng kiểm soát trở kháng, bảng lắp ép

|

|

Ngâm Bạc

|

—

|

Lý tưởng cho tần số cao/tính toàn vẹn tín hiệu

|

RF, kỹ thuật số tốc độ cao

|

|

San lấp bằng khí nóng (HASL) không chì

|

HASL

|

Được sử dụng rộng rãi, hiệu quả về chi phí, độ bền cao; lớp phủ thiêu kết bằng thiếc nóng chảy

|

Điện tử thông dụng, hỗn hợp THT/SMT

|

- ENIG là tiêu chuẩn công nghiệp cho hầu hết các bảng mạch mẫu và sản xuất 4 lớp, đặc biệt khi độ phẳng bề mặt và mật độ cao (BGA, LGA, QFN) là yếu tố quan trọng.

- OSP phù hợp nhất cho các thiết bị điện tử không chì cần hiệu quả chi phí và chất lượng mối hàn tốt.

Sự khác biệt giữa ENIG và HASL:

- ENIG cung cấp bề mặt mịn và phẳng hơn, cần thiết cho các bước siêu nhỏ và BGAs.

- HASL tạo ra các 'vòm' không đều có thể không phù hợp với việc lắp ráp PCB mật độ cao hiện đại.

- ENIG đắt hơn nhưng mang lại khả năng lưu trữ lâu dài tốt hơn và tương thích với nối dây (wire-bonding).

C. In silkscreen

Với lớp phủ hàn và lớp hoàn thiện bề mặt đã được đặt vào vị trí, lớp cuối cùng là in lưới —dùng để đánh dấu:

- Các đường viền và nhãn linh kiện (R1, C4, U2)

- Các ký hiệu cực tính

- Ký hiệu tham chiếu

- Chỉ báo chân 1, logo, mã phiên bản và mã vạch

Kiểm soát chất lượng: Kiểm tra AOI cuối cùng và kiểm tra trực quan

- Kiểm tra Quang học Tự động (AOI): Đảm bảo kích thước/vị trí mở của lớp phủ hàn, không có lớp phủ hàn rò rỉ và vùng tiếp xúc pad được lộ chính xác.

- Kiểm tra trực quan: Xác nhận độ rõ nét của lớp in ký hiệu, không bị thiếu mực in, lớp phủ hàn không che các chi tiết chính và kiểm tra tính toàn vẹn của lớp hoàn thiện bề mặt.

Tại Sao Giai Đoạn Này Quan Trọng Đối Với PCB 4 Lớp

- Khả Năng Hàn: Chỉ những pad/điểm tiếp xúc được để lộ mới cho phép hàn; việc che phủ phần còn lại ngăn ngừa hiện tượng nối tắt—điều cực kỳ quan trọng trong các thiết kế mật độ cao.

- Khả Năng Chống Ăn Mòn & Nhiễm Bẩn: Tuổi thọ và độ tin cậy của mạch được cải thiện đáng kể nhờ bảo vệ các bề mặt đồng khỏi không khí, độ ẩm và dấu vân tay.

- Giảm lỗi: Các ký hiệu rõ ràng và chính xác giúp giảm sai sót trong lắp ráp, giảm nhu cầu sửa chữa hoặc thời gian bảo trì tại hiện trường.

Bước 8: Tạo Hình PCB, Lắp Ráp Và Vệ Sinh

Với tất cả các lớp mạch đã được thiết lập, các lỗ thông mạch đã được mạ, và lớp phủ hàn cùng lớp hoàn thiện bề mặt đã được phủ lên, giờ đây tập trung chuyển sang giai đoạn tạo hình dạng, gắn linh kiện và làm sạch pCB 4 lớp . Giai đoạn này biến tấm mạch nhiều lớp của bạn từ một khối được gia công chính xác nhưng chưa phân biệt thành một thiết bị chức năng hoàn chỉnh, phù hợp với dạng hình học cụ thể.

A. Tạo hình PCB (Cắt và định tuyến)

Tại giai đoạn này, nhiều bản vẽ PCB nằm trên một tấm sản xuất lớn hơn. Cắt định hình có nghĩa là tách riêng từng bảng mạch in bốn lớp theo đường viền yêu cầu, bao gồm các lỗ khoét, khe hoặc rãnh V.

Các phương pháp chính:

- Phay CNC : Các mũi cắt cacbua tốc độ cao đi theo cạnh ngoài của bảng mạch một cách chính xác, đáp ứng các dung sai chặt chẽ tới ±0,1 mm.

- Rãnh chữ V : Các rãnh nông cho phép dễ dàng tách bảng mạch bằng cách bẻ dọc theo các đường rãnh.

- Đấm : Được sử dụng cho các bảng mạch có hình dạng tiêu chuẩn, sản lượng lớn để tối ưu hóa năng suất.

B. Lắp ráp PCB (Đặt linh kiện SMT & THT)

Hầu hết các bảng mạch in 4 lớp ngày nay sử dụng lắp ráp công nghệ hỗn hợp, tận dụng cả hai Công nghệ gắn bề mặt (SMT) để dán linh kiện mật độ cao, tự động hóa, và Công nghệ khoan lỗ (THT) để kết nối có độ bền cao, bộ phận nguồn hoặc linh kiện cũ.

1. Lắp ráp SMT

- In khuôn : Hỗn hợp hàn được in lên các miếng đồng tiếp xúc thông qua khuôn cắt laser để đảm bảo độ chính xác về khối lượng.

- Gắp và Đặt : Các máy tự động đặt hàng chục ngàn linh kiện mỗi giờ với độ chính xác ở mức micron—ngay cả với linh kiện cỡ nhỏ 0201, QFN, BGA hoặc thiết bị LSI.

- Hàn bằng nhiệt đối lưu : Các bảng mạch đã lắp đi qua lò sấy khí cưỡng bức có chế độ nhiệt được lập trình cẩn thận, lần lượt làm nóng chảy và làm nguội mối hàn. Quá trình này tạo ra các mối hàn chắc chắn cho mọi linh kiện SMT.

2. Lắp ráp THT

- Chèn thủ công hoặc tự động : Các linh kiện có chân dài, như đầu nối hoặc tụ điện phân lớn, được luồn qua các lỗ mạ.

- Hàn sóng : Các bảng mạch đi qua sóng hàn nóng chảy để hàn đồng thời tất cả các chân đã luồn—một phương pháp đã được kiểm chứng theo thời gian nhằm đảm bảo độ bền cơ học cao.

SMT so với THT:

- SMT cho phép các cụm linh kiện có mật độ cao, nhẹ và nhỏ gọn. Phù hợp nhất cho các mạch in nhiều lớp hiện đại.

- Tht vẫn được ưu tiên sử dụng cho các đầu nối và các bộ phận công suất cao cần thêm điểm cố định.

C. Làm sạch (Rượu isopropyl và các chất tẩy rửa mạch in chuyên dụng)

Sau khi hàn, các dư thừa như keo trợ hàn, giọt hàn và bụi có thể làm giảm độ tin cậy, đặc biệt là trên các đường dẫn và lỗ khoan cách nhau gần nhau của các mạch in bốn lớp.

Các bước quy trình:

- Làm sạch bằng Rượu Isopropyl (IPA) : Thường dùng trong chế tạo mẫu và sản xuất số lượng thấp, loại bỏ thủ công các dư thừa ion và keo trợ hàn nhìn thấy được.

- Máy rửa mạch in liên tục : Các máy rửa công nghiệp sử dụng nước khử ion, chất xà phòng hóa hoặc dung môi chuyên dụng để làm sạch nhiều mạch cùng lúc — điều này rất quan trọng trong các ngành y tế, quân sự và ô tô.

Tại sao việc làm sạch lại quan trọng:

- Ngăn ngừa ăn mòn và sự phát triển của các tinh thể dendritic giữa các thành phần mạch.

- Giảm nguy cơ các đường rò rỉ điện, đặc biệt đối với các mạch có trở kháng cao hoặc điện áp cao.

Bảng: Tổng quan quy trình lắp ráp và làm sạch

|

Sân khấu

|

Kỹ thuật

|

Ưu điểm

|

Ứng Dụng Điển Hình

|

|

Cắt định hình

|

Cắt CNC, V-Scoring

|

Cạnh chính xác, không ứng suất

|

Tất cả các loại bảng mạch

|

|

Lắp ráp smt

|

Khửn/Hàn chảy

|

Mật độ cao, tốc độ nhanh, độ chính xác cao

|

Sản phẩm đại trà, mật độ cao

|

|

Lắp ráp THT

|

Hàn sóng

|

Các mối nối chắc chắn, chịu được các linh kiện cồng kềnh

|

Công suất, đầu nối

|

|

Vệ sinh

|

IPA hoặc Bộ rửa nối tiếp (In-line Washer)

|

Loại bỏ cặn bẩn, đảm bảo độ tin cậy

|

Tất cả, đặc biệt là các bộ phận quan trọng

|

Bước 9: Kiểm tra cuối cùng, Kiểm soát Chất lượng (QC) và Đóng gói

A pCB 4 lớp chỉ tốt ngang bằng với mức độ nghiêm ngặt của quá trình kiểm tra và kiểm soát chất lượng. Ngay cả khi sản phẩm trông hoàn hảo bằng mắt thường, những khuyết tật vô hình — như chập, hở, lệch vị trí hoặc lớp mạ không đủ — có thể gây ra hoạt động bất thường, hỏng hóc sớm hoặc rủi ro về an toàn. Vì vậy, các nhà sản xuất bảng mạch in (PCB) hàng đầu sử dụng một loạt quy trình kiểm tra toàn diện bao gồm kiểm tra điện, kiểm tra trực quan và tài liệu dựa trên các tiêu chuẩn IPC được công nhận quốc tế.

A. Kiểm tra Quang học Tự động (AOI)

Kiểm tra quang học tự động (AOI) được thực hiện nhiều lần trong suốt quá trình sản xuất PCB nhiều lớp, với lần kiểm tra quan trọng nhất là sau khi hoàn thành lắp ráp và hàn.

- Cách làm việc: Các camera độ phân giải cao quét cả hai mặt của mỗi bảng mạch PCB, so sánh từng đường mạch, điểm hàn và mối nối với các tệp Gerber kỹ thuật số.

-

Những gì AOI phát hiện:

- Mở (các mạch bị đứt)

- Ngắn mạch (cầu hàn)

- Thiếu hoặc lệch linh kiện

- Các mối hàn có lượng thiếc thiếu hoặc thừa

- Hiện tượng Tombstoning hoặc lệch linh kiện

B. Kiểm tra trong mạch (ICT)

Kiểm tra nội mạch (ICT) là tiêu chuẩn vàng để xác minh chức năng của mạch in 4 lớp đã được lắp ráp:

- Đầu dò tiếp xúc: Bộ kiểm tra dạng giường đinh hoặc đầu dò bay tiếp xúc với các điểm kiểm tra chuyên dụng hoặc chân linh kiện.

- Kịch bản kiểm tra: Truyền tín hiệu qua mạch và đo phản hồi tại các điểm nút chính.

-

Các thông số được kiểm tra:

- Tính liên tục giữa tất cả các điểm tín hiệu và điện

- Điện trở/điện dung của các mạch chính

- Độ bền của các lỗ khoan kim loại và lỗ thông lớp

- Sự hiện diện/vắng mặt và hướng lắp đặt của các linh kiện chính

ICT cho phép:

- Chẩn đoán ngay lập tức ở cấp độ bo mạch (xác định chính xác các mối hàn lỗi, đứt mạch hoặc linh kiện lắp sai vị trí)

- Thống kê theo lô để giám sát quá trình sản xuất

C. Kiểm tra điện

Mỗi bản mạch in bốn lớp hoàn thiện được thực hiện đầy đủ kiểm tra liên tục điện tử “ngắn mạch và hở mạch”. Trong bước này:

- Kiểm Tra Điện (ET): Điện áp cao được áp dụng lên tất cả các đường mạch và kết nối liên kết.

- Mục tiêu: Phát hiện bất kỳ lỗi “hở mạch” (ngắt kết nối) hoặc “ngắn mạch” (nối cầu không mong muốn) nào, bất kể hình thức bên ngoài.

Đối với thiết kế điều khiển trở kháng:

- Mẫu Kiểm Tra Trở Kháng: Các đường mạch thử nghiệm được chế tạo cùng cấu trúc lớp và quy trình như các mạch sản xuất, cho phép đo lường và xác minh trở kháng đặc trưng (ví dụ: 50 Ω đơn, 90 Ω vi sai).

D. Tài liệu và khả năng truy xuất nguồn gốc

- Tệp Gerber, Tệp Khoan và Tệp Kiểm Tra: Nhà sản xuất tổng hợp và lưu trữ tất cả các dữ liệu quan trọng, đảm bảo khả năng truy xuất nguồn gốc từ lô vật liệu đến thành phẩm bảng mạch.

- Bản vẽ lắp ráp và Chứng chỉ kiểm tra chất lượng: Đi kèm các lô hàng độ tin cậy cao để tuân thủ các tiêu chuẩn ISO9001/ISO13485, y tế hoặc ô tô.

- Mã vạch: Số sê-ri và mã vạch được in trên từng bảng mạch hoặc tấm panel để theo dõi, xử lý sự cố và tham chiếu 'bản sao kỹ thuật số'.

E. Kiểm tra hình thức cuối cùng và Đóng gói

Các kiểm tra viên được đào tạo thực hiện kiểm tra cuối cùng bằng kính phóng đại và đèn chiếu cường độ cao để xem xét các chi tiết quan trọng:

- Độ sạch của pad và via (không có bi hàn hay dư thừa)

- Độ rõ nét của ký hiệu, nhãn, hướng đặt và độ chính xác của mã phiên bản

- Chất lượng cạnh và tạo hình (không bị bong lớp, vỡ mẻ hoặc hư hỏng)

Bao bì:

- Túi chống tĩnh điện được hút chân không bảo vệ khỏi ESD và sự xâm nhập của độ ẩm

- Xốp bong bóng, mút xốp hoặc khay tùy chỉnh ngăn ngừa va chạm vật lý trong quá trình vận chuyển

- Mỗi lô được đóng gói theo hướng dẫn của khách hàng, bao gồm gói hút ẩm hoặc chỉ thị độ ẩm cho các thị trường yêu cầu độ tin cậy cao

Bảng: Tiêu chuẩn Kiểm tra và Kiểm soát Chất lượng cho PCB 4 lớp

|

Kiểm tra/Kiểm định

|

Tiêu chuẩn/Tài liệu tham chiếu

|

Điều nó đảm bảo

|

|

AOI

|

IPC-610, ISO9001

|

Sản phẩm hoàn thiện không có khuyết tật nhìn thấy được

|

|

Kiểm tra Điện (ET)

|

IPC-9252

|

Không có nối tắt/hở mạch

|

|

ICT/Chỉ điểm bay

|

Tùy chỉnh/IPC-2222

|

Kiểm tra chức năng, theo chân cụ thể

|

|

Kiểm tra Trở kháng

|

IPC-2141A, phiếu kiểm

|

Tuân thủ đường truyền

|

|

Kiểm tra trực quan

|

IPC-A-610, ISO13485

|

Chất lượng thẩm mỹ và cơ học

|

Cách Tạo Bố Trí 4 Lớp trong Altium Designer

Kiểm soát bố trí PCB 4 lớp là yếu tố then chốt để đạt được sự cân bằng phù hợp giữa hiệu suất điện, khả năng sản xuất và chi phí. Các công cụ thiết kế PCB hiện đại như Altium Designer cung cấp giao diện trực quan và mạnh mẽ để xác định—và sau đó xuất—mọi chi tiết mà nhà sản xuất cần nhằm chế tạo các mạch in nhiều lớp chất lượng cao và đáng tin cậy.

Từng Bước: Xác Định Bố Trí PCB 4 Lớp Của Bạn

1. Bắt Đầu Dự Án Của Bạn Trong Altium

- Mở Altium Designer và tạo một dự án PCB mới.

- Nhập hoặc vẽ sơ đồ mạch của bạn, đảm bảo rằng tất cả các linh kiện, mạng nối và ràng buộc đã được xác định.

2. Truy cập Trình quản lý Lớp xếp tầng

- Đi đến Thiết kế → Trình quản lý Lớp xếp tầng.

- Trình quản lý Lớp xếp tầng cho phép bạn cấu hình tất cả các lớp dẫn điện và cách điện, độ dày và vật liệu.

3. Thêm Bốn Lớp Đồng

- Theo mặc định, bạn sẽ thấy Lớp Trên và Lớp Dưới.

- Thêm hai lớp bên trong (thường được đặt tên là MidLayer1 và MidLayer2) cho cấu trúc bốn lớp của bạn.

4. Xác định Chức năng Lớp

Gán các mục đích thông dụng cho mỗi lớp như sau:

|

Lớp

|

Chức năng điển hình

|

Ví dụ về Stack

|

|

ĐẦU TRANG

|

Tín hiệu + Linh kiện

|

L1 (Tín hiệu)

|

|

MidLayer1

|

Mặt đất

|

L2 (Mass)

|

|

MidLayer2

|

Mặt phẳng nguồn (VCC v.v.)

|

L3 (Nguồn)

|

|

Đáy

|

Tín hiệu / Linh kiện

|

L4 (Tín hiệu)

|

5. Cấu hình Độ dày Điện môi/Prepreg và Lõi

- Nhấp giữa các lớp để thiết lập độ dày điện môi (prepreg, lõi) bằng cách sử dụng các giá trị do nhà sản xuất quy định .

- Độ dày tổng điển hình cho mạch in 4 lớp: 1,6mm (nhưng có thể mỏng hơn/dày hơn tùy nhu cầu).

- Nhập giá trị hằng số điện môi (Dk) và hệ số tổn hao, đặc biệt đối với các thiết kế yêu cầu trở kháng kiểm soát.

6. Gán Trọng lượng Đồng

- Chỉ định độ dày đồng cho từng lớp: thường là 1 oz/ft² (~35 μm) là tiêu chuẩn cho các lớp tín hiệu; 2 OZ hoặc nhiều hơn cho nguồn dòng cao.

- Các giá trị này ảnh hưởng đến tính toán chiều rộng đường dẫn và độ bền cơ học.

7. Bật Tính toán Trở kháng

- Sử dụng chức năng Máy tính Trở kháng (hoặc liên kết đến công cụ của nhà sản xuất bạn) để tính toán trở kháng đơn và cặp vi sai dựa trên vật liệu, độ dày và các thông số chiều rộng/khoảng cách của bạn.

- Các mục tiêu điển hình: 50Ω đơn , 90–100Ω vi sai .

- Điều chỉnh độ dày điện môi, chiều rộng đường dẫn và trọng lượng đồng theo nhu cầu để đạt được các mục tiêu này.

8. Tạo Bản vẽ Cấu trúc Lớp

- Xuất một bản vẽ stackup (DXF, PDF, v.v.) cho ghi chú sản xuất của bạn. Điều này giúp ngăn ngừa lỗi giao tiếp và đẩy nhanh quá trình kiểm tra DFM.

9. Chuẩn bị và Xuất tệp Gerber và tệp Drill

- Thiết lập xác nhận stackup cuối cùng cho đường viền bảng, thứ tự lớp và chú thích của bạn.

- Xuất tất cả Tệp Gerber, tệp Drill và sơ đồ stackup với tên gọi chính xác (bao gồm tên lớp khớp với trình quản lý stackup của bạn).

Nghiên cứu điển hình: Tối ưu hóa cấu trúc PCB 4 lớp cho tín hiệu tốc độ cao

Tình huống: Một công ty khởi nghiệp viễn thông đã thiết kế một bộ định tuyến mới sử dụng Altium Designer. Thách thức chính của họ là giảm nhiễu crosstalk giữa các tín hiệu và duy trì các tín hiệu USB/Ethernet trong dung sai trở kháng chặt chẽ.

Giải pháp:

- Sử dụng Trình quản lý Stackup lớp của Altium để tạo [Tín hiệu | Nối đất | Nguồn | Tín hiệu] với lớp prepreg 0,2mm giữa các mặt ngoài và trong.

- Thiết lập trọng lượng đồng là 1 OZ cho tất cả các lớp.

- Sử dụng công cụ tính trở kháng của Altium và phối hợp vật liệu với nhà sản xuất, nhanh chóng lặp lại cho đến khi kết quả đo đạt được mục tiêu 50Ω và 90Ω trong phạm vi ±5% .

- Kết quả: Lô đầu tiên vượt qua kiểm tra tương thích điện từ trường (EMC) và độ toàn vẹn tín hiệu tốc độ cao—rút ngắn thời gian chứng nhận và tiết kiệm thời gian phát triển.

Tại sao Thiết kế Stackup trong Altium Quan trọng đối với PCB 4 Lớp

- Ngăn ngừa thiết kế lại tốn kém: Lập kế hoạch cấu trúc lớp sớm cùng với sự góp ý từ nhà sản xuất sẽ ngăn ngừa chậm trễ và đảm bảo quá trình chuyển tiếp suôn sẻ từ mẫu thử sang sản xuất.

- Hỗ trợ kiểm tra DFM: Các cấu trúc lớp được tài liệu hóa kỹ lưỡng giúp phát hiện các sai lệch giữa DRC/DFM trước khi sản xuất bảng mạch.

- Hỗ trợ các tính năng nâng cao: Việc kiểm soát chính xác cấu trúc lớp là cần thiết đối với các công nghệ như via-in-pad, via chìm/chìm ngầm và dẫn tuyến trở kháng điều khiển.

Thực hành tốt nhất cho cấu trúc lớp và bố trí PCB 4 lớp

Bộ xử lý mạnh mẽ bố trí PCB 4 lớp chỉ là một nửa của phương trình—hiệu suất thực sự, độ tin cậy và tỷ lệ thành phẩm cao đến từ việc áp dụng các thực hành tốt đã được định hình trong bố trí và thiết kế. Khi bạn tối ưu hóa cấu trúc lớp, dẫn tuyến, tách ghép và các đường dẫn nhiệt một cách cẩn trọng, quy trình sản xuất PCB bốn lớp của bạn sẽ tạo ra các bảng mạch vượt trội về độ toàn vẹn tín hiệu, EMC, khả năng sản xuất và độ bền vòng đời.

1. Các yếu tố cần cân nhắc về độ toàn vẹn tín hiệu và nguồn

Đường dẫn trả tín hiệu được kiểm soát và phân phối nguồn sạch là nền tảng trong thiết kế PCB nhiều lớp. Dưới đây là cách để thực hiện đúng:

- Đặt các tín hiệu trên các lớp ngoài (L1, L4) và dành các lớp trong (L2, L3) làm mặt phẳng nối đất (GND) và nguồn (VCC) đặc.

- Bao giờ không chia nhỏ các mặt phẳng bên trong bằng các khoét lớn hoặc khe hở—thay vào đó, hãy giữ cho các mặt phẳng liên tục. Theo IPC-2221/2222 , sự gián đoạn có thể khiến trở kháng điều khiển sai lệch từ 5–15%, điều này có thể dẫn đến suy giảm tín hiệu hoặc lỗi ngắt quãng.

- Các đường hồi tiếp tín hiệu ngắn: Các tín hiệu tốc độ cao và nhạy cảm với nhiễu luôn phải 'nhìn thấy' một mặt phẳng tham chiếu đặc ngay bên dưới. Điều này giúp giảm diện tích vòng lặp và ức chế EMI phát xạ.

Bảng: Cách sử dụng thông thường của cấu trúc PCB 4 lớp

|

Tùy chọn

|

L1

|

L2

|

L3

|

L4

|

Tốt nhất cho

|

|

Tiêu chuẩn

|

Tín hiệu

|

Đất

|

Sức mạnh

|

Tín hiệu

|

Tổng quát, trở kháng điều khiển, EMC

|

|

Thay thế

|

Tín hiệu

|

Sức mạnh

|

Đất

|

Tín hiệu

|

Liên kết nguồn – đất được cải thiện

|

|

Phong tục

|

Tín hiệu/Nguồn

|

Đất

|

Đất

|

Tín hiệu/Nguồn

|

RF, GHz, kỹ thuật số siêu sạch

|

2. Bố trí Linh kiện và Tụ Đỡ

- Nhóm các IC tốc độ cao gần các đầu nối hoặc nguồn/tải để giảm thiểu chiều dài dây dẫn và số lượng lỗ via.

- Đặt các tụ đỡ càng gần càng tốt (ưu tiên đặt trực tiếp trên các lỗ via nối với mặt phẳng nguồn) để đảm bảo điện áp VCC ổn định cục bộ.

- Ưu tiên các mạng quan trọng: Đi dây các mạng tần số cao, mạng xung nhịp và mạng tương tự nhạy trước các tín hiệu ít quan trọng hơn.

Thực hành tốt nhất: Sử dụng kỹ thuật "fanout": dẫn tín hiệu ra khỏi các BGA và các gói linh kiện khoảng cách nhỏ bằng các đoạn dây ngắn và lỗ via trực tiếp — giảm thiểu nhiễu xuyên âm và hiệu ứng cụt dây.

3. Đi dây cho Trở kháng Điều khiển

- Chiều rộng và khoảng cách dây dẫn: Tính toán và thiết lập trong quy tắc thiết kế cho cặp tín hiệu đơn 50Ω và cặp vi sai 90–100Ω bằng cách sử dụng các thiết lập cấu trúc lớp phù hợp (độ dày điện môi, Dk, trọng lượng đồng).

- Giảm thiểu chiều dài cụt: Tránh chuyển tiếp không cần thiết giữa các lớp, và sử dụng khoan ngược (back-drilling) cho các tín hiệu quan trọng để loại bỏ phần thông qua không sử dụng.

- Chuyển đổi lớp: Đặt các cặp vi sai trên cùng một lớp bất cứ khi nào có thể, và tránh việc đi chéo lớp không cần thiết.

4. Chiến lược Via và Via khâu nối (Stitching)

- Sử dụng via khâu nối trên các mặt đất đặc —bao quanh các tín hiệu tốc độ cao, mạng xung nhịp và vùng RF bằng các via nối đất được đặt gần nhau (thường là mỗi 1–2 cm).

- Tối ưu hóa kích thước via và tỷ lệ chiều sâu/lỗ: IPC-6012 khuyến nghị tỷ lệ chiều sâu trên đường kính lỗ hoàn thiện (độ dày bảng so với kích thước lỗ hoàn chỉnh) nói chung không nên vượt quá 8:1 để đảm bảo độ tin cậy cao.

- Lỗ thông mạch khoan ngược: Đối với tốc độ cực cao, hãy sử dụng kỹ thuật khoan ngược để loại bỏ phần dư của lỗ thông mạch và giảm thêm hiện tượng phản xạ tín hiệu.

5. Quản lý nhiệt và cân bằng đồng

- Lỗ thông nhiệt: Đặt các mảng lỗ thông nhiệt dưới các IC/LDO tỏa nhiều nhiệt để kết nối và tản nhiệt xuống mặt phẳng tiếp đất.

- Đổ đồng: Sử dụng phân bố đồng cân bằng trên cả hai lớp ngoài để ngăn cong vênh/xoắn ở các bảng mạch lớn hơn hoặc công suất cao.

- Khu vực đồng được kiểm soát: Tránh các 'đảo' đồng không nối lớn có thể gây ghép điện áp hoặc EMI.

6. Chống nhiễu điện từ (EMI) và ngăn crosstalk

- Định tuyến các hướng tín hiệu vuông góc: Định tuyến các tín hiệu trên L1 và L4 theo góc vuông (ví dụ: L1 chạy theo hướng đông-tây, L4 chạy theo hướng bắc-nam) — điều này giảm ghép điện dung và nhiễu xuyên âm qua các mặt phẳng.

- Giữ các tín hiệu tốc độ cao tránh xa mép bảng mạch , và tránh đi song song với mép, vì điều này có thể phát xạ nhiều EMI hơn.

7. Xác minh bằng Mô phỏng và Phản hồi từ Nhà sản xuất

- Thực hiện mô phỏng tính toàn vẹn tín hiệu trước và sau khi bố trí đối với các mạng hoặc giao diện quan trọng.

- Xem xét lại cấu trúc lớp và các ràng buộc định tuyến với nhà sản xuất PCB 4 lớp đã chọn —sử dụng kinh nghiệm của họ để ngăn ngừa sớm các rủi ro về khả năng sản xuất và độ tin cậy trong quá trình thiết kế.

Trích dẫn từ Ross Feng: tại Viasion, chúng tôi nhận thấy rằng việc tuân thủ các phương pháp tốt nhất một cách kỷ luật ở cấp độ thiết kế — các mặt phẳng vững chắc, sử dụng đường dẫn (via) hợp lý, mối quan hệ cẩn trọng giữa dây nối và mặt phẳng — sẽ tạo ra các mạch in 4 lớp đáng tin cậy hơn, giảm nhiễu điện từ (EMI) và rút ngắn chu kỳ gỡ lỗi cho khách hàng của chúng tôi.

Bảng tóm tắt: Những điều Nên và Không nên trong bố trí mạch in 4 lớp

|

Những điều Nên

|

Những điều Không nên

|

|

Sử dụng các mặt phẳng nối đất và nguồn liên tục

|

Chia nhỏ các mặt phẳng bên trong; tránh các khe hở

|

|

Đặt tụ lọc gần các đường dẫn nguồn

|

Dẫn tín hiệu tốc độ cao mà không có mặt phẳng tham chiếu

|

|

Tính toán và đảm bảo trở kháng kiểm soát

|

Bỏ qua các giá trị cấu trúc lớp do nhà sản xuất cung cấp

|

|

Tối ưu thông qua tỷ lệ khung hình và khoảng cách

|

Lạm dụng các đoạn nối ngắn/mặt cắt ngang không cần thiết

|

|

Sử dụng cân bằng đồng để giảm biến dạng

|

Để lại các vùng đồng lớn không được kết nối

|

Các yếu tố ảnh hưởng đến chi phí PCB 4 lớp

Kiểm soát chi phí là mối quan tâm hàng đầu của mọi quản lý kỹ thuật, nhà thiết kế và chuyên viên mua sắm khi làm việc với pCB 4 lớp . Việc hiểu rõ các biến số ảnh hưởng đến giá thành sản xuất mạch nhiều lớp giúp đưa ra quyết định thông minh, tiết kiệm chi phí—mà không làm giảm chất lượng tín hiệu, độ tin cậy hay tính năng sản phẩm.

1. Lựa chọn vật liệu

-

Loại lõi và lớp cách điện (prepreg):

- FR-4 tiêu chuẩn: Tiết kiệm chi phí nhất, phù hợp với đa số ứng dụng thương mại và công nghiệp.

- Vật liệu có chỉ số TG cao, tổn hao thấp hoặc vật liệu RF: Rogers, Teflon và các chất nền đặc biệt khác là yếu tố thiết yếu đối với các thiết kế tần số cao, độ tin cậy cao hoặc yêu cầu quản lý nhiệt nghiêm ngặt, nhưng có thể làm tăng chi phí chất nền lên 2–4 lần.

-

Độ dày lớp đồng:

- 1 oz (35µm) là tiêu chuẩn; nâng cấp lên 2 oz hoặc hơn cho các mặt phẳng nguồn hoặc quản lý nhiệt sẽ làm tăng cả chi phí vật liệu và xử lý.

-

Độ nhẵn bề mặt:

- ENIG (Mạ Nickel không điện hóa và phủ vàng chìm): Chi phí cao hơn, nhưng cần thiết cho các ứng dụng khoảng cách nhỏ, độ tin cậy cao hoặc nối dây gắn kết.

- OSP, HASL, Bạc chìm/Thiếc chìm: Tiết kiệm chi phí hơn, nhưng có thể đánh đổi về thời hạn bảo quản hoặc độ phẳng.

2. Độ dày và kích thước bảng mạch

- Độ dày tiêu chuẩn (1,6mm) là lựa chọn tiết kiệm nhất, tối ưu hóa việc sử dụng tấm mạch và giảm thiểu các bước quy trình đặc biệt.

- Độ dày tùy chỉnh, rất mỏng (<1,0 mm) hoặc dày (>2,5 mm) các tấm yêu cầu xử lý đặc biệt và có thể làm giới hạn lựa chọn nhà sản xuất.

Bảng: Các độ dày tấm mẫu và ứng dụng điển hình

|

Độ dày

|

Ứng dụng

|

Tác động đến chi phí

|

|

1.0 mm

|

Thiết bị đeo, thiết bị di động mật độ cao

|

Trung lập

|

|

1,6 mm

|

Mục đích chung, tiêu chuẩn công nghiệp

|

Thấp nhất

|

|

2,0+ mm

|

Nguồn điện, đầu nối, chịu lực cơ học

|

cao hơn 10-20%

|

3. Thiết kế phức tạp

- Chiều rộng vạch/dãy khoảng cách: ≤4 mils làm tăng chi phí do tỷ lệ loại bỏ cao hơn và năng suất chậm hơn.

- Kích thước Via tối thiểu: Microvia, via chìm/nổi hoặc via trong miếng hàn làm tăng đáng kể nỗ lực sản xuất.

- Số lượng lớp: Mạch in bốn lớp là 'lõi' của mạch nhiều lớp phổ biến trên thị trường; việc thêm nhiều lớp hơn (6, 8, 12, v.v.) hoặc cấu trúc xếp lớp không tiêu chuẩn sẽ làm tăng giá thành tương ứng.

4. Phân bố bảng mạch và hiệu suất sử dụng

- Bảng mạch lớn (nhiều bảng trên một tấm) tối đa hóa năng suất và hiệu quả vật liệu, giúp giảm chi phí mỗi bảng.

- Bảng mạch có hình dạng bất thường hoặc kích thước lớn (yêu cầu lãng phí nhiều hơn hoặc cần dụng cụ chuyên dụng) làm giảm mật độ bảng và hiệu quả về chi phí.

5. Yêu cầu xử lý đặc biệt

- Trở kháng điều khiển: Yêu cầu kiểm soát chặt chẽ hơn về chiều rộng đường dẫn, khoảng cách và độ dày lớp điện môi—có thể cần thêm các bước kiểm tra chất lượng/kiểm thử.

- Các tiếp điểm vàng, rãnh, xẻ rãnh, mạ viền: Mọi quy trình cơ học hoặc hoàn thiện không tiêu chuẩn nào cũng làm tăng chi phí NRE (chi phí kỹ thuật không định kỳ) và chi phí trên từng linh kiện.

- Ép lớp tuần tự, khoan ngược: Thiết yếu cho các lỗ via chìm/nổi hoặc thiết kế tốc độ cao, nhưng làm tăng thêm các bước, thời gian và độ phức tạp.

6. Khối lượng và Thời gian giao hàng

- Giai đoạn thử nghiệm và sản xuất số lượng nhỏ: Thông thường từ 10–50 USD/bảng mạch, tùy thuộc vào tính năng, do chi phí thiết lập được phân bổ trên ít đơn vị hơn.

- Số lượng trung bình đến lớn: Chi phí trên mỗi đơn vị giảm mạnh—đặc biệt nếu thiết kế của bạn được tối ưu hóa theo tấm mạch và sử dụng thông số kỹ thuật phổ thông.

- Giao hàng nhanh Giao hàng nhanh (nhanh nhất từ 24–48 giờ) sẽ phát sinh thêm phí cao hơn—hãy lên kế hoạch trước nếu có thể.

7. Chứng nhận và Đảm bảo Chất lượng

- UL, ISO9001, ISO13485, Tuân thủ môi trường: Cơ sở được chứng nhận và tài liệu đầy đủ sẽ tốn chi phí cao hơn nhưng là bắt buộc đối với các dự án ô tô, y tế và thương mại đòi hỏi độ chính xác cao.

Bảng so sánh chi phí: Báo giá ví dụ cho mạch in 4 lớp

|

Tính năng

|

FR-4 cơ bản, OSP

|

ENIG, High-TG, Kiểm soát trở kháng

|

|

1,6mm, 1 oz, lỗ tối thiểu 0,3mm, hoàn thiện tiêu chuẩn

|

15–25 USD mỗi bảng (số lượng 10)

|

30–60 USD mỗi bảng (số lượng 10)

|

|

2,0mm, 2 oz, ENIG, 4 mil/4 mil, kiểm soát trở kháng

|

$30–$45 mỗi bảng (số lượng 10)

|

$45–$70 mỗi bảng (số lượng 10)

|

|

Linh kiện lai cứng-mềm (cùng kích thước)

|

$60–$100+

|

Không phổ biến

|

Cách Tận Dụng Tối Đa Giá Trị từ Sản Xuất PCB 4 Lớp

- Cung cấp đầy đủ bản vẽ cấu trúc lớp và bản vẽ cơ khí ngay từ đầu

- Phản hồi nhanh chóng với phản hồi DFM, chỉnh sửa để phù hợp với khả năng sản xuất

- Chọn các nhà cung cấp đã được chứng nhận tại Thâm Quyến hoặc toàn cầu

- Tối ưu hóa thiết kế mảng/bảng để sản xuất số lượng lớn

- Hợp tác với các nhà cung cấp như Viasion Technology, cung cấp dịch vụ kỹ thuật chi phí nội bộ và kiểm tra tệp DFM miễn phí

Lựa Chọn Nhà Sản Xuất PCB 4 Lớp Phù Hợp

Quyết định về ở đâu bạn đã có pCB 4 lớp Việc sản xuất có thể ảnh hưởng lớn đến chi phí dự án, hiệu năng điện, thời gian chờ sản xuất và độ tin cậy lâu dài của thiết bị. Mặc dù quy trình sản xuất bảng mạch in (PCB) bốn lớp đã rất chín muồi, chỉ một số nhà cung cấp nhất định mới có thể đáp ứng một cách nhất quán các yêu cầu về độ chính xác, khả năng lặp lại và tài liệu kỹ thuật mà các thị trường như ô tô, công nghiệp, y tế và điện tử tiêu dùng đòi hỏi.

1. Chứng nhận và Tuân thủ

Hãy tìm các nhà sản xuất được chứng nhận theo:

- UL (Underwriters Laboratories): Đảm bảo tuân thủ tiêu chuẩn chống cháy và đặc tính vận hành an toàn.

- ISO 9001 (Hệ thống Chất lượng): Chứng tỏ kiểm soát quy trình và tài liệu kỹ thuật vững chắc từ thiết kế đến giao hàng.

- ISO 13485 (Y tế): Bắt buộc đối với các bộ phận và thiết bị PCB đạt tiêu chuẩn y tế.

- Môi trường (RoHS, REACH): Chỉ ra việc kiểm soát các chất nguy hại và tuân thủ thị trường toàn cầu.

2. Khả năng Kỹ thuật và Kinh nghiệm

Một nhà sản xuất bảng mạch in 4 lớp hàng đầu cần đáp ứng:

- Kiểm soát Cấu trúc Lớp Chính xác: Có khả năng cung cấp độ dung sai chặt chẽ về độ dày điện môi, trọng lượng đồng và hình học lỗ via.

- Công nghệ Via Tiên tiến: Via lỗ xuyên, via ẩn/chìm, via trên pad, và khoan ngược để phục vụ các thiết kế tốc độ cao, mật độ cao và cấu trúc lớp tùy chỉnh.

- Sản xuất Trở kháng Điều khiển: Coupon kiểm tra trở kháng tại chỗ, bàn kiểm tra đối ứng, và chuyên môn trong các thiết kế đơn cực vi sai.

- Tấm hóa Linh hoạt: Sử dụng hiệu quả vật liệu cho các kích thước và hình dạng bảng mạch khác nhau, đi kèm tư vấn nội bộ để giúp giảm chi phí mỗi bảng mạch.

- Dịch vụ Từ A Đến Z: Bao gồm tạo mẫu nhanh, sản xuất quy mô lớn và các tùy chọn gia tăng giá trị như lắp ráp chức năng, phủ bảo vệ chức năng và hoàn thiện hộp.

3. Giao tiếp và Hỗ trợ

Tốc độ phản hồi và hỗ trợ kỹ thuật rõ ràng là yếu tố phân biệt các nhà cung cấp PCB tốt:

- Đánh giá DFM và Cấu trúc lớp sớm: Chủ động phát hiện các vấn đề về DFM hoặc trở kháng trước khi bắt đầu gia công.

- Đội ngũ Kỹ thuật sử dụng Tiếng Anh: Đối với khách hàng quốc tế, đảm bảo không có thông tin nào bị sai lệch do ngôn ngữ.

- Báo giá và Theo dõi Trực tuyến: Công cụ báo giá thời gian thực và theo dõi trạng thái đơn hàng giúp tăng tính minh bạch và độ chính xác trong lập kế hoạch dự án.

4. Dịch vụ giá trị gia tăng

- Hỗ trợ Thiết kế và Bố trí Mạch in (PCB): Một số nhà cung cấp có thể xem xét hoặc đồng thiết kế bố cục để đảm bảo khả năng sản xuất tối ưu hoặc độ toàn vẹn tín hiệu.

- Tìm nguồn linh kiện và lắp ráp: Lắp ráp trọn gói làm giảm đáng kể thời gian chờ và hậu cần cho các mẫu thử hoặc lô chạy thử nghiệm.

- Từ chế tạo mẫu đến sản xuất hàng loạt: Chọn một cơ sở có thể mở rộng theo khối lượng đơn hàng của bạn, cung cấp kiểm soát quy trình ổn định từ bo mạch đầu tiên đến đơn vị triệu.

5. Vị trí và hậu cần

- Khu vực Thâm Quyến/Quảng Đông: Trung tâm toàn cầu về sản xuất bảng mạch in nhiều lớp chất lượng cao, nhanh chóng, với chuỗi cung ứng trưởng thành, nguồn vật liệu dồi dào và hạ tầng xuất khẩu vững mạnh.

- Các lựa chọn phương Tây: Bắc Mỹ hoặc Châu Âu cung cấp gia công đạt chứng nhận UL/ISO với chi phí nhân công cao hơn—phù hợp nhất cho khối lượng thấp đến trung bình yêu cầu thời gian giao hàng ngắn hoặc tuân thủ quy định đặc biệt.

Cách chọn nhà sản xuất bảng mạch in 4 lớp

|

Bước kiểm tra

|

Kiểm tra/Gi hỏi những gì

|

|

CHỨNG NHẬN

|

Yêu cầu/xem tài liệu UL, ISO9001, ISO13485, RoHS

|

|

Báo cáo mẫu

|

Xem xét hình ảnh thiết diện ngang, kết quả kiểm tra trở kháng, hình ảnh AOI

|

|

Thời gian phản hồi kỹ thuật

|

Gửi email một câu hỏi về cấu trúc lớp—câu trả lời có mang tính kỹ thuật và nhanh chóng không?

|

|

Hỗ trợ bố trí bảng mạch (panelization)/DFM

|

Họ có giúp bạn bố trí các tệp Gerber để tối ưu hóa không?

|

|

Tính linh hoạt về khối lượng

|

Họ có thể mở rộng quy mô từ 5 mẫu thử nghiệm lên 10.000 bảng mạch trở lên không?

|

|

Dịch vụ sau bán hàng

|

Bảo hành, RMA hoặc phân tích nguyên nhân gốc rễ khi phát sinh sự cố

|

Ứng dụng của PCB 4 lớp trong điện tử hiện đại

Sự linh hoạt, độ tin cậy và lợi ích về hiệu suất của pCB 4 lớp đã khiến chúng trở thành lựa chọn ưu tiên trong nhiều ứng dụng điện tử hiện đại. Sự kết hợp tối ưu giữa tính toàn vẹn tín hiệu, giảm nhiễu EMI, mật độ bố trí đường nối và cung cấp nguồn điện đã biến bảng mạch in 4 lớp thành công nghệ nền tảng trong hầu như mọi phân khúc thị trường nơi mà độ phức tạp, kích thước hay hiệu suất điện là yếu tố quan trọng.

1. Điện tử tiêu dùng

- Thiết bị đeo và thiết bị thông minh Các thiết bị theo dõi sức khỏe nhỏ gọn, đồng hồ thông minh và máy theo dõi sức khỏe di động dựa vào cấu trúc PCB 4 lớp để tích hợp các vi điều khiển tiên tiến, bộ thu phát không dây và mảng cảm biến trong các thiết kế nhỏ gọn.

- Bộ định tuyến và điểm truy cập Các thiết bị mạng tốc độ cao sử dụng quy trình sản xuất PCB 4 lớp để đảm bảo trở kháng được kiểm soát chính xác, duy trì chất lượng tín hiệu cho các giao diện USB 3.x, Wi-Fi và Ethernet.

- Hệ thống Máy chơi game và Trung tâm Giải trí tại nhà Các bo mạch chủ PC dày đặc, bộ điều khiển và thiết bị truyền dữ liệu tốc độ cao được hưởng lợi từ cấu trúc nhiều lớp để giảm nhiễu, cải thiện quản lý nhiệt và hỗ trợ CPU tiên tiến cùng đồ họa rời.

2. Điện tử ô tô

- Đơn vị điều khiển điện tử (ecus) Các phương tiện hiện đại sử dụng hàng chục bộ điều khiển điện tử (ECU), tất cả đều yêu cầu các bo mạch in nhiều lớp chắc chắn, miễn nhiễm với nhiễu điện từ (EMI) để điều khiển hệ thống truyền động, túi khí, phanh và giải trí đa phương tiện.

- Hệ thống hỗ trợ lái xe tiên tiến (adas) thiết kế bo mạch in 4 lớp làm nền tảng cho radar, LIDAR và các giao diện camera tốc độ cao, nơi việc truyền tín hiệu ổn định và hiệu suất nhiệt là yếu tố then chốt.

- Quản lý Pin và Điều khiển Nguồn điện Trong xe điện (EV) và xe lai, cấu trúc 4 lớp xử lý việc phân phối dòng điện cao, cách ly sự cố và truyền thông đáng tin cậy giữa các mô-đun pin.

3. Công nghiệp & Tự động hóa

- Cổng kết nối và Mô-đun Truyền thông Các mạng điều khiển công nghiệp (Ethernet, Profibus, Modbus) sử dụng bo mạch in 4 lớp cho các giao diện bền bỉ và nguồn điện ổn định.

- Bộ điều khiển PLC và Robot Các bố trí dày đặc, thiết kế tín hiệu hỗn hợp và cách ly nguồn được thực hiện hiệu quả thông qua cấu trúc nhiều lớp, cải thiện thời gian hoạt động của máy và giảm nhiễu.

- Thiết bị Đo lường & Kiểm thử Các mạch tương tự chính xác và mạch kỹ thuật số tốc độ cao đòi hỏi định tuyến trở kháng điều khiển, giảm nhiễu xuyên âm và thiết kế mạng phân phối điện (PDN) cẩn thận—tất cả đều là điểm mạnh của mạch in bốn lớp.

4. Thiết bị Y tế

- Thiết bị chẩn đoán và giám sát di động Từ máy đo độ bão hòa oxy đến điện tâm đồ di động, quy trình sản xuất mạch in 4 lớp hỗ trợ thu nhỏ kích thước, thiết kế tín hiệu hỗn hợp và vận hành đáng tin cậy trong các sản phẩm y tế quan trọng về an toàn.

- Thiết bị cấy ghép và thiết bị đeo trên cơ thể Tính tương thích sinh học nghiêm ngặt, độ tin cậy và nhiễu điện từ thấp được đảm bảo nhờ cấu trúc lớp được thiết kế tốt, đạt chứng nhận theo tiêu chuẩn ISO13485 và IPC-A-610 Class 3.

5. IoT, Viễn thông và Hạ tầng Dữ liệu

- Cổng kết nối, Cảm biến và Thiết bị biên Các sản phẩm IoT công suất thấp nhưng mật độ cao đạt được độ tin cậy và hiệu suất thông qua cấu trúc nhiều lớp hiện đại, thường tích hợp không dây, tín hiệu tương tự và kỹ thuật số tốc độ cao trên một bo mạch nhỏ gọn duy nhất.

- Backplane và Mô-đun Tốc độ Cao Bộ định tuyến, công tắc và máy chủ dựa vào các bo mạch 4 lớp và các bo mạch phức tạp hơn để truyền tín hiệu nhanh, chống nhiễu và kiến trúc đường điện ổn định.

Bảng: Các Ứng dụng Mẫu và Lợi thế Cấu trúc Lớp

|

Loại Ứng Dụng

|

lợi ích của PCB 4 lớp

|

Các Yêu cầu Chính Điển hình

|

|

Thiết bị đeo / Tiêu dùng

|

Nhỏ gọn, EMI thấp, mật độ cao

|

Trở kháng điều khiển, thu nhỏ kích thước

|

|

ECU ô tô / ADAS

|

Độ tin cậy, khả năng miễn nhiễm EMI

|

Tiêu chuẩn ISO/phương tiện, công suất mạnh, SI, EMC

|

|

Robot Công Nghiệp

|

Tính toàn vẹn tín hiệu, độ bền

|

Mặt phẳng nguồn/mass, không gian định tuyến tăng thêm

|

|

Thiết bị Y tế

|

Giảm nhiễu, tuổi thọ dài

|

ISO13485, nguồn/mass sạch, EMI thấp

|

|

Cổng IoT

|

Tích hợp RF/số, kích thước nhỏ

|

Cấu trúc lớp sạch, chân linh hoạt, độ tin cậy cao

|

Câu hỏi thường gặp (FAQ)

1. Tấm mạch in 4 lớp cải thiện hiệu suất EMI như thế nào?

A pCB 4 lớp cho phép một mặt mass vững chắc ngay bên dưới các lớp tín hiệu, tạo ra các đường hồi tiếp rất hiệu quả cho dòng điện tốc độ cao. Điều này giảm thiểu diện tích vòng lặp, giảm mạnh phát xạ EMI và bảo vệ các tín hiệu nhạy cảm khỏi nhiễu. Khác với các bảng mạch 2 lớp, các mặt phẳng nội bộ trong cấu trúc 4 lớp hấp thụ và điều hướng lại nhiễu bức xạ, giúp thiết bị vượt qua kiểm định tương thích điện từ (EMC) ngay từ lần thử đầu tiên.

2. Khi nào tôi nên nâng cấp từ mạch in 2 lớp lên 4 lớp?

Nâng cấp lên pCB 4 lớp nếu:

- Bạn cần chạy các tuyến truyền dữ liệu tốc độ cao (USB, HDMI, PCIe, DDR, v.v.).

- Thiết kế của bạn không đáp ứng được tiêu chuẩn nhiễu điện từ phát xạ/phát tán.

- Bạn gặp khó khăn khi bố trí các linh kiện hiện đại mật độ cao mà không cần quá nhiều via hoặc cách đi dây rối rắm.

- Phân phối nguồn ổn định và điện áp chênh lệch thấp trên mặt đất là yếu tố thiết yếu.

3. Tôi nên chọn độ dày đồng nào cho mạch in 4 lớp?

- 1 oz (35µm) mỗi lớp là tiêu chuẩn—đủ phù hợp với hầu hết các thiết kế số và hỗn hợp tín hiệu.

- 2 oz trở lên được khuyến nghị cho các đường dẫn dòng cao hoặc yêu cầu tản nhiệt khắt khe (ví dụ: bộ nguồn, bộ điều khiển LED).

- Hãy luôn chỉ định trọng lượng đồng riêng biệt cho cả các lớp tín hiệu và lớp mặt phẳng trong cấu trúc lớp của bạn.

4. Mạch in 4 lớp có hỗ trợ trở kháng điều khiển cho tín hiệu tốc độ cao không?

Có! Với thiết kế cấu trúc lớp phù hợp và kiểm soát chặt chẽ độ dày điện môi, mạch in 4 lớp rất lý tưởng cho 50Ω đơn và cặp vi sai 90–100Ω . Các nhà sản xuất bảng mạch hiện đại sẽ chế tạo các mẫu thử để đo và chứng nhận trở kháng trong phạm vi ±10% (theo IPC-2141A).

5. Những yếu tố chính nào ảnh hưởng đến chi phí sản xuất mạch in 4 lớp?

- Loại vật liệu lõi/prepreg (FR-4 so với vật liệu tần số cao, nhiệt độ chuyển thủy tinh cao, v.v.)

- Kích thước bảng mạch, tổng số lượng và hiệu suất sử dụng tấm panel

- Số lớp và độ dày đồng

- Chiều rộng đường dẫn/khoảng cách tối thiểu và đường kính lỗ via

- Lớp phủ bề mặt (ENIG, HASL, OSP, bạc/thiếc ngâm)

- Chứng nhận (UL, ISO, RoHS, Ô tô/Y tế)

Kết luận & Các điểm chính

Làm chủ sản xuất bảng mạch in 4 lớp —từ thiết kế stackup cẩn thận đến sản xuất tỉ mỉ và kiểm tra kỹ lưỡng—giúp tạo ra các thiết bị điện tử hiện đại một cách tự tin, chính xác và nhanh chóng. Mạch in 4 lớp vẫn là điểm 'lý tưởng' trong việc cân bằng độ phức tạp, hiệu suất điện và tổng chi phí lắp đặt, mang lại kết quả đáng tin cậy cho mọi thứ, từ các thiết bị tiêu dùng nhỏ gọn đến bộ điều khiển điện tử ô tô (ECU) và thiết bị chẩn đoán y tế.

Tóm tắt: Điều gì làm cho mạch in 4 lớp trở nên thiết yếu?

- Tính toàn vẹn tín hiệu & Ức chế EMI: Các mặt phẳng nối đất và cấp nguồn bên trong riêng biệt trong cấu trúc mạch in 4 lớp đảm bảo tham chiếu tín hiệu ổn định, giảm nhiễu xuyên âm và đáp ứng các tiêu chuẩn EMC khắt khe ngày nay.

- Mật độ bố trí cao hơn: Gấp đôi số lớp đồng so với mạch in 2 lớp làm tăng đáng kể lựa chọn linh kiện và giúp hiện thực hóa các sản phẩm nhỏ gọn, dày đặc hơn mà không gặp rắc rối trong việc bố trí mạch.

- Phân phối điện đáng tin cậy: Các mặt phẳng chuyên dụng đảm bảo việc cung cấp điện với điện trở thấp và độ cảm ứng thấp đến từng thành phần — cho phép các đường điện ổn định và hỗ trợ các bộ xử lý hiệu suất cao hoặc mạch tương tự.

- Độ phức tạp tiết kiệm chi phí: việc sản xuất và lắp ráp mạch in 4 lớp hiện đã chín muồi, giá cả phải chăng và có sẵn trên toàn cầu — cho phép sản xuất nhanh chóng và quy mô lớn, dù bạn cần năm hay năm mươi nghìn mạch in.

Những nguyên tắc vàng cho mạch in 4 lớp chất lượng cao

Luôn xác định rõ cấu trúc lớp và yêu cầu trở kháng ngay từ đầu. Lập kế hoạch sớm (kết hợp cùng nhà sản xuất) sẽ tránh được những bất ngờ về sau và đảm bảo các mạng tốc độ cao hoặc mạng tương tự hoạt động đúng như thiết kế.

Bảo vệ các mặt phẳng và duy trì đường hồi tiếp tốt. Tránh các khe hở/cắt lỗ không cần thiết trên các mặt nối đất/nguồn. Tuân thủ các thực hành tốt nhất theo tiêu chuẩn IPC-2221/2222 để đảm bảo các mặt phẳng liền mạch và khoảng cách tối thiểu chính xác.

Tận dụng các công cụ CAD chuyên nghiệp cho thiết kế mạch in. Sử dụng Altium, Eagle, KiCad hoặc phần mềm ưa thích của bạn, và luôn kiểm tra kỹ lưỡng bản xuất Gerber/drill để đảm bảo rõ ràng và đầy đủ.

Yêu cầu và kiểm tra chất lượng. Chọn nhà cung cấp có kiểm tra AOI, kiểm tra mạch trong (in-circuit) và kiểm tra trở kháng, cùng các chứng nhận ISO/UL/IPC. Yêu cầu mẫu cắt ngang hoặc phiếu kiểm tra trở kháng đối với các thiết kế độ tin cậy cao.

Tối ưu hóa cho bảng mạch và quy trình. Làm việc với nhà sản xuất của bạn để điều chỉnh bố trí phù hợp với kích thước bảng mạch và quy trình ưu tiên của họ—điều này thường giúp giảm giá thành từ 10–30% mà không ảnh hưởng đến hiệu suất.

Tin Tức Nổi Bật

Tin Tức Nổi Bật