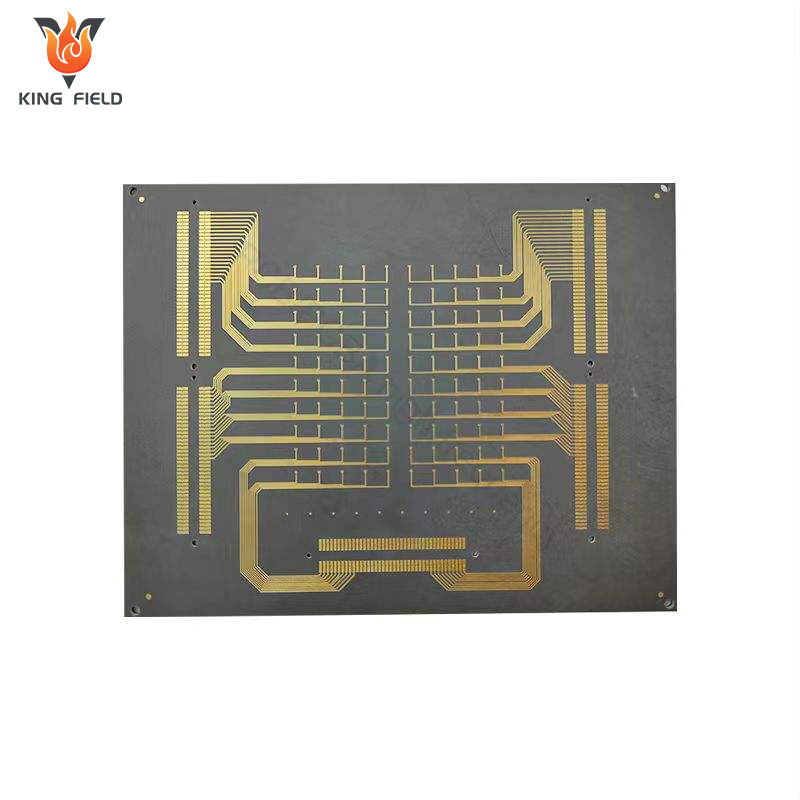

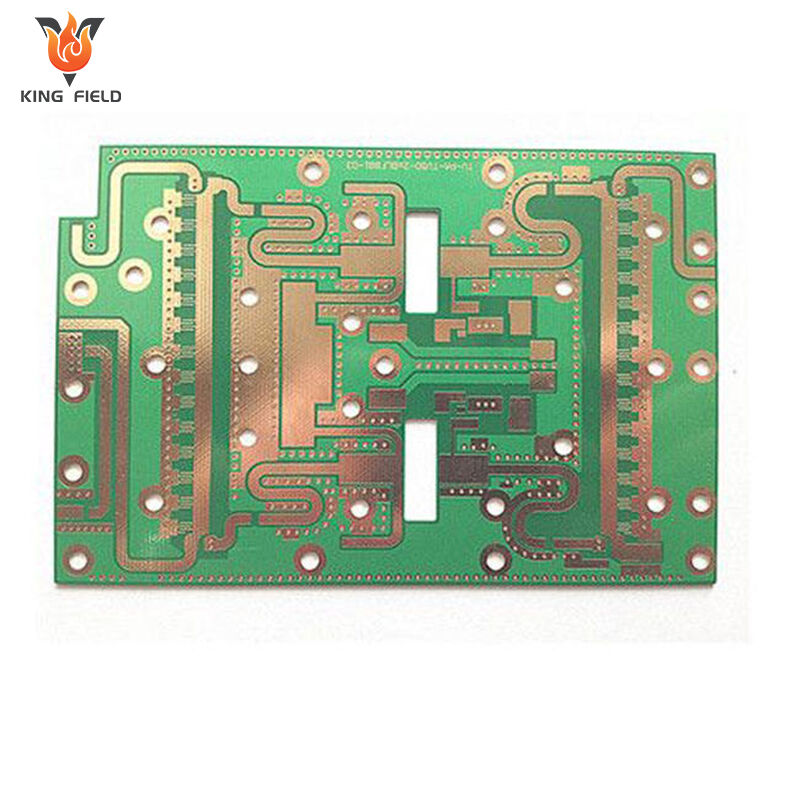

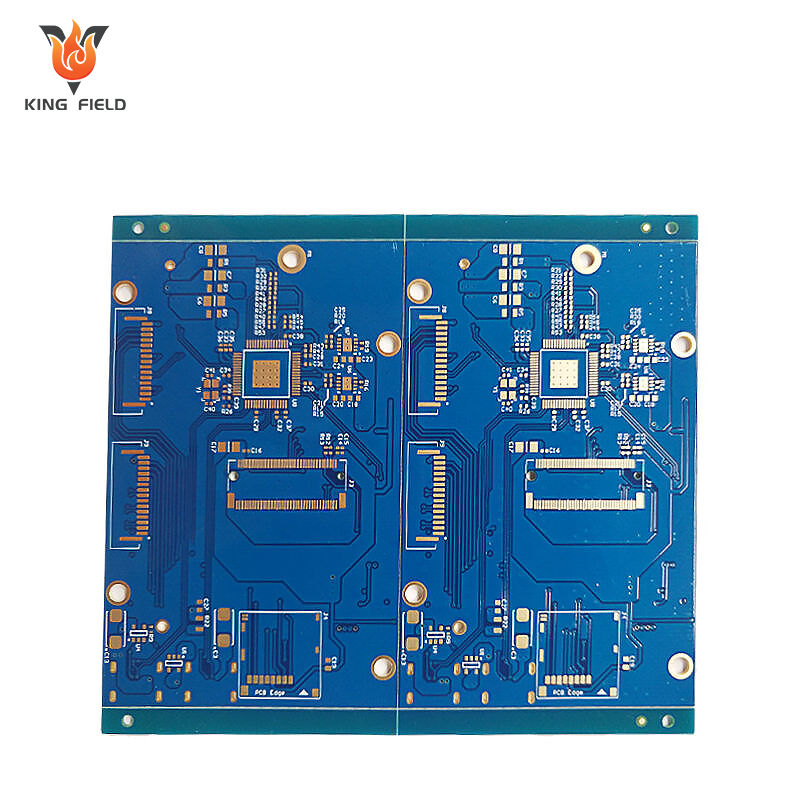

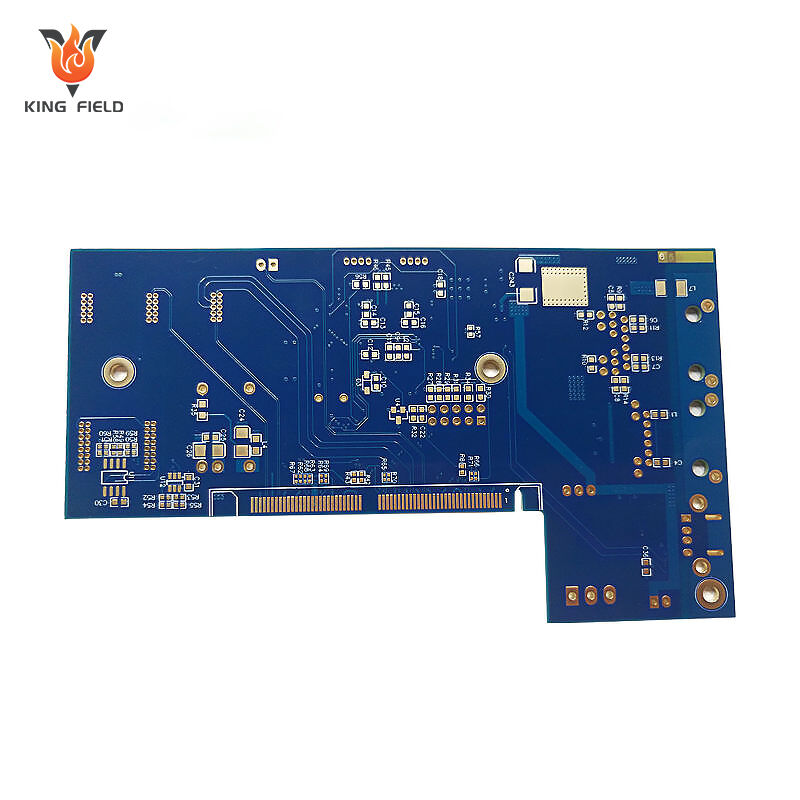

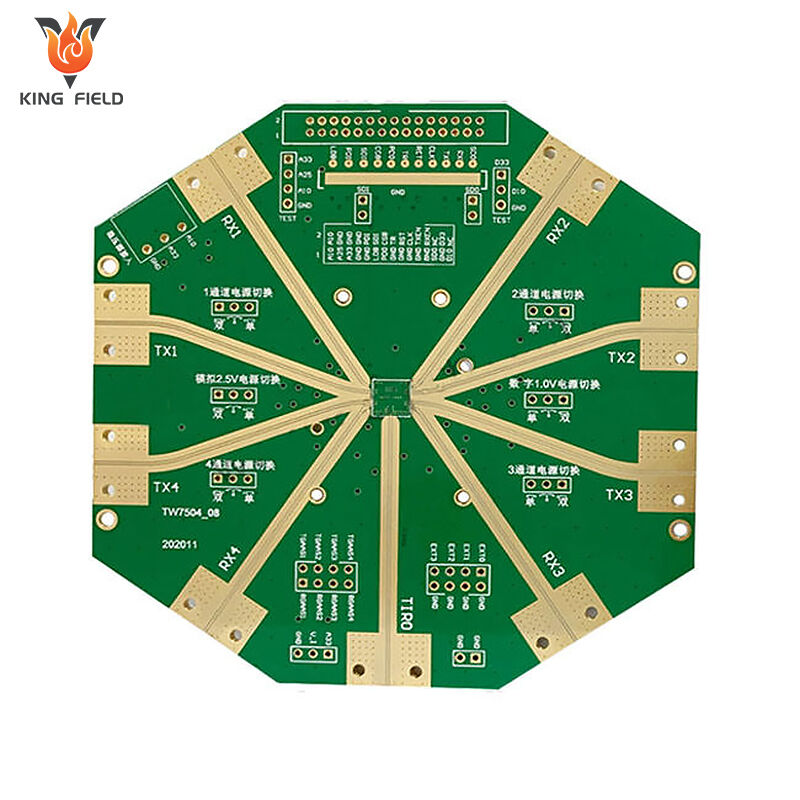

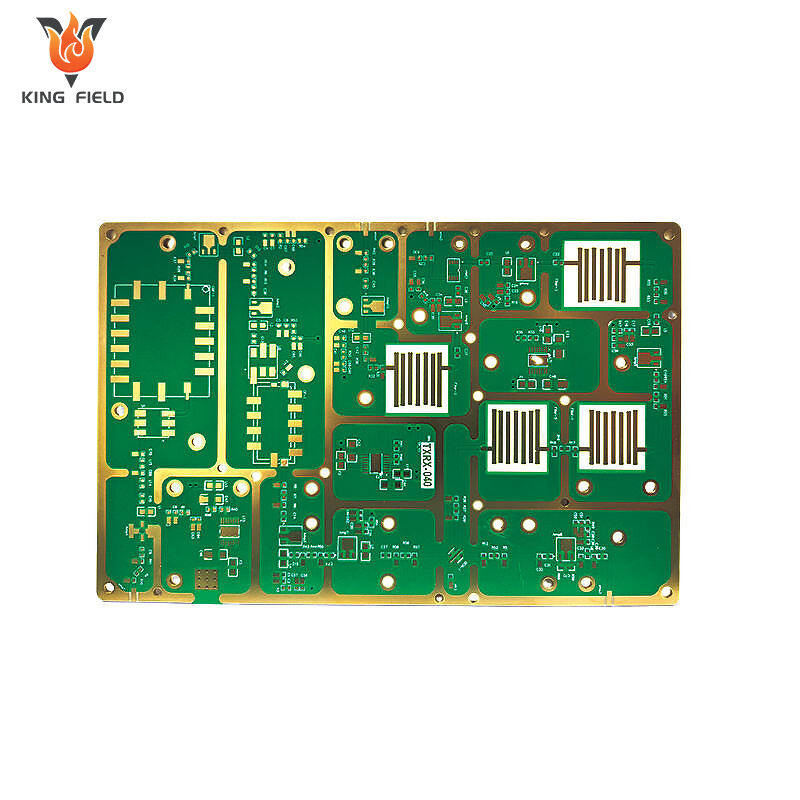

Mạch in Tần số Cao

Mạch in PCB tần số cao hiệu suất cao cho các ứng dụng RF, vi sóng và tín hiệu tốc độ cao. Vật liệu cao cấp ít tổn hao (PTFE/Rogers), kiểm soát trở kháng chính xác, và mẫu trong 24 giờ + giao hàng nhanh. Hỗ trợ DFM và kiểm tra chất lượng đảm bảo hiệu suất ổn định ở tần số GHz.

✅ Vật liệu ít tổn hao để đảm bảo toàn vẹn tín hiệu

✅ Kiểm soát trở kháng chính xác (±5%)

✅ Tập trung vào RF/viễn thông/dữ liệu tốc độ cao

Mô tả

Mạch in tần số cao là gì?

Mạch in tần số cao là loại mạch in sử dụng các lớp nền chuyên dụng có hằng số điện môi thấp (Dk) và tổn hao điện môi thấp (Df), chẳng hạn như PTFE và dòng Rogers. Nó yêu cầu kiểm soát trở kháng nghiêm ngặt và bố trí dây dẫn được tối ưu hóa để giảm các thông số ký sinh. Nó được thiết kế đặc biệt cho các tình huống truyền tín hiệu tần số cao dao động từ 300 MHz đến 3 GHz. Các bảng mạch in độ chính xác cao tương thích rộng rãi với thiết bị trong các lĩnh vực như viễn thông, công nghiệp quân sự, y tế chăm sóc và điện tử tiêu dùng.

Đặc điểm của bảng mạch in tần số cao

Các đặc điểm của mạch truyền thông tần số cao được thiết kế xoay quanh ba yêu cầu cốt lõi là tổn hao thấp, độ ổn định cao và chống nhiễu trong quá trình truyền tín hiệu tần số cao dao động từ 300 MHz đến 3 GHz. Mỗi đặc điểm tương ứng với việc lựa chọn vật liệu cụ thể, tiêu chuẩn quy trình và giá trị ứng dụng. Dưới đây là phân tích chi tiết:

Đặc tính tổn hao thấp của lớp nền

Khi truyền tín hiệu tần số cao, sẽ xảy ra tổn thất năng lượng do tính chất điện môi của lớp nền. Đây là điểm khác biệt cốt lõi giữa mạch tần số cao và bảng mạch in thông thường.

Thông số kỹ thuật chính

· Hằng số điện môi thấp (Dk): Hằng số điện môi quyết định tốc độ truyền tín hiệu. Giá trị Dk càng thấp, tốc độ truyền tín hiệu càng nhanh và độ trễ tín hiệu càng nhỏ. Giá trị Dk của PCB tần số cao thường ổn định trong khoảng từ 2,2 đến 4,5 (Dk của các tấm nền FR-4 thông thường vào khoảng 4,6 đến 4,8), và cần đảm bảo độ ổn định của Dk ở các nhiệt độ và tần số khác nhau để tránh méo tín hiệu.

· Tang số tổn thất điện môi thấp (Df): Giá trị Df phản ánh trực tiếp mức tổn thất năng lượng của tín hiệu trong chất nền. Df càng thấp, tổn thất càng nhỏ. Giá trị Df của các chất nền PCB tần số cao nói chung nhỏ hơn 0.002 (Df của fR-4 thông thường khoảng 0,02), có thể hiệu quả giảm suy hao tín hiệu và đặc biệt phù hợp cho việc truyền tín hiệu tần số cao và khoảng cách xa.

Tấm nền điển hình

· PTFE (Polytetrafluoroethylene): Dk≈2.1, Df≈0.0009, chịu nhiệt độ cao (trên 260℃), độ ổn định hóa học mạnh, là lựa chọn hàng đầu cho các ứng dụng yêu cầu cao như công nghiệp quân sự và viễn thông vệ tinh.

· Dòng sản phẩm Rogers (ví dụ RO4350B): Dk≈3.48, Df≈0.0037, có độ ổn định trở kháng tuyệt vời, phù hợp cho trạm gốc 5G và các mô-đun RF.

· Tấm nhựa epoxy tần số cao: Chi phí thấp hơn, Dk≈3.5-4.0, đáp ứng các yêu cầu cơ bản của linh kiện RF trong thiết bị điện tử tiêu dùng.

Đặc tính kiểm soát trở kháng độ chính xác cao

Tín hiệu tần số cao rất nhạy cảm với sự thay đổi trở kháng. Sự không phù hợp trở kháng có thể gây phản xạ tín hiệu, sóng đứng và méo dạng, ảnh hưởng trực tiếp đến hiệu suất thiết bị.

· Tiêu chuẩn kiểm soát trở kháng: Các giá trị trở kháng thường dùng cho PCB tần số cao là 50Ω và 75Ω. Dung sai trở kháng nên được kiểm soát trong khoảng ±3% đến ±5%.

· Phương pháp thực hiện: Bằng cách thiết kế chính xác bốn thông số cốt lõi - bề rộng đường dẫn, khoảng cách đường dẫn, độ dày lớp nền và độ dày lá đồng - và xác minh chúng bằng phần mềm mô phỏng điện từ trường, đảm bảo tính nhất quán về trở kháng. Ví dụ, giá trị trở kháng của cấu trúc đường truyền vi dải tỷ lệ thuận với bề rộng dây dẫn và tỷ lệ nghịch với độ dày lớp nền. Cần phải điều chỉnh lặp đi lặp lại để đạt được giá trị mục tiêu.

Thông số ký sinh thấp và đặc tính chống nhiễu

Trong các mạch tần số cao, điện dung ký sinh và độ tự cảm của dây dẫn có thể tạo ra các nguồn nhiễu bổ sung, dẫn đến hiện tượng nhiễu xuyên âm hoặc bức xạ điện từ (EMI). Do đó, các PCB tần số cao cần được thiết kế và tối ưu hóa nhằm giảm các hiệu ứng ký sinh.

Thiết kế thông số ký sinh thấp

· Rút ngắn chiều dài dây dẫn, giảm việc đi dây vòng vèo và giảm điện cảm ký sinh;

· Tăng khoảng cách giữa các đường tín hiệu hoặc sử dụng dải cách ly nối đất để giảm điện dung ký sinh;

· Sử dụng các cấu trúc đường truyền đặc biệt như đường truyền vi dải (microstrip lines) và đường truyền dải (ribbon lines) nhằm giảm ghép nối điện từ giữa các tín hiệu và môi trường bên ngoài;

Khả năng chống nhiễu điện từ (EMI)

· Tăng số lượng lớp nối đất để tạo thành "buồng chắn sóng" và ngăn chặn nhiễu điện từ bên ngoài;

· Thực hiện che chắn cục bộ các linh kiện nhạy cảm để giảm bức xạ tín hiệu bên trong;

· Tối ưu hóa bố trí nguồn điện và tiếp đất để giảm ảnh hưởng của nhiễu nguồn lên các tín hiệu tần số cao.

Các đặc tính thích nghi vật lý và môi trường tuyệt vời

Các kịch bản ứng dụng của PCB tần số cao chủ yếu nằm trong các lĩnh vực có yêu cầu nghiêm ngặt về môi trường như điều khiển công nghiệp, y tế và công nghiệp quân sự. Do đó, vật liệu nền và quy trình cần phải đáp ứng các yêu cầu hiệu suất vật lý bổ sung

· Khả năng chịu nhiệt độ cao: Một số vật liệu nền có thể chịu được nhiệt độ trên 260℃, đáp ứng yêu cầu xử lý của hàn hồi lưu và hàn sóng, đồng thời phù hợp với việc vận hành thiết bị lâu dài trong môi trường nhiệt độ cao.

· Khả năng chống hóa chất: Vật liệu nền phải có đặc tính chống axit, kiềm và chống ẩm để ngăn ngừa hiện tượng tách lớp của vật liệu nền và oxy hóa lá đồng trong môi trường khắc nghiệt.

· Ổn định cơ học: Lá đồng có lực bám dính mạnh với lớp nền, làm giảm khả năng cong vênh hoặc biến dạng, đảm bảo độ tin cậy của thiết bị trong điều kiện rung động và va đập.

Đặc tính độ chính xác chế tạo cao

Độ chính xác công nghệ gia công của PCB tần số cao cao hơn nhiều so với PCB thông thường. Các yêu cầu chính của quy trình bao gồm:

· Độ rộng vạch/khoảng cách giữa các vạch nhỏ: Có thể đạt được độ rộng vạch và khoảng cách 3mil/3mil (0.076mm/0.076mm) hoặc thậm chí nhỏ hơn, đáp ứng yêu cầu đi dây của các mạch mật độ cao và tần số cao.

· Khoan chính xác: Đường kính lỗ tối thiểu có thể đạt 0.1mm, và dung sai vị trí lỗ được kiểm soát trong phạm vi ±0.01mm, tránh những thay đổi trở kháng do sai lệch vị trí lỗ.

· Xử lý bề mặt: Quá trình mạ vàng và mạ bạc thường được áp dụng để giảm tổn thất tín hiệu trên bề mặt dây dẫn .

Các vật liệu được sử dụng trong mạch in tần số cao

Chất nền lõi

Chất nền là nền tảng của PCB tần số cao và ảnh hưởng trực tiếp đến tổn hao và độ ổn định truyền tín hiệu. Các loại và thông số phổ biến hiện nay như sau:

| Loại nền | Các thông số cốt lõi | Ưu Thế | Các tình huống áp dụng | ||

| PTFE | Dk≈2,1, Df≈0,0009 | Tổn hao cực thấp, chịu nhiệt độ cao (260℃+), độ ổn định hóa học cao và khả năng chống ẩm tốt | Ra-đa quân sự, thông tin vệ tinh, thiết bị vi sóng và tần số vô tuyến | ||

| Dòng Rogers | Lấy ví dụ RO4350B: Dk≈3,48, Df≈0,0037 | Sản phẩm có độ ổn định trở kháng cực cao, tổn hao thấp và khả năng gia công tốt | trạm phát 5G, mô-đun RF, linh kiện tần số cao điều khiển công nghiệp | ||

| Tấm epoxy resin tần số cao | Dk≈3,5-4,0, Df≈0,005-0,01 | Chi phí thấp, dễ gia công và khả năng tương thích tốt | Linh kiện RF điện tử tiêu dùng, thiết bị tần số cao cấp nhập môn | ||

| Chất nền chứa gốm | Dk≈4,0-6,0, Df≈0,002-0,004 | Độ dẫn nhiệt cao và độ ổn định kích thước tốt | Thiết bị tần số cao công suất lớn, mô-đun RF cấp ô tô | ||

Vật liệu lá đồng

Tín hiệu tần số cao có hiệu ứng da, do đó việc chọn lá đồng cần cân nhắc cả hiệu suất dẫn điện và độ phẳng bề mặt:

· Lá đồng điện phân: Chi phí thấp, độ nhám bề mặt ở mức trung bình, phù hợp với hầu hết các tình huống PCB tần số cao;

· Lá đồng cán: Bề mặt nhẵn hơn, tổn thất hiệu ứng da ít hơn, phù hợp với thiết bị tần số vô tuyến cao tần và độ nhạy cao;

· Độ dày lá đồng: Thường dùng là 1oz (35μm) hoặc ½oz (17.5μm). Lá đồng mỏng có thể giảm cảm kháng ký sinh và phù hợp hơn cho mạch đi dây mật độ cao và tần số cao.

Vật liệu xử lý bề mặt

Xử lý bề mặt của PCB tần số cao cần giảm điện trở tiếp xúc, ngăn ngừa sự oxy hóa của lá đồng và tránh ảnh hưởng đến việc truyền tín hiệu tần số cao

· Mạ vàng (ENIG): Bề mặt nhẵn, khả năng chống oxy hóa mạnh, điện trở tiếp xúc thấp, ảnh hưởng nhỏ đến tổn hao tín hiệu tần số cao, phù hợp với các giao diện RF độ chính xác cao.

· Mạ bạc: Có độ dẫn điện tốt hơn mạ vàng và tổn hao thấp hơn, nhưng dễ bị oxy hóa và cần kết hợp với lớp phủ chống oxy hóa. Phù hợp với các mạch vi sóng tần số cao.

· Mặt nạ hàn hữu cơ (OSP): Có chi phí thấp và quy trình đơn giản, nhưng khả năng chịu nhiệt độ cao ở mức trung bình. Phù hợp với các PCB tần số cao trong thiết bị điện tử tiêu dùng nhạy cảm về chi phí.

Lợi thế của các bảng mạch in tần số cao

Suy hao tín hiệu thấp đảm bảo chất lượng truyền dẫn

Bằng cách sử dụng các vật liệu nền chuyên dụng có hằng số điện môi thấp (Dk) và tổn thất điện môi thấp (Df), chẳng hạn như PTFE và dòng Rogers, tổn thất năng lượng của tín hiệu tần số cao trong khoảng từ 300 MHz đến 3 GHz trong quá trình truyền tải có thể được giảm hiệu quả giảm thiểu méo tín hiệu và đáp ứng được yêu cầu về truyền thông và truyền dữ liệu ở khoảng cách xa và tần số cao.

Kiểm soát trở kháng độ chính xác cao nâng cao độ toàn vẹn tín hiệu

Bằng cách thiết kế chính xác chiều rộng đường dẫn, khoảng cách giữa các đường dẫn và độ dày vật liệu nền, dung sai trở kháng được kiểm soát trong phạm vi ±3% đến ±5%, đạt được sự phối hợp ổn định với các trở kháng tiêu chuẩn như 50Ω/75Ω, tránh hiện tượng phản xạ tín hiệu và hiện tượng sóng đứng, đồng thời đảm bảo hoạt động đáng tin cậy của các mạch tần số cao như RF và vi ba.

Khả năng chống nhiễu mạnh, phù hợp với môi trường điện từ phức tạp

Cấu trúc đi dây được tối ưu hóa (như các đường vi dải và đường dải ruy băng) cùng thiết kế nối đất nhiều lớp có thể giảm điện dung ký sinh và độ tự cảm, cũng như nhiễu xuyên âm tín hiệu và bức xạ điện từ (EMI). Khi kết hợp với lớp chắn kim loại cục bộ, nó có thể chống lại sự nhiễu điện từ bên ngoài và phù hợp với các ứng dụng yêu cầu cao về tương thích điện từ, chẳng hạn như thiết bị điều khiển công nghiệp và dụng cụ y tế.

Khả năng thích nghi môi trường vượt trội, đáp ứng các điều kiện làm việc khắc nghiệt

Chất nền chuyên dụng cho tần số cao có đặc tính chịu nhiệt độ cao (trên 260℃), chống ăn mòn hóa học và chống ẩm. Khi kết hợp với quy trình liên kết lá đồng ổn định, nó có thể duy trì hoạt động ổn định trong các môi trường khắc nghiệt như rung động và chu kỳ nhiệt độ cao-thấp, đáp ứng yêu cầu vận hành lâu dài theo tiêu chuẩn ô tô và quân sự thiết bị.

Hỗ trợ tích hợp cao, tạo điều kiện thuận lợi cho thiết kế nhỏ gọn

Hỗ trợ xử lý các đường nét và khoảng cách nhỏ cỡ 3mil/3mil trở xuống, cũng như các lỗ có đường kính nhỏ. Có thể đạt được bố trí dây dẫn mật độ cao, đáp ứng yêu cầu thiết kế của các sản phẩm thu nhỏ và tích hợp cao như RF mô-đun và thành phần trạm phát 5G, đồng thời tiết kiệm không gian thiết bị.

Khả Năng Sản Xuất

| Khả năng sản xuất PCB | |||||

| mục | Khả năng sản xuất | Khoảng cách tối thiểu từ S/M đến pad, đến SMT | 0.075mm/0.1mm | Độ đồng nhất của lớp đồng mạ | z90% |

| Số lớp | 1~40 | Khoảng trống tối thiểu cho chú thích để cách đến SMT | 0.2mm/0.2mm | Độ chính xác của họa tiết so với họa tiết | ±3mil(±0.075mm) |

| Kích thước sản xuất (tối thiểu & tối đa) | 250mmx40mm/710mmx250mm | Độ dày xử lý bề mặt cho Ni/Au/Sn/OSP | 1~6um /0.05~0.76um /4~20um/ 1um | Độ chính xác của họa tiết so với lỗ | ±4mil (±0.1mm ) |

| Độ dày đồng của lớp phủ | 1/3 ~ 10z | Kích thước tối thiểu của pad đã kiểm tra E- | 8 X 8mil | Chiều rộng vạch tối thiểu/khoảng cách | 0.045 /0.045 |

| Độ dày bảng sản phẩm | 0.036~2.5mm | Khoảng cách tối thiểu giữa các pad đã kiểm tra | 8mil | Dung sai ăn mòn | +20% 0,02mm) |

| Độ chính xác cắt tự động | 0.1mm | Dung sai kích thước tối thiểu của đường viền (cạnh ngoài đến mạch) | ±0,1mm | Dung sai căn chỉnh lớp phủ | ±6mil (±0,1 mm) |

| Kích thước lỗ khoan (Tối thiểu/Tối đa/dung sai kích thước lỗ) | 0,075mm/6,5mm/±0,025mm | Dung sai kích thước tối thiểu của đường viền | ±0,1mm | Dung sai keo thừa cho ép lớp phủ | 0.1mm |

| Vênh & Cong | ≤0.5% | Bán kính góc R tối thiểu của đường viền ngoài (góc lượn trong) | 0.2mm | Dung sai căn chỉnh cho lớp phủ nhiệt hóa cứng và UV | ±0.3mm |

| tỷ lệ khía cạnh tối đa (độ dày/đường kính lỗ) | 8:1 | Khoảng cách tối thiểu từ tiếp điểm vàng đến viền ngoài | 0,075mm | Chiều rộng cầu S/M tối thiểu | 0.1mm |