עיצוב תבנית PCB: יסודות עיצוב מעגלים

הקדמה

פלטות חיבור מודפסות (PCB) מהוות את לב ליבם של כמעט כל המכשירים האלקטרוניים המודרניים, מהטלפונים החכמים ומחשבים ועד למערכות בקרה תעשייתיות וציוד רפואי. ה תבנית PCB נמצא בעולם של עיצוב לוח מעגלים , ומסרטט כל חיבור חשמלי, זרימת אותות ויחס בין רכיבים שיתגשמו במוצר הסופי. יצירת תַּיָּרָה סְכֵמָתִית תבנית ברורה ויציבה היא קריטית לא רק להצלחת חדשנות ולביצוע פונקציונלי, אלא גם לאיתור שגיאות, ייצור ובקרת איכות במהלך ייצור לוחות חיבורים מודפסים תהליך.

למה להתחיל עם עיצוב תבנית PCB?

פרויקט PCB תמיד מתחיל בתבנית מעגל מתומצתת. תרשים זה מספק ייצוג לוגי של עיצוב המעגל האלקטרוני, המפרט את כל אחד מההיבטים: החל מחלוקת הספק וארקה, תיוג רשתות, וסימני רכיבים, וכלה בארגון השיטתי של זרימת האותות. כלים לאוטומציה של עיצוב אלקטרוני (EDA) —כגון OrCAD, Altium Designer, KiCad, ו-EasyEDA—מאפשרים ללכוד את העיצובים המורכבים הללו באופן דיגיטלי, ומייצרים את היסודות לתהליכי הזרם-למטה כמו פריסת ה-PCB , אימות רשימת רשתות , ולבסוף, הרכבת לוחות PCB .

מהי חשיבותו של דיאגרמת סכמתית?

- ממחיש מעגל בעל מבנה מדויק — מהווה תבנית לעיצוב ולפתרון תקלות.

- חיוני לשיתוף פעולה בין מהנדסים, טכנאים ויצרנים.

- הנחיות לייצור ותיקון בהמשך הדרך.

רכיבים מרכזיים של תרשים PCB

- סמלים אלקטרוניים : עכברים, קondenסаторים, ICs, וכו'.

- רשתות / חוטים : חיבורים חשמליים וזרימת אותות.

- תוויות / שמות רשת : עבור אותות ברורים ומובחנים.

- סימני כוח/אדמה: נקודות זינה ויחוס מסומנות בבירור.

- מספרי זיהוי של רכיבים: לפי תקני IEEE.

הנחיות לשרטוט דיאגרמות סכמטיות של PCB

תרשים סכמטי gut של PCB הוא היסוד בפיתוח מוצר אמין, ומבטיח בהירות, יישום ייצור ויעילות שיתופית. להלן הנחיות עיקריות לעיצוב סכמטי מקצועי:

בחירת גודל עמוד מתאים

בחר ממדי עמוד המתאימים לקנה המידה והמורכבות של המעגל—הימנע מצפיפות יתר של מעגלים פשוטים או בזבוז מקום על עמודים גדולים מדי. זה מאזן בין קריאות לנוחות ניהול המסמך.

שם עמודים בסדר אלפביתי

חלק תרשימי PCB מרובי עמודים לפי מודולים פונקציונליים ושם את העמודים בסדר אלפביתי. זה מפשט את הניווט וההפניות הדדויות.

יישם מערכת רשת לנקודות ייחוס

הפעל מערכת רשת כדי להצמיד רכיבים, חיבורים וסמלים באופן אחיד. פעולה זו מפזרת את נתיבי החיבורים, מבטיחה עקביות חזותית ומקלה על הפנייה מדויקת במהלך סקרי עיצוב.

כלול בלוק כותרת בתחתית הדף

הוסף בלוק כותרת תקני בתחתית כל עמוד, שכולל מידע מטא חשוב: גודל העמוד, מספר גרסה של המסמך, מזהה ייחודי של המסמך, שם המעצב/פרטי קשר, תאריך העיצוב, ולוגו החברה. פעולה זו משפרת את האפשרות לעקוב אחר השינויים והמקצועיות.

הוסף הערות/הבהרות חשובות

הטמע הערות מפתח לפרטים קריטיים של העיצוב: תצורות גשר, אילוצי פריסת PCB, מיקומי נקודות בדיקה או דרישות מיוחדות לרכיבים. ציין את הלוגיקה שאינה ברורה במפורש כדי למנוע תפיסה שגויה.

כלול יומן גרסאות

שמור על קטע יומן גרסאות כדי לעקוב אחר שינויים. פעולה זו מבטיחה אחריות, מפשטת ניהול גרסאות ותומכת בהתאמה לסטנדרטים איכותיים.

הטמע טבלת תוכן

לפרויקטים מרובים עמודים או מורכבים, הוסף תוכן העניינים המפרט את כותרות העמודים, המודולים הפונקציונליים ומספרי העמודים המתאימים. זה מאפשר ניווט מהיר ושיפור בהנגישות של המסמך לצוותים.

השתמש בתרשים בלוקים למודולי עיצוב

התחל מתרשים בלוקים ברמה גבוהה כדי לתאר את המודולים הפונקציונליים המרכזיים ואת הקשרים ביניהם. זה מספק מבט כולל על ארכיטקטורת המערכת ועל זרימת האותות.

הצג את נתיב זרימת האותות באמצעות עיצוב היררכי

אמץ עיצוב היררכי לפירוק מעגלים מורכבים: השתמש בבלוקים עליונים למודולי המערכת ובגיליונות תחתונים למעגלים המפורטים. זה מבהיל את הקשרים בין המודולים, מפחית ערבוב ופשוט את חזרות העיצוב.

השתמש בסימוני רכיבים תקנים

עקוב אחר התקנים של IEEE/IPC לסימון רכיבים: R (נגד), C (קבל), U (מעגל משולב), D (דיודה), Q (טרנזיסטור), וכו'. סימונים עקביים מונעים בלבול ומבטיחים תאימות עם כלים תעשייתיים.

יצירת סמלים של רכיבים מס libraries סטנדרטיות

השתמשו בספריות רכיבים רשמיות או מוכחות בתעשייה ליצירת סמלים. נמנעו משימוש בסמלים מותאמים אישית אלא אם כן זה הכרחי – סטנדרטיזציה מבטיחה עקביות בין העיצובים ומצמצמת את סיכון השגיאות.

הפחתת חיבורי רשת מיותרים

מזערו חיבורים חוציים כפולים, רשתות תלוות או חיבורים לא בשימוש. השתמשו בתוויות רשת במקום חוטים ישירים עבור חיבורים שחוזרים על עצמם, כדי לשפר את הקריאה ולפשט את שינויי העיצוב.

שמירה על קריאות במקם רכיבים

סדרו את הרכיבים בצורה לוגית והימנעו מצפיפות מופרזת. סידור מסודר מקל על המעבר לעיצוב PCB ומשפר את יעילות סקירת העיצוב.

הצבת רכיבים המחוברים לאבני שדרור בקרבה רבה

הציבו אבני שדרור, משדרים קריסטליים והקיבטורים/נגדים המשויכים להם בקרבה מירבית לסיכות השעון של ה-MCU. פעולה זו ממזערת הפרעות אותות, מקצרת את אורך ה-trace ומשפרת את שלמות אות השעון.

הרצת בדיקת DRC לצורך הערכת שלמות העיצוב

הפעל בדיקת עמידה אוטומטית בכללי העיצוב (DRC) באמצעות תוכנת עיצוב סכמטי כדי לזהות שגיאות כגון פינים לא מחוברים, קצר, או הקצאות רכיבים לא חוקיות. פתר את שגיאות ה-DRC לפני המשך לתבנית.

אמת ידנית את הרשתות כדי למחוק שגיאות פוטנציאליות

השלם את בדיקת ה-DRC באימות ידני של הרשתות: בדוק שוב את כל רשתות החשמל, מסלולי האותות והחיבורים של הרכיבים. שלב זה מאתר שגיאות עדינות שעשויים להימלט ממכשירי בדיקה אוטומטיים.

צור רשימת חומרים (BOM) מלאה

צור רשימת חומרים (BOM) מקיפה הכוללת פרטים קריטיים: סימוני רכיבים, כמויות, ערכים, מספרי חלקים של היצרן (MPNs), מידע על ספקים ותבניות. רשימת חומרים מלאה מזרזת את תהליכי הקנייה והייצור.

הערות שימוש עבור Kingfield:

- התאם את חבל הכותרת והיסטוריית הגרסאות לסטנדרטים הפנימיים של Kingfield למסמכים.

- למטרות שיווק או תיעוד טכני, שים את המדריך זה בזוג עם דוגמאות סכמטיות כדי לשפר את היישום המעשי.

- התאם את ההנחיות לדרישות ספציפיות של התעשייה על ידי הוספת הערות הקשורות לעמידה בתקנות.

איך ליצור דיאגרמת עקומה אפקטיבית של עיצוב PCB

עיצוב עקום PCB אפקטיבי: מדריך קצר

- בהירות מטרות : הגדר יישום, בלוקים פונקציונליים ומגבלות.

- בחירת כלים : השתמש ב-Altium/ KiCad / Eagle לצורך תאימות ותמיכה בספריות רכיבים.

- סטנדרטיזציה של רכיבים :

-

- השתמש בסמלים/עמדות יצרן מאומתים.

- שם כ-"U1_MCU_STM32F4"; הוסף ערכים, אריזות, SPNs.

-

- קבץ בלוקים פונקציונליים באופן לוגי; מינן חיבורים חוצים.

- אמץ עיצוב היררכי ל-PCBים מורכבים.

-

- אמת תצורות פינים מול דפי נתונים; הוסף מעגלי הגנה.

- הצמד ל-IPC-2221/ISO 13485/IATF 16949; תייג רשתות קריטיות.

-

- כלול מיקומי רכיבים, הערות ל המעגלים המרכזיים, חותמת כותרת.

- שלב BOM מפורט.

-

- ביקורת עצמית/עמיתים; בדוק בדיקה של מעגלים קריטיים; אמת רשימת חיבורים.

- מסירתUILayout : ייצוא רשימות רשתות/רשימות חומרים/Gerbers; תקשורת דרישות קריטיות.

החשיבות של תרשימי PCB בעיצוב לוחות PCB

- תכנון יסוד : ממיר דרישות חשמליות ללוגיקה מעשית של עיצוב, המנחה בחירה ברכיבים, חיבורים וסידור.

- מניעת שגיאות : מאשר את שלמות המעגל מראש, מפחית קצר/כשלים פונקציונליים בייצור.

- שיתוף פעולה בין צוותים : מאחד מהנדסים באמצעות התייחסות סטנדרטית לתקשורת.

- ציות לחוק : מאפשר התאמה לתקני תעשייה דרך כוונת עיצוב מתועדת.

- איתור שגיאות ושימור : מקל על אבחון שגיאות ותיקוני ייצור לאחר הפקה.

- BOM & רכש : מייצר ישירות רשימת חומרים (BOM) מדויקת עם פרטי רכיבים לרכש.

- יכולת הרחבה וחזרתיות : תומך בעיצוב היררכי ל-PCBים מורכבים ומפשט את עדכוני העיצוב.

- שליטה בעלות : מפחית את עלות העבודה החוזרת על ידי זיהוי כשלים בעיצוב בשלבים מוקדמים, ובכך מונע איטרציות יקרות בייצור.

תהליך עיצוב סכמת PCB: צעד אחר צעד

תהליך עיצוב סכמת PCB עוקב אחר זרימת עבודה לוגית וסידורית כדי להבטיח דיוק, תאימות והעברה חלקה לעיצוב הפיזי של הלוח. כל שלב מבוסס על השלב הקודם, עם מוצרי עבודה ברורים ונקודות בקרה לאיכות:

הגדרת דרישות העיצוב

שלב יסוד זה דורש התאמה בין-פונקציונלית כדי למנוע הרחבה בלתי מבוקרת של היקף העבודה ושינויים חוזרים בעיצוב. התחל בהרשמה:

- מפרטים חשמליים : טווחי מתח קלט/פלט, הגבלות זרם פעילות, תדרי אות ודרישות עמידות לרעש.

- ארכיטקטורת חשמל : הבהרת מקורות חשמל, צורכי רגולציה של מתח וחלוקת חשמל.

- דרישות אות : זיהוי סוגי האותות, פרוטוקולי תקשורת ואילוצי אות קריטיים.

- אילוצי מכני וסביבתי : מגבלות גודל/צורה של פסיב, טווח טמפרטורת עבודה ותקנים של אמינות.

- תקנים לאישור תקינות : דרישות רגולטוריות שמשפיעות על עיצוב הסכמה.

צייר דיאגרמת בלוקים

המרה של DSD לדיאגרמת בלוקים ברמה גבוהה כדי לדמיין את ארכיטקטורת המערכת. שלבים מרכזיים:

- זיהוי מודולים פונקציונליים : פירוק המערכת לבלוקים מרכזיים.

- הגדרת חיבורים בין מודולים : שימוש בחצים כדי להצביע על זרימת אות/כוח בין הבלוקים. לתייג רשתות קריטיות.

- הפשטה של הסיבוכיות : במערכות מרובות מודולים, קבץ בלוקים קשורים. השתמש בסימנים סטנדרטיים לצורך בהירות.

- אימות עם בעלי עניין : בדוק את תרשים הבלוקים כדי לאשר שجميع הדרישות טופלו, ולבצע התאמות לפני המשך לעיצוב מפורט.

יצירת תרשים חשמלי

השתמש בתוכנת CAD מקצועית כדי ליישם את תרשים הבלוקים כתרשים מפורט. עקוב אחר עקרונות אופטימליים אלו:

- הגדרת פרמטרים של הפרויקט : הגדר גודל עמוד, מערכת רשת ותבניות עיצוב לפני תחילת העבודה.

-

מיקום רכיבים :

- השתמש בספריות סטנדרטיות להצבת רכיבים—הימנע מסמלים מותאמים אישית אלא אם יש צורך מוחלט בכך.

- קבץ רכיבים לפי מודולים פונקציונליים וסדר אותם בהתאם לצרימת אותות לוגית.

- שמור על רכיבים קריטיים נגישים להערות עתידיות ולהפניות צולבות.

-

נתיבי חיווט :

- השתמש במערכת הרשת כדי להצמיד את הנתיבים ולהימנע מחוטים מבולגנים וחופפים.

- החלף חוטים ארוכים ומיותרים בתוויות נתיב.

- בעיצובים היררכיים, צור גיליון עליון עם סמלי בלוקים, ולאחר מכן צור קישור מכל בלוק לגיליון תחתון שמכיל את המעגל המפורט.

- הפניות צולבות : השתמש בתכונות תוכנה לקישור רכיבים בין דיאגרמות רב-דף ודא שכל החיבורים הושלמו.

הוסף מידע על רכיב

העשרה את הדיאגרמה עם נתונים ניתנים לפעולה לייצור, רכש וTroubleshooting:

- מספרי זיהוי של רכיבים : הקצה תיוגים תקניים לפי IEEE (לפי 4.10) באופן עקבי. הסר כפילויות או תיוגים דו-משמעיים.

-

ערכים ודרוגים של רכיבים : ציין פרמטרים מדויקים:

- נגדים: ערך (10kΩ), סובלנות (±1%), דירוג הספק (0.25W), אריזה (0402).

- קבלים: ערך (10µF), דירוג מתח (16V), דיאלקטריק (X5R), אריזה (0603).

- רכיבים משולבים (ICs): מספר חלק (STM32F407VG), תצורת פינים (DIP-40), וمواصفות עיקריות (32-ביט ARM Cortex-M4).

- נתוני יצרן וטביעת רגל : כלול מספרי חלקים של היצרן (MPNs), קישורים לגיליונות נתונים, וסימוני טביעות PCB.

- הערות שוליים : הוסף הערות לדרישות מיוחדות.

- מידע זה מבטיח שהדיאגרמה היא "ניתנת לייצור" ומצמצם שגיאות במהלך אספקת רכיבים והרכבה.

ביצוע בדיקת חוקי חשמל (ERC)

בדיקת ERC היא שלב אימות אוטומטי לזיהוי שגיאות ברמת הסכמה לפני מעבר לレイ아אוט. עקוב אחר התהליך הבא:

- הגדרת כללי ERC : הגדר כללי תוכנה ספציפיים בהתאם לדרישות העיצוב שלך.

- הרץ ERC : בצע את הבדיקה וצור דוח המפרט את ההפרות.

-

פתרון הפרות :

- שגיאות חמורות: יש לטפל באופן מיידי.

- אזהרות: יש לבדוק ולפתור אם יש השפעה.

- מידע: יש לתעד לצורך הפניה עתידית.

- הפעל מחדש את ERC : חזור על הפעולה עד שauc לא תשארו שגיאות חמורות. בעבור עיצובים מורכבים, בצע סקירה ידנית במקביל ל-ERC כדי לאתר מקרי קצה.

צור את רשימת החיבורים (Netlist)

רשימה רשתית היא קובץ מבוסס טקסט המגדיר את כל הרכיבים, הסיכות שלהן והרשתות שמחברות ביניהם – ובכך משמשת כגשר בין תרשים למערך. שלבים עיקריים:

- בחר פורמט רשימת חיבורים (Netlist) : בחרו פורמט שמשתלב עם תוכנת ערכת ה-PCB.

- יצירת רשימת רשתות : השתמשו בתוכנת CAD לייצוא רשימת הרשתות—ודאו שכל הרכיבים, הערכים והחיבורים כלולים.

-

אימות דיוק רשימת הרשתות :

- השוו מדגם של רכיבים ורשתות לתרשים כדי לאשר שאין חיבורים חסרים או שגויים.

- ודאו שמספרי הפניות, מספרי החלקים והתקעים תואמים את התרשים.

- תיקון שגיאות בקבוצת הרשתות : תקנו בעיות כגון "רכיב לא מוגדר" או "שם רשת לא חוקי" לפני הייבוא לתוכנת היערכות.

- קבוצת רשתות נקייה ומדויקת היא קריטית כדי להימנע משגיאות בעריכה ולצמצם את הצורך בשדרוגי PCB.

מעבר לעריכת PCB

השלב האחרון בעיצוב תרשימי הוא ההכנה למסירה - הבטחת מעבר חלק לצוות עיצוב ה-PCB. פעולות עיקריות:

- אריזת מסמכים תרשימיים : אספו את התרשים הסופי (כל העמודים), דוח ERC, רשימת רשתות, BOM (לפי 4.17), והערות עיצוב לתיקיית פרויקט.

- העברת אילוצי עיצוב : שיתוף דרישות קריטיות עם צוות ההלayout.

- הסכמה על כללי עיצוב : אימות כללי עיצוב הלAYOUT על סמך האילוצים מהתרשים.

- מסירה ושיתוף פעולה : השתמשו בכלים של בקרת גרסאות כדי לשתף קבצים והקימו לולאת משוב - ענו במהירות על שאלות שמתמקדות בעיצוב.

- צוות ההלayout ישתמש ברשימת הרשתות כדי למקם רכיבים ולשרטט עקارات, תוך ייחוס לתרשים כדי להבטיח התאמה למטרת העיצוב.

איך לקרוא תרשימי לוחות מעגלים

קריאת תרשים של PCB מחייבת הבנה של שפתו הוויזואלית, המבנה הלוגי והאלמנטים המרכזיים שלו. להלן מדריך צעד אחר צעד למעקב אחרי מסלולים ופענוח רכיבים לצורך הרכבה, אבחון תקלות והנדסת הפוך.

מעקב אחרי מסלולי חשמל, ארקור וסיגנלים

תרשימים מאורגנים סביב שלושה סוגי מסלולים מרכזיים — שלטו בהם כדי לנווט בכל עיצוב:

מעקב אחרי מסלולי חשמל

מסלולי חשמל מספקים אנרגיה לכל הרכיבים — התחלו כאן כדי להבין את "דם החיים" של המעגל:

- זיהוי מקורות חשמל : מצאו את רכיב קלט החשמל.

- עקבו אחר יישור מתח : עקבו אחרי החשמל מהמקור למגברי מתח שממירים את מתח הקלט לרמות ישומיות. שימו לב לרכיבי הסינון שמפחיתים רעש.

- מיפוי הפצת חשמל : עקוב אחר רשתות חשמל ממונעות, חיישנים (U3) ו-LEDs (D1-D3).

- בדוק קondenסاتור התנתקות : חפש קondenסاتורים בערך קטן המחוברים בין רשתות חשמל לאדמה ליד מעגלים משולבים (ICs) – הם מיצבים מתח ומסננים רעשים עבור רכיבים בודדים.

עקבות מסלולי אדמה

אדמה (GND) היא נקודת התייחסות לכל האותות והחשמל – קריטית ליציבות המעגל:

- הכרה בסימני אדמה : תרשימי חיבורים משתמשים בסימנים סטנדרטיים:

- אדמה דיגיטלית: קו מוצק.

- אדמה אנלוגית: סימן משולש.

- מארץ של שילדה: סמל עם מישור אדמה.

- עקבו אחר חיבורי האדמה : ודאו שכל הרכיבים מחוברים למסלול אדמה. הסירו רכיבים 'צפים' – הם גורמים להתנהגות לא יציבה.

- הערה הפרדת אדמות : במעגלים משולבים אנלוגיים-דיגיטליים, רשתות האדמה האנלוגיות והדיגיטליות נפגשות לעתים קרובות בנקודה אחת כדי להפחית הפרעות הדדיות – עקבו אחר נקודת המפגש הזו כדי להבין את דרכי הפחתת הרעשים.

עקיבת מסלולים של אותות

מסלולי אותות מעבירים נתונים או אותות בקרה בין רכיבים – עקבו אחריהם כדי להבין את פעולת המעגל:

- עקבו אחר זרימת האות : עקבו אחר הרשת עד היעד – מחובר לפלטיה 6 של MCU להמרה אנלוגית-דיגיטלית. שימו לב לרכיבים הביניים.

- עקבו אחר אותות הבקרה : זיהוי אותות בקרה שמפעילים/מכבים רכיבים.

- ניווט בתרשימים מרובי עמודים : השתמשו בטבלת התוכן ובהפניות הצולבות כדי לעקוב אחר האותות בין העמודים.

פענוח סימוני התייחסות להרכבה ולトラブルשואוטינג

סימוני התייחסות הם ה"שמות" של הרכיבים – שליטתם היא מפתח לשימוש מעשי בתרשימים:

.prefices סטנדרטיים לסימוני התייחסות

: למדו בעל פה את ה-prefixes הסטנדרטיים של IEEE לזיהוי מהיר של סוגי רכיבים:

|

קידומת

|

סוג רכיב

|

דוגמה

|

פונקציה رئيسית

|

|

ר

|

מגננה

|

R5

|

מגביל זרם, מחלק מתח

|

|

ג

|

קונפסיטור

|

C8

|

מאחסן מטען, מסנן רעש

|

|

U

|

מעגל משולב (IC)

|

U3

|

MCU, voltage regulator, חיישן

|

|

G

|

דיודה

|

D2

|

חוסם זרם הפוך

|

|

ק

|

טרנזיסטור

|

שאלון 1

|

מגביר אותות, מחליף מעגלים

|

|

J

|

מחבר

|

J4

|

יציאת USB, כותרת חיישן

|

|

ל

|

מנוע

|

L3

|

מאחסן אנרגיה, מסנן אותות AC

|

|

SW

|

מֶתֶג

|

SW1

|

קלט משתמש (כפתור, מתג)

|

|

פ

|

פוז

|

פ1

|

מגן על המעגל מפני חשמל יתר

|

שימוש בדיסיגניטורים להרכבה

במהלך הרכבת PCB, הדיסיגניטורים ממפים רכיבים של דיאגרמה לפסיימנטים פיזיים על ה-PCB:

- מציאת רכיבים : בסכמה, מצא את הדיסיגניטור והוסף את ערכו (10kΩ) ואת החבילה.

- התאם ללוח PCB : על לוח ה-PCB הפיזי, מצא את התוויות הסילקסקرين "R10" ולחם את הנגד המתאים בגודל 10kΩ 0402.

- אמת התאמת BOM : השווה בין הסימונים ל-BOM כדי להבטיח אספקת רכיבים נכונה.

שימוש בסימונים לאיתור תקלות

סימונים מפשטים את אבחון תקלות במעגל:

- מצא רכיב פגום : אם חיישן לא עובד, מצא את הסימון שלו (U3) בסכמה ועקוב אחר מסלולי האנרגיה והארקה שלו – השתמש ברמ"ס כדי לבדוק אם יש מתח בדוק 1 של U3.

- אמת מסלולי אות : אם התקשורת נכשלת, עקוב אחר הרשת "UART_TX" מהדוק 7 של ה-MCU U2 לדוק 3 של המחבר J4 – בדוק קיומם של עקבות שבורות או ערכים שגויים של רכיבים.

- גיליונות נתונים להתייחסות צלבית : השתמש במספר חלק של המזהה (מה-BOM) כדי לגשת לגיליון הנתונים של הרכיב — ודא את חיבורי הפינים ביחס לתרשים הסכמתי.

טיפים מרכזיים לקריאת תרשימים סכמתיים מורכבים

- התחל מתרשים בלוקים : השתמש בתרשים הבלוקים ברמת עליונה כדי להתמצאות לפני שצוללים לתוך המעגלים המפורטים — זהה את המודול המרכזי ופנה החוצה.

- השתמש בהערות : הקפד להתייחס להערות המבהירות לוגיקה שאינה ברורה מאליה.

- קבץ רכיבים לפי פונקציה : קבץ בראשך רכיבים בעלי Präfix זהה של מזהה כדי להבין מערכיות משנה.

- תרגל עם תרשימים סכמתיים פשוטים : התחל עם מעגלים בסיסיים כדי לשלוט במעקב אחר מסלולים ובהכרת סימונים לפני שמתקדמים לעיצובים מורכבים.

ההבדל בין תרשים PCB לבין פריסה של PCB

טבלה השוואתית

|

היבט

|

תרשים

|

تخطيط

|

|

מטרה

|

חיבורים לוגיים

|

מימוש פיזי

|

|

תצוגה

|

מופשט/סימבולי

|

גאומטרי על PCB

|

|

מיקוד

|

פונקציה, זרימת אותות

|

מיקום, דרכי חיבור

|

|

מַדְרֵגָה

|

עיצוב ראשוני

|

עוקב אחר תרשים

|

|

פלט

|

רשימת חיבורים, רשימת חומרים

|

גרבר, קידור, הדפסת שילקסקرين

|

|

בדיקהוד

|

בדיקת עקיפות, בדיקת כללים

|

בדיקת כללים, בדיקות ייצור

|

|

תוצאהRESULT

|

בהירות העיצוב

|

מוכן לייצור

|

שלבים למעבר מתרשים לレイ아אוט

הגדרת תכולת הלוח ומבנה השכבות

הגדרת מידות לוח ה-PCB; בחירת מספר שכבות (2/4/6+) וחומר; הגדרת עובי נחושת ותכונות דיאלקטריות.

מיקום רכיבים

סידור לפי פונקציה, עדיפות לשימור אינטגריטי של אותות ויכולת ייצור; להבטיח גישה לבדיקה/הרכבה; להימנע מקיום שטחים חופפים.

ביצוע ריסון

ריסון באמצעות הנתיבים הקצרים והנקיים ביותר; עדיפות לספקי כוח/אדמה ולאותות מהירים; עמידה בהתאמת עכבות (50Ω/100Ω); מזעור חיבורים מוצלבים.

ביצוע בדיקת חוקי עיצוב

הרצת בדיקת חוקי עיצוב כדי לאמת רוחב/ריווח של עקבות, גודל חורים ודבקים וכללי ייצור; תיקון חריגים (קצר, בעיות ריווח) לפני סגירה.

הכנה קבצי ייצור

ייצוא קבצי Gerber, קבצי בור, BOM ותרשימי הרכבה; הבטחת תאימות לייצרני PCB.

תוכנות וכלים лучших לתרשימי PCB ב-2024

|

תוכנה

|

תכונות עיקריות

|

העוצמות

|

מקרי שימוש מומלצים

|

|

Altium Designer

|

תרשים/פריסה משולבת, תצוגה תלת-ממדית

|

חזק לעיצובים מורכבים, תקן תעשייתי

|

פרויקטים מקצועיים/בנפח גבוה, מעגלים בעלי מהירות גבוהה

|

|

OrCAD

|

סימולציה מתקדמת, שיתוף פעולה בצוות

|

אמין לתחום חלל תעופת/רכב, תמיכה באישורים

|

תעשיות/sectors מפוקחות

|

|

KiCad

|

קוד פתוח, פלטפורמה צולבת, ספריות סטנדרטיות

|

חינם, קהילה פעילה

|

חובבים, סטארט-אפים, קוד פתוח

|

|

Eagle

|

ידידותי למשתמש, אינטגרציה ענן

|

קליל, קל למתחילים

|

פסקי PCB פשוטים, פרויקטים חובביים

|

|

פרוטאוס

|

דיאגרמה + PCB + סימולציית SPICE

|

הכול-באחד לפיתוח גרסה ראשונית

|

חינוך, דמויות ראשוניות נמוכות מורכבות

|

|

EasyEDA

|

מבוסס웹, אין צורך בהתקנה, שיתופי

|

נגיש בכל מקום, עקומת למידה נמוכה

|

מתחילים, יצירה מהירה של דגמים ראשוניים

|

טיפים שימושיים לעיצוב דיאגרמות סכמטיות של שלדות PCB למתחילים

- התחילו ממעגלים פשוטים; תרגלו על ידי שיבוץ פרויקטים פתוחי מקור.

- תמיד בדקו גיליון נתונים של רכיבים לצורך זיהוי פינים, דירוגים והתאמת יסודות.

- השתמשו בשירותי אינטרנט: הדרכות ב-Youtube, פורומים (Reddit r/PrintedCircuitBoard).

סימנים נפוצים בדיאגרמות סכמטיות של שלדות מעגל

|

רכיב

|

סימן

|

תֵאוּר

|

|

מגננה

|

▭▬▭ / ▭▭▭

|

נגד קבוע (תקן IEEE)

|

|

קונפסיטור

|

⏚⏚

|

קבל ללא קוטב

|

|

דיודה

|

⚡▶

|

דיוד מישר

|

|

טרנזיסטור NPN

|

▲ עם 3 פינים

|

מפלט, בסיס, קולט

|

|

IC

|

▭ עם פינים

|

מעגל משולב (תג פינים במספרים)

|

|

כוח

|

VCC/+

|

מתח חיובי

|

|

קרקע

|

⏚

|

ארץ דיגיטלית/אנלוגית

|

רשימת בדיקה לתרשים PCB מושלם

- מספרי פינים/תוויות נכונות לכל הרכיבים

- ערכים מדויקים של רכיבים ומזהי הפניות

- חיבורים ברורים מחוץ לדף

- קבלים נפרדים מתאימים ורשימה מלאה של חומרים (BOM)

- אין פינים לא מחוברים או רשתות קצר

- תאימות לתקני IEEE/IPC

סיכום

עיצוב דיאגרמת PCB הוא מפתח לפיתוח PCB מהימן. הצלחה דורשת תכנון טכני, בחירה וחיבורים מדויקים של רכיבים והתחייבות לסטנדרטים – זה ממזער שגיאות ייצור, מקטין את עלויות העבודה מחדש ומבטיח שהמוצר הסופי יענה על הדרישות.

שאלות נפוצות

ש1: האם KiCad מתאים לעיצובי PCB מקצועיים?

ת1: כן – הוא תומך בעיצובים מורכבים רב-שכבות וייצוא קבצי ייצור, ושימוש בו נפוץ בקרב סטארט-אפים וחברות קטנות ובינוניות.

ש2: מה ההבדל בין ERC ל-DRC?

ת2: ERC בודק שגיאות בסכמה; DRC בודק הגבלות תAYOUT פיזי.

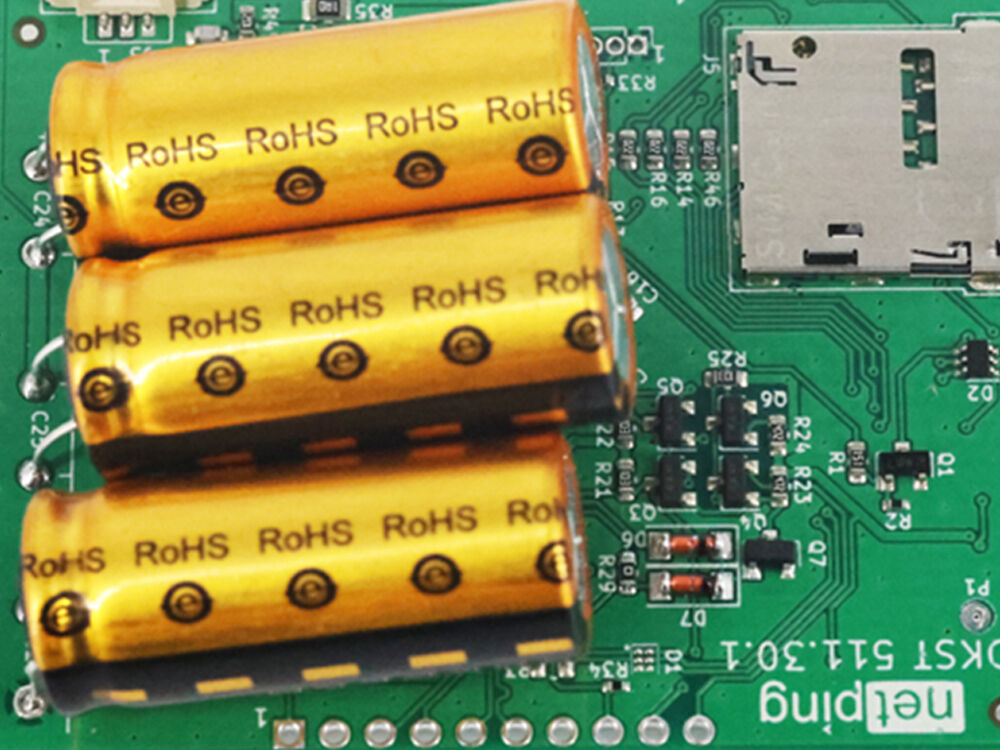

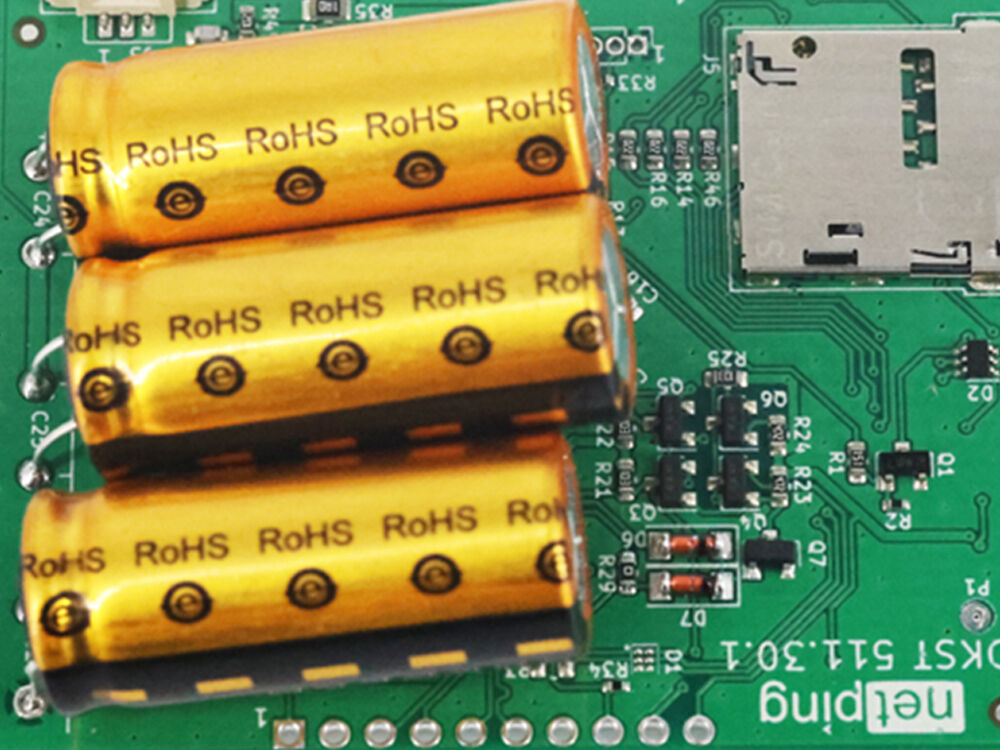

שאלה 3: למה צריך קondenסات השהייה?

תשובה 3: הם מיצבים את מתח הכוח של המיקרו-מעגל, מסננים רעשים ומונעים ירידות מתח עקב זרמים זמניים.

שאלה 4: כיצד בוחרים בין פסיבי 2 שכבות לפסיבי 4 שכבות?

תשובה 4: פסיבי 2 שכבות לدوائر פשוטים; פסיבי 4 שכבות לעיצובים מורכבים.

חדשות חמות

חדשות חמות